Лабораторная работа № 5. Арифметические схемы

Цели работы

1. Исследовать работу схем шифратора, дешифратора, мультиплексора, демультиплексора.

2. Исследовать работу схем полусумматора, сумматора, 4-разрядного сумматора.

3. Исследовать работу одноразрядного АЛУ и 4-разрядного АЛУ.

Теоретическая часть

Комбинационные схемы

Все цифровые схемы делятся на два вида – комбинационные и схемы памяти.

Комбинационная схема – схема, выход которой зависит только от входа в текущий момент времени, не зависит от предыдущего состояния и не имеет памяти.

Мультиплексор (multiplexer, MUX) – схема, обеспечивающая передачу информации, поступающей по нескольким входам на один выход. Выбор входной линии осуществляется при помощи адресных входов.

Если в мультиплексоре n адресных линий, то входов может быть 2n.

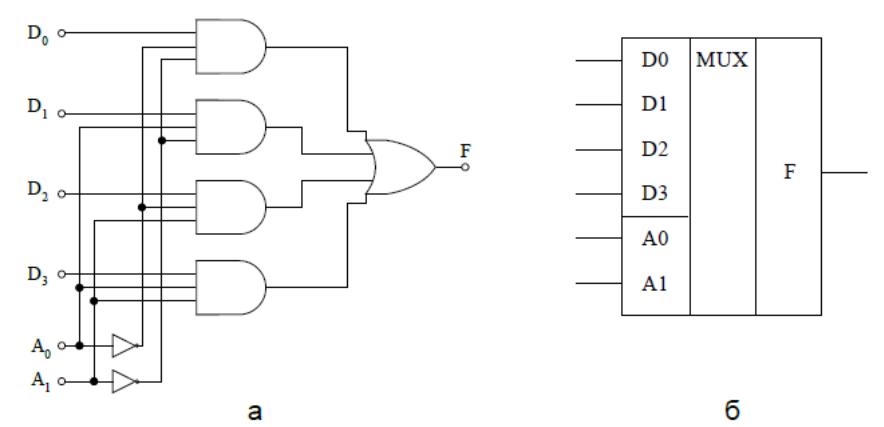

Рис. 1. 4-входовой мультиплексор:

а – реализация на вентилях; б – обозначение на схемах

Четыре вентиля И используются в этой схеме в качестве ключей (см. предыдущий параграф). Сигналы на двух нижних входах каждого вентиля И являются управляющими и определяют, будет ли проходить на выход сигнал данных с верхнего входа. Две адресные линии А0 и А1 кодируют 2-битное число (0..3), которое указывает, какая из четырех входных линий данных D0–D3 должна соединяться с выходом F. Каждый вентиль И запускается определенной комбинацией адресных входов.

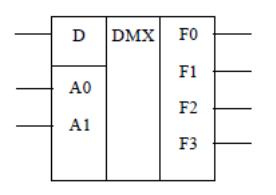

Демультиплексор (demultiplexer, DMX) – схема, обеспечивающая передачу информации, поступающей по одному входу на несколько выходов. Выбор выходной линии осуществляется при помощи адресных входов.

Рис. 2. Демультиплексор

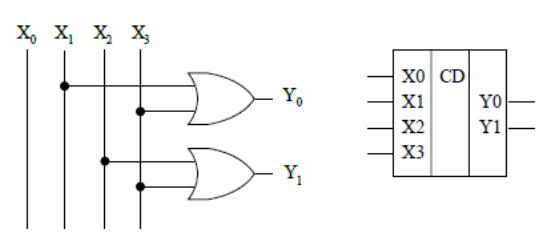

Шифратор (coder, CD) – преобразователь, в котором при подаче сигнала на один из входов на выходе появляется двоичный код этого входа.

Если в шифраторе n выходов, то он имеет 2n входов. Таблица истинности шифратора:

-

Входы

Y1

Y0

Х0

0

0

Х1

0

1

Х2

1

0

Х3

1

1

По таблице истинности можно вывести логические функции Y0 и Y1:

Y0 = X1 X3; Y1 = X2 X3

Рис. 4. Шифратор 4х2

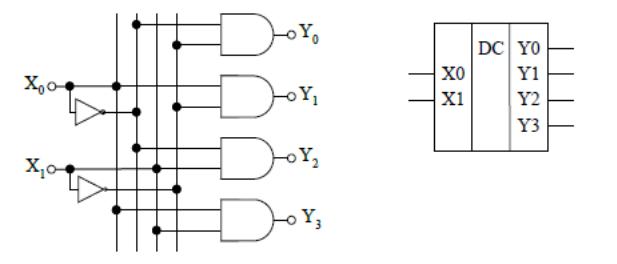

Дешифратор (decoder, DC) – преобразователь, в котором при подаче двоичного кода на вход на соответствующей выходной линии появляется сигнал.

Таблица истинности дешифратора:

-

Входы

Выходы

Х1

Х0

Y3

Y2

Y1

Y0

0

0

0

0

0

1

0

1

0

0

1

0

1

0

0

1

0

0

1

1

1

0

0

0

Логические функции имеют вид:

Рис. 5. Дешифратор 2х4