- •Міністерство освіти і науки україни Житомирський державний технологічний університет методичні вказівки

- •Правила роботи в лабораторії

- •Лабораторна робота №1 Дослідження функціональних можливостей цифрових мікросхем малої інтеграції

- •1.1. Навчальні питання

- •1.2. Навчальна мета

- •1.3. Теоретичні відомості

- •1.4. Опис лабораторної установки

- •1.5 Підготовка до роботи

- •1.6. Порядок виконання роботи

- •1.7. Обробка результатів

- •1.9. Контрольні тестові питання

- •Лабораторна робота №2 Дослідження принципів побудови та функціональних можливостей дешифраторів

- •2.1. Навчальні питання

- •2.2. Навчальна мета

- •2.3. Теоретичні відомості

- •2.4. Опис лабораторної установки

- •2.5. Підготовка до виконання роботи

- •2.6. Порядок виконання роботи

- •2.7. Обробка результатів

- •2.8. Контрольні тестові питання

- •Лабораторна робота №3 Дослідження принципів побудови та функціональних можливостей мультиплексорів

- •3.1. Навчальні питання

- •3.2. Навчальна мета

- •3.3. Теоретичні відомості

- •3.4. Опис лабораторної установки

- •3.5. Підготовка до виконання роботи

- •3.6. Порядок виконання роботи

- •3.7. Обробка результатів

- •3.9. Контрольні тестові питання

- •Лабораторна робота №4 Дослідження принципів побудови та функціональних можливостей тригерів

- •4.1. Навчальні питання

- •4.2. Навчальна мета

- •4.3. Теоретичні відомості

- •4.4. Опис лабораторної установки

- •4.5. Підготовка до виконання роботи

- •4.6. Порядок виконання роботи

- •4.7. Обробка результатів

- •4.9. Контрольні тестові питання.

- •Лабораторна робота №5 Дослідження принципів побудови та функціональних можливостей лічильників

- •5.1. Навчальні питання

- •5.2. Навчальна мета

- •5.3. Теоретичні відомості

- •5.4. Опис лабораторної установки

- •5.5. Підготовка до виконання роботи

- •5.6. Порядок виконання роботи.

- •5.7. Обробка результатів.

- •5.9. Контрольні тестові питання.

- •Для нотаток Література

4.7. Обробка результатів

1. За результатами п. 3 завдання визначити: аналітичну форму запису функціонування RS-тригера; функціональні типи входів та виходів тригера; заборонену комбінацію RS-тригера.

2. За результатами п. 4 визначити: правильність аналітичну форму запису функціонування D-тригера; функціональні типи входів та виходів тригера; наявність або відсутність забороненої комбінації D-тригера.

3. За результатами п. 5 визначити: пріорітетність входів керування RS- та D-тригерів; наявність заборонених комбінацій вхідних сигналів.

4. За результатами п. 6 визначити: аналітичну форму запису функціонування Т-тригера; функціональні типи входів та виходів тригера.

5. За результатами п.2.8 визначити: аналітичну форму запису алгоритму функціонування JK-тригера; заборонену комбінацію вхідних сигналів; функціональні типи входів та виходів JK-тригера.

6. За результатами п. 9 визначити: пріорітетність входів керування RS- та JK-тригерів; наявність заборонених комбінації вхідних сигналів.

7. За результатами п. 10 визначити: способи переводу JK-тригера в режими функціонування Т-, RS-, D-тригерів.

8. За результатами п. 11 визначити: принципи функціонування T-, D-, JK-тригерів у динамічному режимі.

3.9. Результати досліджень оформити у вигляді звіту, який підлягає індивідуальному захисту.

4.8. Зміст звіту. Звіт повинен містити:

1. Структурні схеми досліджуваних пристроїв.

2. Результати розрахунків.

3. Зробити висновки: про об’єм виконаної роботи, чи досягнена мета роботи, чи практичні результати співпали з теоретичними.

4.9. Контрольні тестові питання.

1. Яка пріорітетність входів керування JK-тригера?

2. Який вигляд має аналітична форма запису функціонування RS-тригера?

3. Який вигляд має аналітична форма запису функціонування JK-тригера?

4. Який вигляд має аналітична форма запису функціонування D-тригера?

5. Які є способи переводу JK-тригера в режими функціонування Т-тригера?

6. Які є способи переводу JK-тригера в режими функціонування RS-тригера?

7. Які є способи переводу JK-тригера в режими функціонування D-тригера?

8. Яка пріорітетність входів керування RS-тригера?

9. Який принцип одночасного функціонування JK-тригера та RS-тригера, що реалізовані в одній мікросхемі?

10. Яке застосування в цифровій техніці мають тригери?

Лабораторна робота №5 Дослідження принципів побудови та функціональних можливостей лічильників

5.1. Навчальні питання

1. Виконати дослідження принципів побудови та функціональних можливостей інтегрального лічильника ИЕ7 в режимах паралельного запису інформації, лічби в статиці, динаміці.

2. Виконати дослідження принципів побудови та функціональних можливостей інтегрального дільника частоти зі змінним коефіцієнтом ділення в усіх його режимах роботи.

3. Перевірити правильність отриманих даних та зняти часові діаграми роботи лічильника за допомогою осцилографа.

5.2. Навчальна мета

1. Експериментальне дослідження принципів побудови та функціональних можливостей інтегральних лічильників.

5.3. Теоретичні відомості

Рахунок числа імпульсів. Лічильниками називають пристрої, ведучі рахівниць числа імпульсів. Їх застосовують не тільки для рахунку, але і для виконання інших операцій, які можна звести до рахунку імпульсів.

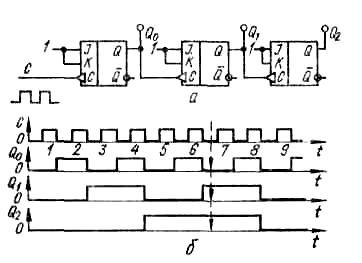

Рис. 5.1 Умовне позначення (а) і часова діаграма (б) лічильного тригера

Основним елементом лічильників є синхронний Т-тригер, використовуваний для роботи в рахунковому режимі. На практиці Т-тригери отримують з D- або JK-тригерів, що включаються так, як показано на рис. 5.1.

Т-тригер ділить на два частоту імпульсів, що поступають на синхронізуючий вхід (рис. 5.1). Каскадне включення п таких тригерів утворює лічильник з коефіцієнтом перерахунку 2n (з урахуванням нульового стану), тобто схему, яка при подачі Т імпульсів повертається до початкового стану. Такі схеми називають схемами рахунку по модулю 2п.

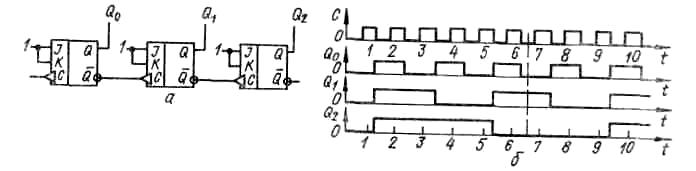

Рис. 5.2. Схема (а) і часові діаграми (б) двійкового послідовного лічильника, що підсумовує

На рис. 5.2, а зображений простий спосіб включення тригерів, що реалізовує послідовний лічильник, що підсумовує. Показаний трьох розрядний лічильник з коефіцієнтом перерахунку 23 = 8. Отже, після подачі на вхід восьми імпульсів лічильник повернеться до початкового стану. Говоритимемо, що подача на вхід лічильника числа імпульсів, Т, що перевищує, 24 - 1 (у даному прикладі 7 імпульсів), викликає переповнювання лічильника.

Можливий і інший варіант послідовного включення тригерів, коли їх входи сполучені з інверсними виходами попередніх тригерів, як показано на рис. 5.3. Таким чином отримують двійковий віднімаючий лічильник.

Рис. 5.3. Схема (а) і часові діаграми (б) двійкового послідовного віднімаючого лічильника

Якщо як початковий стан лічильника вибрати десяткове число 7 (двійковий код 111), то послідовність вхідних імпульсів зменшує вміст лічильника аж до 000, після чого наступає переповнювання, тобто повернення до початкового стану 111.

Якщо як початковий стан лічильника прийняти число 000, то стани виходів тригерів лічильника відображають від’ємне число злічених імпульсів, представлене в додатковому коді.

Послідовні і паралельні лічильники. На рис. 5.1, а і 5.2, а показані схеми двійкових послідовних лічильників, тобто таких лічильників, в яких при зміні стану певного тригера збуджується подальший тригер, причому тригери міняють свої стани не одночасно, а послідовно.

Якщо в даній ситуації повинні змінити свої стани п тригерів, то для завершення цього процесу буде потрібно п інтервалів часу, відповідних часу зміни стану кожного з тригерів. Такий послідовний характер роботи є причиною двох недоліків послідовного лічильника: менша швидкість рахунку в порівнянні з паралельними лічильниками і можливість появи помилкових сигналів на виході схеми. У паралельних лічильниках синхронізуючі сигнали поступають на всі тригери одночасно.

Допустима швидкість рахунку в лічильниках обох типів визначається максимальною швидкістю перекидання одного тригера.

Визначаючи максимальну швидкість рахунку послідовного лічильника, слід враховувати найбільш несприятливий випадок зміни стану всіх т тригерів. Сумарну тривалість перехідного процесу можна визначити як суму часів запізнювання окремих елементів, що сполучають тригери, і часів спрацьовування всіх тригерів. Знайдений таким чином максимальний час переходу лічильника з одного стану в інше слід вважати граничним. Звичайний реальний час переходу менше граничного, оскільки у ряді послідовних включених тригерів даний тригер починає перехід з одного стану в інше ще до закінчення перехідного процесу в збудливому його елементі.

Послідовний характер переходів тригерів лічильника є джерелом помилкових сигналів на його виходах. Наприклад, в лічильнику, ведучому рахівниць в чотирьох розрядному двійковому коді з «вагами» 8421, при переході від числа

710 = 01112 до числа 810 = 10002 на виході з'явиться наступна послідовність сигналів:

0111→0110→0100→0000→1000.

Це означає, що при переході із стану 7 в стан 8 на виходах лічильника на короткий час з'являться стани 6; 4; 0. Ці додаткові стани можуть викликати неправильну роботу інших пристроїв. З метою зменшення часу протікання перехідних процесів схему, показану на рис. 5.2, а, можна реалізувати у варіанті з подачею вхідних імпульсів одночасно на всі тригери.

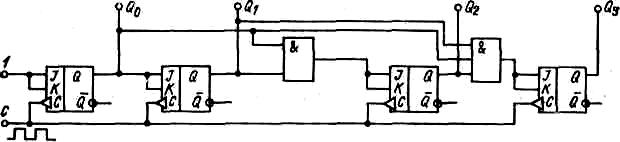

Рис. 5.4. Схема двійкового паралельного лічильника, що підсумовує

У цьому випадку отримаємо паралельний лічильник, що підсумовує. Приклад такої схеми даний на рис. 5.4. Тут на інформаційні входи тригерів подаються сигнали, що є логічною функцією стану лічильника і визначальні конкретні тригери, які змінюють свій стан при даному вхідному імпульсі. Принцип стробування імпульсу на вході даного тригера для розглянутого тут способу рахунку в прямому двійковому коді виходить з тимчасової діаграми на рис. 5.2, б. Він зводиться до наступного: тригер міняє свій стан під час вступу чергового імпульсу синхронізації, якщо всі попередні тригери знаходилися в стані логічної одиниці. Звідси і випливає схема паралельного лічильника, що підсумовує, показана на рис. 5.4.

Паралельні лічильники мають вищу швидкодію у порівнянні з послідовними, оскільки синхронізуючі імпульси поступають на всі тригери одночасно.

Реверсивні лічильники. Разом з розглянутими вище лічильниками, ведучими рахівниць лише в одному напрямі (лічильники, що підсумовують і віднімаючі), застосовують реверсивні (зворотні) лічильники, що дозволяють підсумовувати або віднімати вхідні імпульси залежно від значення сигналу керування.

Реверсивні лічильники в даний час випускаються у вигляді окремих ІМС. Так, ІМС типу 155ИЕ7 є реверсивним чотирьох розрядним двійковим лічильником.

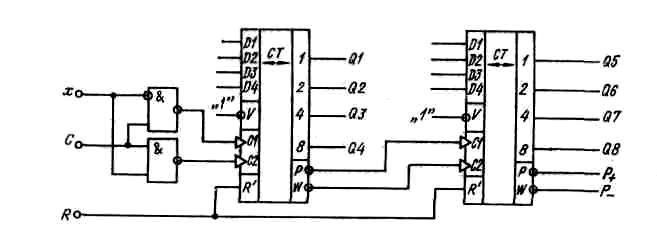

Рис. 5.5. Схема двійкового восьми розрядного реверсивного лічильника на ІМС типу 155ИЕ7

На рис. 5.5 показана схема реверсивного восьми розрядного двійкового лічильника, побудованого на основі двох ІМС типу 155ИЕ7. Розряд Q8 є знаковим. Рахунок ведеться в додаткових кодах. Кожна ІМС має по два рахункові входи С1 і С2, що забезпечують відповідно роботу в режимі підсумовування і віднімання. Зміна стану лічильника відбувається у момент надходження переднього фронту імпульсу на вхід С1 або С2. Якщо лічильник працює в режимі підсумовування, то змінюється сигнал на вході С1. Сигнал на вході С2 при цьому повинен мати високий логічний рівень. При роботі в режимі віднімання змінюється сигнал на вході С2, а вхід С1 знаходиться в стані логічної одиниці.

Інтегральна мікросхема типу 155ИЕ7 має два виходи переповнювання: вихід Р (перенесення при рахунку в позитивному напрямі) і вихід W (позики при рахунку в негативному напрямі). Сигнали перенесення Р і позики W формуються таким чином.

На виході перенесення Р негативний спад імпульсу утворюється при переповнюванні лічильника, тобто при появі на виходах Ql-Q4 максимального числа і умові, що тактуючий сигнал, поданий на вхід С1, має нульовий логічний стан. На виході позики W імпульс формується при появі на виходах всіх розрядів Q1-Q4 сигналу нульового логічного рівня. При цьому вхід С2 повинен знаходитися в стані логічного нуля. ІМС типу 155ИЕ7 має додаткові входи Dl-D4, по яких можливий паралельний запис чотирьох розрядних кодів за умови, що на входи V і R' подані сигнали нульового логічного рівня.

При каскадному з'єднанні декілька ІМС сигнали Р я W з виходів попередньої ІМС безпосередньо поступають на входи С1 і С2 подальшій ІМС, як показано на рис. 5.5. У даному восьмирозрядному реверсивному лічильнику рахунок здійснюється при кожному спаді тактуючого імпульсу C (X = 0 - підсумовування, X = 1 - віднімання).

Установка лічильника в нульовий стан проводиться подачею сигналу високого логічного рівня на входи R' обидві ІМС.

Аналогічно може виконуватися двійково-десятковий лічильник із застосуванням ІМС типу 155ИЕ6. Наявність у ІМС типів 155ИЕ6 і 155ИЕ7 входів паралельного запису коду дозволяє використовувати їх в режимі програмованих лічильників.