- •О.И. Елисеева, б.Б. Михайлов микропроцессоры.

- •Основные правила по технике безопасности при работе в лаборатории

- •Изучение микро-эвм на базе комплекта к 580

- •Общие сведения.

- •Порядок проведения лабораторной работы.

- •Задание 2. Изучение порядка записи и выполнения простых программ.

- •Задание 3. Исследование процесса выполнения программы по командам.

- •Задание 4. Обнуление бита переноса

- •Список необходимых команд микропроцессора к580

- •Исследование микропроцессора серии к1801

- •1. Краткое описание микропроцессора к1801вм1

- •1.1. Основные технические характеристики.

- •1.2. Структура микропроцессора.

- •1.3 Система команд микропроцессора

- •Методы адресации процессора 1801

- •Порядок выполнения работы

- •Требования к отчету.

- •Список необходимых команд микропроцессора к1801вм1

- •Исследование микропроцессорного комплекта серии к1804 Краткие теоретические сведения.

- •Входные данные Выходные данные

- •Описание устройства «микротренажер мт 1804».

- •Режимы работы устройства «микротренажер мт 1804»

- •Разряды

- •Подготовка к работе и порядок её выполнения

- •5. Отчет

- •Исследование однокристального микропроцессора 1816ве51 Порядок проведения лабораторной работы .

- •Краткое описание лабораторного стенда умпк-51.

- •Задание 1. Изучить порядок обмена информацией и способы управления микроконтроллера.

- •1. Порядок включения контроллера.

- •2. Режим просмотра и изменения содержимого внешней памяти.

- •3. Вывод на дисплей содержимого программного счетчика.

- •4. Просмотр и изменение содержимого внутренней памяти данных.

- •5. Просмотр и изменение содержимого отдельных разрядов.

- •6. Просмотр и изменение содержимого внутренних регистров.

- •7. Порядок занесения команды (программы).

- •8. Запуск выполнения программы.

- •Задание 2: Изучить порядок выполнения команд и программ.

- •. Система команд микроконтроллера семейства 1816.

- •1. Общая характеристика.

- •2. Типы команд

- •3. Типы операндов

- •5. Oбозначения, используемые при описании команд.

- •6. Команды пересылки данных микроконтроллера 1816.

- •7. Команды арифметических операций 1816.

- •8. Команды логических операций микроконтроллера 1816.

- •9. Команды операций над битами микроконтроллера 1816.

- •10.Команды передачи управления микроконтроллера 1816.

- •Память данных (озу).

- •Регистры специальных функций.

- •Исследование однокристального микропроцессора к1810вм86 Краткое описание микропроцессора к1810вм86

- •Оглавление

Исследование однокристального микропроцессора к1810вм86 Краткое описание микропроцессора к1810вм86

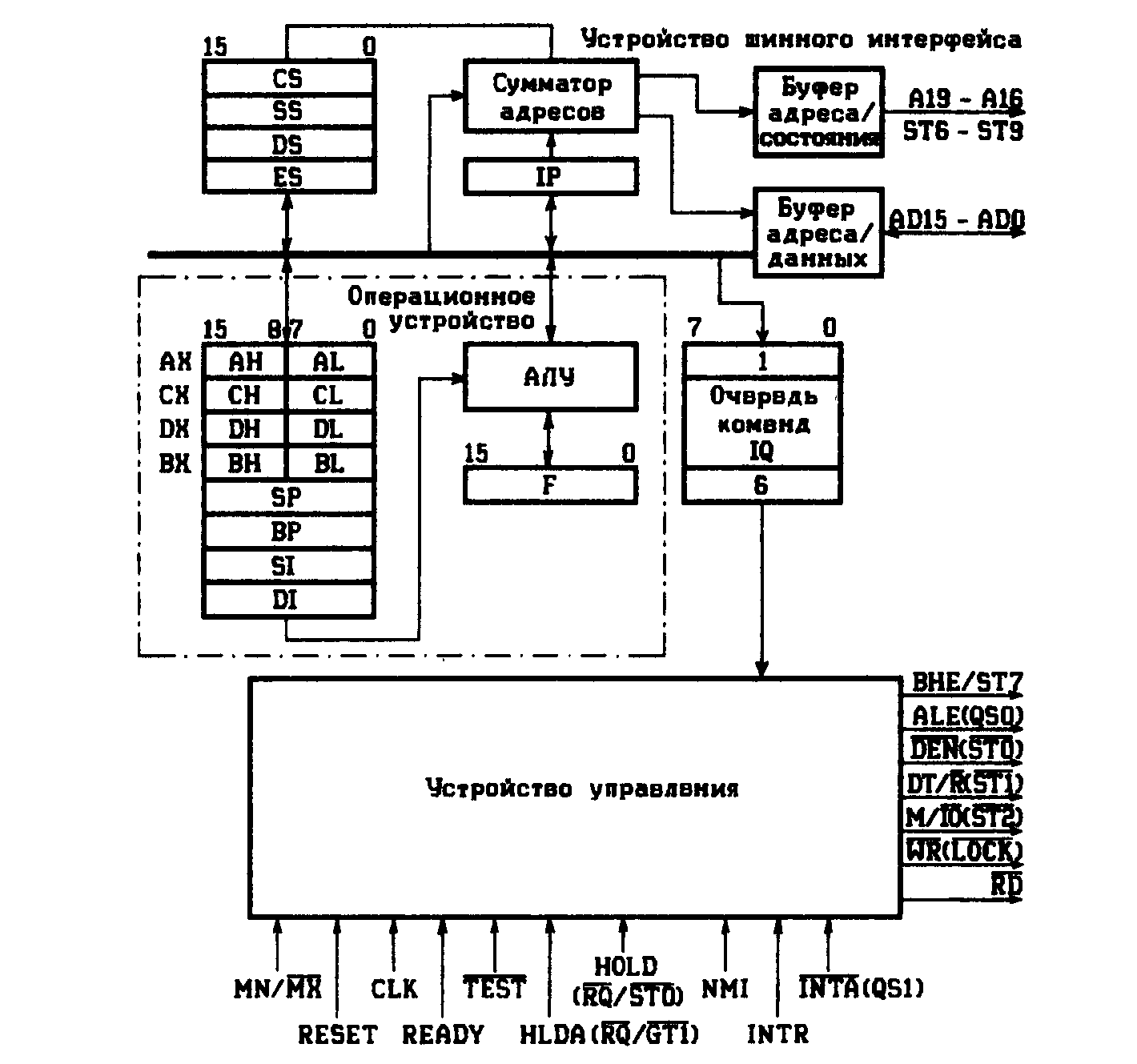

Микропроцессор имеет разрядность шины данных 16 бит, шины адреса 20 бит. Схема процессора представлена на рис.1:

Рис.1

В процессоре имеется восемь 16-разрядных регистров общего назначения:

AX – аккумулятор,

BX – базовый регистр,

CX – счетчик,

DX – регистр данных,

SP – указатель стека,

BP – указатель базы,

SI – индекс источника,

DI – индекс приемника.

Обычно регистры AX, BX, CX и DX используются для хранения данных, регистры SP, BP, SI, DI - для адресной информации. Для регистров AX, BX, CX, DX возможно также раздельное использование младших и старших байтов (AH, AL, BH, BL, CH, CL, DH, DL).

Регистр SP (Stack Pointer) представляет собой указатель стека (содержит текущее значение вершины стека), регистр BP (Base Pointer) используется при некоторых специальных формах адресации данных. Регистры SI и DI применяются при работе с так называемыми строками - последовательностями байтов или слов. Регистр SI (Source Index) указывает на текущий обрабатываемый элемент исходной строки (строки-источника), а DI (Destination Index) - на элемент результирующей строки (строки-приёмника).

Регистр флагов F:

FH |

FL |

||||||||||||||

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

x |

x |

x |

x |

OF |

DF |

IF |

TF |

SF |

ZF |

x |

AF |

x |

PF |

x |

CF |

Арифметические флаги:

CF – флаг переноса, фиксирует значение переноса из старшего бита результата при сложении, либо заема при вычитании, а также значение выдвигаемого бита при сдвиге операнда

PF – флаг паритета, фиксирует четное число единиц в младшем байте результата

AF – флаг вспомогательного переноса, фиксирует перенос из младшей тетрады (используется при выполнении десятичной коррекции)

ZF – флаг нулевого результата

SF – флаг знака, равен старшему разряду результата при работе со знаковой арифметикой

OF – флаг переполнения

Флаги управления:

DF – флаг направления обработки цепочек команд: DF=0 – в сторону больших адресов, DF=1 – в сторону меньших.

IF – флаг разрешения прерываний: IF=0 прерывания запрещаются, IF=0 – разрешаются.

TF – флаг трассировки: TF=1 – пошаговый режим работы.

Блок сегментных регистров состоит из четырех 16-разрядных регистров CS, SS, DS, ES, которые хранят базовые адреса сегментов памяти: CS – сегмент команд, SS – сегмент стека, DS – сегмент данных, ES – дополнительный сегмент (обычно также используется для хранения данных).

Указатель команд IP хранит смещение следующей команды в текущем кодовом сегменте.

Организация памяти в процессоре

Память представляет собой набор последовательно расположенных байтов, каждый из которых имеет 20-разрядный адрес. Два смежных байта могут рассматриваться как 16-битное слово, адресом слова считается адрес младшего байта (он меньше, чем адрес старшего байта). Адресное пространство имеет емкость 1 Мбайт и разбито на сегменты емкостью 64 Кбайт, которые характеризуются базами. Начальные адреса четырех текущих сегментов записываются в сегментные регистры CS, SS, DS, ES; для перехода к другой области памяти достаточно сменить содержимое сегментного регистра.

Каждая ячейка памяти характеризуется логическим и физическим адресом. Физический адрес представляет собой 20-разрядное число, однозначно определяющее положение ячейки в памяти. Логический адрес ячейки состоит из двух 16-битовых значений: базы сегмента и смещения внутри сегмента относительно базы (определяет расстояние от начала сегмента до этой ячейки). Для пересчета логического адреса в физический база сегмента сдвигается влево на 4 бит и суммируется со смещением. Если при суммировании возникает бит переноса, он игнорируется; таким образом, после ячейки памяти с адресом FFFFF идет ячейка с адресом 00000, то есть возникает кольцевая организация памяти (она также присуща каждому сегменту в отдельности).

Обращение к памяти.

К каждому сегменту памяти обращение осуществляется отдельно. Прямая передача информации между сегментами невозможна, для этого необходимо использовать регистры общего назначения.

Для обращения к памяти используются 4 регистра: BX, SI, DI, BP, а также смещение, задаваемое непосредственной величиной: d8 – 8 бит или d16 – 16 бит. Комбинируя эти регистры и смещения внутри квадратных скобок [ ], можно задействовать любую ячейку памяти.

[BX + SI] [BX + DI] [BP + SI] [BP + DI] |

[SI] [DI] d16 [BX] |

[BX + SI + d8] [BX + DI + d8] [BP + SI + d8] [BP + DI + d8] |

[SI + d8] [DI + d8] [BP + d8] [BX + d8] |

[BX + SI + d16] [BX + DI + d16] [BP + SI + d16] [BP + DI + d16] |

[SI + d16] [DI + d16] [BP + d16] [BX + d16] |

Для примера примем DS=100, BX=30, SI=70. В этом случае адрес [BX+SI]+25 будет преобразован процессором в следующий физический адрес: 100*16+30+70+25=1725.

По умолчанию сегментный регистр DS используется всегда, кроме режимов с регистром BP, в этом случае используется сегментный регистр SS.

Адреса задаются в шестнадцатеричном коде.

Структура команд процессора

Двухоперандные команды:

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

Код операции |

d |

s |

md |

reg |

r/m |

||||||||||

disp L |

disp H |

||||||||||||||

Бит d указывает направление передачи: d=1 – передача операнда или результата операции в регистр, указанный в поле reg, d=0 – передеча из регистра reg. Бит s показывает формат данных: s=1 – слово, s=0 - байт

Поле reg определяет второй операнд, обязательно находящийся в регистре; поле r/m (регистр/память) определяет первый операнд, который может находиться в регистре или памяти.

reg, r/m |

s=0 |

s=1 |

reg, r/m |

s=0 |

s=1 |

000 |

AL |

AX |

100 |

AH |

SP |

001 |

CL |

CX |

101 |

CH |

BP |

010 |

DL |

DX |

110 |

DH |

SI |

011 |

BL |

BX |

111 |

BH |

DI |

Поле md показывает, содержится первый операнд в памяти или в регистре, а в случае расположения операнда в памяти определяет вариант использования смещения disp, которе может находиться в третьем и четвертом байтах команды:

md=00 – операнд содержится в памяти, disp=0 (смещение отсутствует)

md=01 – операнд содержится в памяти, disp=disp L (команда содержит 8-битовое смещение, которое расширяется со знаком до 16 бит)

md=10 – операнд содержится в памяти, disp=disp H, disp L (команда содержит 16-битовое смещение)

md=11 – операнд содержится в регистре

Однооперандные команды:

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

Код операции |

s |

md |

Код операции |

r/m |

|||||||||||

disp L |

disp H |

||||||||||||||

Могут содержать от 2хдо 4х байт в зависимости от s и md

Команды с непосредственной адресацией:

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

Код операции |

s |

w |

md |

Код операции |

r/m |

||||||||||

disp L |

disp H |

||||||||||||||

data L |

data H |

||||||||||||||

Могут содержать до 3х слов. Поля s и w показывают, как используются последние 2 байта команды:

s |

w |

|

x |

0 |

data=data L (8 разрядов) |

0 |

1 |

data=data H, dataL (16 разрядов) |

1 |

1 |

data=data L (расширение до 16-разрядного слова со знаком) |

Система команд процессора

Команды пересылки данных

MOV op1, op2 - переслать операнд op2 в op1

PUSH op - записать операнд op в стек

POP op - извлечь операнд op из стека

XCHG op1, op2 - поменять местами значения операндов op1 и op2

Основные арифметические команды

ADD op1, op2 - выполнить сложение вида op1 = op1 + op2

INC op - увеличить содержимое операнда op на единицу (op = op + 1)

SUB op1, op2 - выполнить вычитание вида op1 = op1 - op2

DEC op - уменьшить содержимое операнда op на единицу (op = op - 1)

CMP op1, op2 - выполнить сравнение операндов op1 и op2 (то есть вычислить разность (op1 - op2) и установить флаги в регистре F)

MUL op (op - байт) - выполнить умножение вида AX = AL * op

MUL op (op - слово) - выполнить умножение вида DXAX = AX * op

DIV op (op - байт) - деление AX /op ; частное - в AL, остаток - в AH

DIV op (op - слово) - деление DXAX /op; частное - в AX, остаток - в DX

Все арифметические команды влияют на содержимое регистра флагов F, однако после команд умножения и деления состояния флагов не определены (произвольны).

Команды сдвига данных:

SHL op - сдвиг операнда op (беззнаковое целое) на 1 разряд влево

SHR op - сдвиг операнда op (беззнаковое целое) на 1 разряд вправо

Команды управления ходом программы:

LOOP label - организация цикла со счётчиком в регистре CX. Команда производит вычитание единицы из этого регистра, и, если CX не равен нулю, выполняется переход на метку label. Эта метка размещается «выше» по программе, т.е. до команды LOOP.

JZ label - переход на метку label, если «ноль», т.е. если ZF=1

JNZ label - переход на метку label, если «не ноль», т.е. если ZF=0

Обе эти команды обычно употребляются в программе после команд CMP, SUB или DEC.

Методы адресации

. Регистровая адресация

Операнды могут располагаться в любых регистрах общего назначения и сегментных регистрах. В этом случае в тексте программы указывается название соответствующего регистра, например команда, копирующая в регистр AX содержимое регистра BX, записывается как

mov ax,bx

. Непосредственная адресация

Некоторые команды (все арифметические команды, кроме деления) позволяют указывать один из операндов непосредственно в тексте программы, например команда

mov ax,2 помещает в регистр AX число 2.

Прямая адресация

Если известен адрес операнда, располагающегося в памяти, можно использовать этот адрес. Если операнд — слово, находящееся в сегменте, на который указывает ES, со смещением от начала сегмента 0001, то команда

mov ax,es:[0001h]

поместит это слово в регистр AX. Если селектор сегмента данных находится в DS, имя сегментного регистра при прямой адресации можно не указывать, DS используется по умолчанию. Прямая адресация иногда называется адресацией по смещению.

Косвенная адресация

По аналогии с регистровыми и непосредственными операндами адрес операнда в памяти также можно не указывать непосредственно, а хранить в любом регистре. До 80386 для этого можно было использовать только BX, SI, DI и BP. Например, следующая команда помещает в регистр AX слово из ячейки памяти, селектор сегмента которой находится в DS, а смещение — в BX:

! mov ax,[bx]

Как и в случае прямой адресации, DS всегда используется по умолчанию. Но в реальных программах, если смещение берут из регистра BP, то в качестве сегментного регистра используется SS.

Адресация по базе со сдвигом

Теперь скомбинируем два предыдущих метода адресации: следующая

команда

mov ax,[bx]+2

помещает в регистр AX слово, находящееся в сегменте, указанном в DS, со смещением на 2 большим, чем число, находящееся в BX. Так как слово занимает ровно два байта, эта команда поместила в AX слово, непосредственно следующее за тем, которое есть в предыдущем примере. Такая форма адресации используется в тех случаях, когда в регистре находится адрес начала структуры данных, а доступ надо осуществить к какому-нибудь элементу этой структуры. Другое

важное применение адресации по базе со сдвигом — доступ из подпрограммы к параметрам, данным в стеке, используя регистр BP в качестве базы и номер параметра в качестве смещения.

До 80386 в качестве базового регистра можно было использовать только BX, BP, SI или DI и сдвиг мог быть только байтом или словом (со знаком). С помощью этого метода можно организовывать доступ к одномерным массивам байт: смещение соответствует адресу начала массива, а число в регистре — индексу того элемента массива, который надо обработать.

. Адресация по базе с индексированием

В этом методе адресации смещение операнда в памяти вычисляется как сумма чисел, содержащихся в двух регистрах, и смещения, если оно указано:

mov ax,[bx+si]+2

В регистр AX помещается слово из ячейки памяти со смещением, равным сумме чисел, содержащихся в BX и SI, и числа 2. Из шестнадцатибитных регистров так можно складывать только BX+SI, BX+DI, BP+SI и BP+DI. Так можно прочитать, например, число из двумерного массива: если задана таблица 10x10 байт, 2 — смещение ее начала от начала сегмента данных, BX = 20, а SI = 7, приведенная команда прочитает слово, состоящее из седьмого и восьмого байт третьей строки.

Описание эмулятора

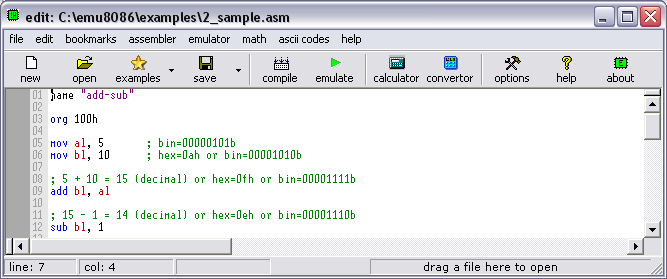

Для выполнения работы используется эмулятор процессора emu8086. Окно программы имеет следующий вид:

Рис.2

Текст программы набирается в поле редактора построчно. Комментарии записываются после знака «;».

Числа допускается записывать в любой системе счисления, при этом после числа ставится обозначение: h – шестнадцатеричное, b – двоичное, o – восьмеричное, например: 1ah, 101b, 71o. Числа без обозначения считаются десятичными. Если в записи шестнадцатеричного числа старшим разрядом является буква (A..F), то перед ней необходимо поставить «0».

Для создания циклов, условных и безусловных переходов используются команды LOOP, JMP, JA, JC и т.п. и метки вида:

label:

В конце программы рекомендуется ставить команду RET

Полный список и описание всех команд процессора можно найти в меню help: Documentation and tutorials/8086 Instruction Set.

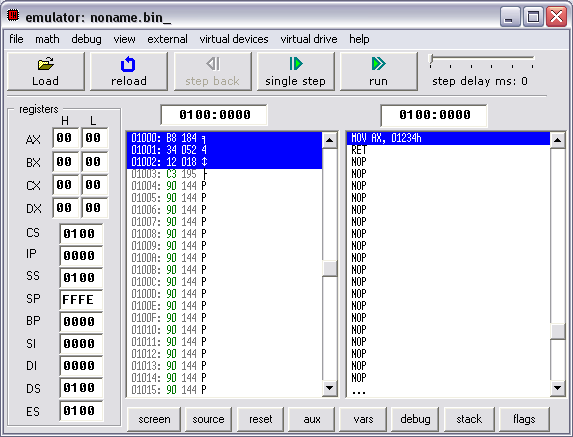

Для запуска набранной программы используется кнопка emulate на панели инструментов. При этом открывается окно эмулятора (рис.3):

Рис.3

В открывшемся окне эмулятора можно управлять режимом работы программы: кнопка single step позволяет использовать пошаговый режим, run – запустить программу на выполнение. В левой части окна выводятся значения всех регистров общего назначения, их можно просматривать и изменять по ходу выполнения программы; кроме того, двойной щелчок мыши по окошку со значением регистра позволяет вывести на экран окно расширенного просмотра значений регистров в различных кодировках. В центральной части окна эмулятора находятся номера и содержимое ячеек памяти (подсвечиваются ячейки, соответствующие следующей строке программы), в правой части – обработанный текст выполняемой программы. Содержимое регистра флагов можно просматривать и изменять с помощью кнопки flags в левом нижнем углу. При помощи регулятора step delay можно устанавливать задержку между выполнением шагов программы.

Порядок выполнения работы

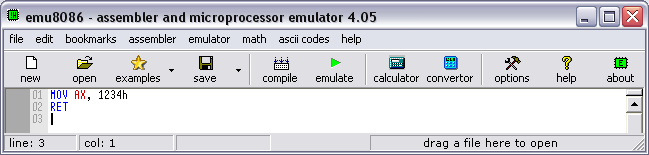

I.Ознакомьтесь с работой эмулятора:

запустите программу emu8086.exe

Рис.4

В окне приветствия (рис.4) выберите вариант new, далее (рис.5) выберите empty workspace.

Рис.5

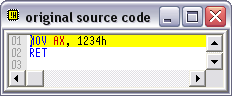

для примера напишите программу занесения числа 1234h в регистр AX:

Рис.6

запустите ее нажатием клавиши F5 или кнопки emulate на панели инструментов, откроются окна эмулятора (рис.3) и кода программы (рис.7):

Рис.7

запустите программу на выполнение в пошаговом режиме и проследите за изменением значения регистров AX и IP (содержимое изменившиеся при выполнении команды регистров выделяется синим цветом), затем перезагрузите программу нажатием кнопки reload и выполните ее с помощью кнопки run

просмотрите содержимое регистра флагов, нажав кнопку flags; измените значение флага паритета PF на 1

II. Напишите программы, выполняющие следующие действия:

1. Команда загрузки и пересылки данных (команда MOV)

загрузить регистр CX числом ABCDh

переслать содержимое CX в регистр AX

загрузить ячейку памяти текущего сегмента без смещения (смещение 0) числом FFh

задать в качестве базы сегмента DS=200h, предварительно записав это число в регистр DX; загрузить ячейку 02100h числом AAh (смещение 100h)

записать в регистр BX смещение 200h и загрузить ячейку 02200h числом BBh (смещение [BX])

записать в регистр SI индекс 20 и загрузить ячейку 02220h числом CCh, используя сегмент с базой DS=200h и смещение [BX+SI]

загрузить ячейку 02222h числом DDh, используя сегмент с базой DS=200h и смещение [BX+SI+2]

2. Однооперандные команды

загрузить регистр DX числом 5

увеличить содержимое регистра DX на единицу (команда INC)

перенести содержимое регистра DX в ячейку памяти 01100h

уменьшить содержимое ячейки 01100h на единицу (команда DEC)

инвертировать содержимое регистра DX (команда NOT)

3. Двухоперандные команды

а) Арифметические операции:

сложить числа 1Bh и 1Ch, используя регистры BX и CX, результат записать в CX (команда ADD)

вычесть из содержимого регистра CX константу 10b, результат записать в AX (команда SUB)

содержимое регистра AX разделить на 10h, предварительно записав делитель в регистр BX (команда DIV)

остаток от деления (находится в регистре DX) умножить на 2 (команда MUL)

б) Логические операции:

записать в ячейку памяти 01100h число 101101b, в регистр AX число 110001b, выполнить для них логическое умножение, результат записать в ячейку 01100h (команда AND)

записать в регистр AX число 111010b, выполнить логическое сложение между содержимым AX и ячейки памяти 01100h, результат записать в регистр AX (команда OR)

выполнить операцию сумма по модулю 2 для содержимого регистра AX и числа 001001b (команда XOR)

4. Команды сдвига

занести в регистр BX число 25h, умножить его на 2, используя операцию арифметического сдвига (команда SAL)

занести в ячейку памяти 01200h число 40h, разделить его на 4, используя операцию арифметического сдвига (команда SAR)

5. Команды управления программой

а) Цикл (команда LOOP)

занести в регистр CX число 10 (количество повторений цикла)

установить в качестве базы сегмента DS=0100h, занести в регистр BX смещение 0101h

установить метку начала выполнения цикла вида label:

тело цикла: занести число AAh в ячейку, смещение которой относительно базы DS указано в регистре BX, и увеличить содержимое BX на 1

после записи тела цикла перейти по метке label

После выполнения программы число AAh должно быть записано в ячейки с 01101h по 0110Ah

б) Условный переход (команда JC)

занести число FFh в регистр AL

увеличить содержимое регистра AL на AAh

если бит переноса не равен единице, записать в регистр BX число ABCDh, иначе завершить программу (переход по метке к концу программы)

в) Безусловный переход (команда JMP)

занести в ячейку 01100h число С3h (код команды RET)

написать программу сложения чисел Ah и Bh, используя регистры DL и DH

для окончания выполнения программы перейти по адресу 01100h

Список необходимых команд микропроцессора К181ВМ86

Команда |

Операнды |

Описание |

Пример |

Регистр флагов |

||||||||||||

ADD |

REG, memory memory, REG REG, REG memory, immediate REG, immediate |

Сложение

Алгоритм: операнд 1=операнд1+операнд2 |

Сложение 5 и -3:

MOV AL, 5 ; AL = 5 ADD AL, -3 ; AL = 2 RET |

|

||||||||||||

AND |

REG, memory memory, REG REG, REG memory, immediate REG, immediate |

Логическое И, результат сохраняется в операнд1

Применяются правила: 1 AND 1 = 1 1 AND 0 = 0 0 AND 1 = 0 0 AND 0 = 0 |

Сложение по И чисел 1100001b и 11011111b:

MOV AL, 'a' ; AL = 01100001b AND AL, ; AL = 01000001b ('A') RET |

|

||||||||||||

DEC |

REG memory |

Декрементация

Алгоритм операнд=операнд-1 |

Уменьшение 255 на1:

MOV AL, 255 ; AL = 0FFh (255 or -1) DEC AL ; AL = 0FEh (254 or -2) RET |

|

||||||||||||

DIV |

REG memory |

Деление (без знака)

Алгоритм: 1)операнд - байт: AL=AX/операнд, AH = остаток 2)операнд – слово: AX=(DX AX)/операнд, DX =остаток |

Деление 203 на 4:

MOV AX, 203 ; AX = 00CBh MOV BL, 4 DIV BL ; AL = 50 (32h), AH = 3 RET |

|

||||||||||||

HLT |

- |

Прекращение выполнения программы |

MOV AX, 5 HLT |

|

||||||||||||

INC |

REG memory |

Инкрементация

Алгоритм: операнд=операнд+1 |

Увеличение 4 на 1:

MOV AL, 4 INC AL ; AL = 5 RET |

|

||||||||||||

JC |

Метка |

Короткий переход, если бит переноса равен 1.

Алгоритм: если CF = 1 то переход

|

Проверка наличия бита переноса:

include 'emu8086.inc' ORG 100h MOV AL, 255 ADD AL, 1 JC label1 PRINT 'no carry.' JMP exit label1: PRINT 'has carry.' exit: RET |

|

||||||||||||

JMP |

Метка 4-хбайтный адрес |

Безусловный переход (перемещение к другой части программы). 4-х байтный адрес может вводиться в виде: 1234h:5678h, первое значение – база сегмента, второе – смещение.

Алгоритм: переход по метке (всегда) |

Выполнить прыжок через 2 строки, напечатать “Got Here!”, если прыжок выполнен:

include 'emu8086.inc' ORG 100h MOV AL, 5 JMP label1 PRINT 'Not Jumped!' MOV AL, 0 label1: PRINT 'Got Here!' RET |

|

||||||||||||

LOOP |

метка |

Декрементация CX, переход к метке, если CX не равен нулю

Алгоритм: CX=CX -1 если CX <> 0 то переход иначе продолжить |

Напечатать “loop” 5 раз:

include 'emu8086.inc' ORG 100h MOV CX, 5 label1: PRINTN 'loop!' LOOP label1 RET |

|

||||||||||||

MOV |

REG, memory memory, REG REG, REG memory, immediate REG, immediate

SREG, memory memory, SREG REG, SREG SREG, REG |

Копирование операнда2 в операнд1

Команда MOV не может: 1.устанавливать значение регистров CS и IP. 2.копировать значение одного сегментного регистра в другой сегментный регистр (необходимо сначала скопировать в регистр общего назначения). 3.копировать непосредственное значение в сегментный регистр

Алгоритм: операнд1=операнд2 |

Занесение числа ABh в регистр AL, пересылка его в ячейку памяти с адресом 01101h:

MOV AL, 0ABh MOV BX, 0100h MOV DS, BX MOV [BX+1], AX RET |

|

||||||||||||

MUL |

REG memory |

Умножение (без знака)

Алгоритм: 1)операнд - байт: AX = AL * операнд 2)операнд - слово: (DX AX) = AX*операнд |

Умножение 200 на 4:

MOV AL, 200 MOV BL, 4 MUL BL ; AX = 0320h (800) RET |

CF=OF=0, если старший бит результата равен нулю |

||||||||||||

NOP |

- |

Нет операции |

Ничего не делать 2 раза:

NOP NOP RET |

|

||||||||||||

NOT |

REG memory |

Инвертирует все биты операнда

Алгоритм: 1.если бит равен 1, то приравнять бит 0 2.если бит равен 0, то приравнять бит 1 |

Инвертировать число 11011b:

MOV AL, 00011011b NOT AL ; AL = 11100100b RET |

|

||||||||||||

OR |

REG, memory memory, REG REG, REG memory, immediate REG, immediate |

Логическое ИЛИ между всеми битами двух операндов. Результат сохраняется в первом операнде.

Применяются правила: 1 OR 1 = 1 1 OR 0 = 1 0 OR 1 = 1 0 OR 0 = 0 |

Сложение по ИЛИ 1000001b и 100000b:

MOV AL, 'A' ; AL = 01000001b OR AL, 00100000b ; AL = 01100001b ('a') RET |

|

||||||||||||

RET |

- immediate |

Возврат из процедуры

Алгоритм: 1.вытолкнуть из стека: IP 2.если операнд – константа: SP=SP+operand |

Вызов процедуры занесения числа 1234h в регистр AX, увеличение его на 1

ORG 100h ; for com file CALL p1 ADD AX, 1 RET p1 PROC MOV AX, 1234h RET p1 ENDP |

|

||||||||||||

SAL |

memory, immediate REG, immediate memory, CL REG, CL |

Арифметический сдвиг операнда 1 влево. Число сдвигов устанавливается операндом 2 (константа либо значение регистра CL)

Алгоритм: 1.Сдвиг всех бит влево, старший бит записывается в CF. 2.В качестве младшего бита записывается 0. |

Сдвиг числа E0 влево 1 раз:

MOV AL, 0E0h ; AL = 11100000b MOV CL, 1 SAL AL, CL ; AL = 11000000b, CF=1. RET |

OF=0 если знак операнда1 сохраняется. |

||||||||||||

SAR |

memory, immediate REG, immediate memory, CL REG, CL |

Арифметический сдвиг операнда1 вправо. Число сдвигов устанавливается операндом2 (константа либо значение регистра CL)

Алгоритм: 1.Сдвиг всех бит вправо, младший бит заносится в CF. 2.Старший бит (бит знака) устанавливается в то же значение, что было раньше. |

Сдвиг числа E0 вправо 2 раза (бит знака равен 1):

MOV AL, 0E0h ; AL = 11100000b SAR AL, 2 ; AL = 11111000b, CF=0. RET

Сдвиг числа 4C вправо 1 раз (бит знака равен 0):

MOV BL, 4Ch ; BL = 01001100b SAR BL, 1 ; BL = 00100110b, CF=0 RET |

OF=0 если знак операнда1 сохраняется. |

||||||||||||

SUB |

REG, memory memory, REG REG, REG memory, immediate REG, immediate |

Вычитание

Алгоритм: операнд1=операнд1-операнд2 |

Вычитание 2 из 5:

MOV AL, 5 SUB AL, 2 ; AL = 3 RET

|

|

||||||||||||

XOR |

REG, memory memory, REG REG, REG memory, immediate REG, immediate |

Сумма по модулю 2 (исключающее ИЛИ) между всеми битами двух операндов. Результат сохраняется в первом операнде.

Применяются правила: 1 XOR 1 = 0 1 XOR 0 = 1 0 XOR 1 = 1 0 XOR 0 = 0 |

Сумма по модулю два чисел 111b и 10b:

MOV AL, 00000111b XOR AL, 00000010b ; AL = 00000101b RET

|

|

Примечания

REG – регистр общего назначения: AX, BX, CX, DX, AH, AL, BL, BH, CH, CL, DH, DL, DI, SI, BP, SP

SREG – сегментный регистр: DS, ES, SS, только в качестве второго операнда - CS

Memory – ячейка памяти: [BX], [BX+SI+7], var, etc...

Immediate – непосредственный ввод значения.

В описании регистра флагов:

1 – флаг устанавливается в 1

0 – флаг устанавливается в 0

r – значение флага зависит от результата операции

? – значение флага не определено

- - значение флага не изменяется