- •1.Определение ос. Ос как виртуальная машина и как диспетчер аппаратных и прораммных ресурсов.

- •2.Назначение и основные функции ос. Классификация ос. Варианты классификации.

- •5.Многопроцессорные ос. Симметричная и несимметричная параллельная обработка.

- •3.Эволюция ос. Современные ос, их характеристики и области применения.

- •4.Однозадачные и многозадачные ос. Преимущества многозадачности и ее реализация в ос.

- •Сетевые компоненты ос.

- •Оc с разделением времени. Основные свойства, классы решаемых задач. Примеры современных реализаций.

- •Ос реального времени. Жесткие и нежесткие системы. Интерфейс с внешней средой.

- •Операционные системы unix. Основные линии развития (at&t и bsd unix). Современные реализации для пэвм.

- •Операционные системы Microsoft Windows. Основные версии и реализации, их характеристики и свойства.

- •Современные типы ос для пэвм. Назначение, характеристики и свойства.

- •Функциональная организация (структура) типовой многозадачной ос. Базовые функциональные подсистемы. Ядро и пользовательский слой ос.

- •Архитектурные принципы (принципы разработки и организации) современной мультипрограммной ос. Модульная структура ос.

- •Подсистема планирования (управления) процессов и потоков в ос. Понятие процесса, потока и ресурса. Типы ресурсов. Информационные структуры процесса (потока).

- •Жизненный цикл процесса. Диаграмма состояний. Переходы между состояниями. Диаграмма состояний потоков в ос ms Windows (2000/xp).

- •16. Алгоритмы планирования. Квантование времени (вытеснение). Планирование на основе приоритетов. Приоритетное планирование потоков в ms Windows (2000/xp).

- •Организация взаимодействия (синхронизация) параллельных процессов и потоков. Эффект гонок. Критическая секция. Типовые задачи синхронизации.

- •Системные механизмы для синхронизации потоков. Блокирующие переменные, мьютексы, семафоры.

- •Подсистема управления памятью. Основные функции. Сегментная и страничная программные модели памяти.

- •Концепция виртуальной памяти. Трансляция виртуальных адресов.

- •Иерархическая организация памяти эвм. Принцип кэширования. Устройство кэш-памяти (созу) на процессоре. Алгоритмы работы кэш-памяти.

- •Алгоритмы распределения основной памяти эвм.

- •Страничный обмен (замещение), как метод реализации виртуальной памяти. Таблицы страниц процесса. Свопинг процессов.

- •Структура виртуального адресного пространства процесса в ms Windows nt (2000/xp).

- •Архитектура (модель) ос ms Windows nt (2000/xp). Компоненты ядра и компоненты пользовательского режима. Файловое дерево ос ms Windows на загрузочном томе.

- •Порядок и основные процедуры для загрузки ос на аппаратной платформе ibm-совместимых пэвм. Мультисистемная организация, диспетчеры загрузки ос.

- •Подсистема ввода-вывода ос. Буферизация обмена данными между внешней и основной памятью. Дисковый (системный) кэш.

- •Управление устройствами (аппаратурой) в ос. Независимость программ от устройств. Типы устройств. Драйверная подсистема ос. Модель драйвера в ос Windows.

- •Файловая система ос (fs). Внешняя модель (архитектура) fs. Правила именования и пространства имен в ос Windows. Элементы полного имени. Типы файловых объектов и их атрибуты.

- •Внутренняя организация файловой системы (fs). Системные данные fs на томе. Типы файловых систем.

- •Множественность файловых систем (fs) современных ос. Файловые системы ос Windows: fat12, fet16, fat32, cdfs, ntfs (ntfs5), сетевые fs. Диспетчер файловых систем (ifs ), драйверы fs.

- •Файловая система faTхх. Назначение и организация таблицы распределения файлов. Типы записей в fat.

- •Структура элемента каталога в файловой системе faTхх. Опорные и дополнительные элементы. Метка тома.

- •Поддержка и внутренняя организация длинных имен в ос Windows для файловых систем faTxx. Псевдоним длинного имени в пространстве имен dos.

- •Система операций над файлами. Типы доступа к данным файла. Защита файлов и данных в ос. Обеспечение целостности fs. Восстанавливаемость после сбоев ос и аппаратуры.

- •Файловая система ntfs. Основные свойства и возможности. Обеспечение целостности и отказоустойчивости ntfs. Управление доступом к данным и защита данных в ntfs.

- •Внутренняя организация ntfs на логическом томе. Метафайлы и их назначение. Структура главной таблицы файлов (мfт).

- •Интерфейс прикладного программирования в ос. Библиотеки функций api, системные вызовы. Назначение и реализация в инструментальных системах (системах программирования).

- •Командный (консольный) интерфейс ос. Виртуальная машина ms-dos, интерпретатор команд и его функции. Синтаксис консольных команд. Система команд и их классификация.

- •Внутренние команды командного интерфейса ос. Формат вызова, механизм внутренней реализации. Примеры внутренних команд vdm.

- •Команды-фильтры. Конвейеризация (потоковое сцепление) команд в командном интерфейсе. Перенаправление стандартного ввода-вывода в файлы и другие устройства.

- •Конфигурационные, диагностические и информационные команды ос.

- •Среда окружения командного интерфейса и ее назначение. Команды формирования окружения. Системные переменные.

- •Система команд ос для операций с файлами. Команды для работы с каталогами.

- •Программирование в среде командного интерфейса. Пакетные командные файлы: - внутренние команды, передача параметров.

- •Графический интерфейс конечного пользователя (gui). Концепция рабочего стола. Стандартные элементы оформления и управления в gui. Способы запуска приложений.

- •Защита данных и программ в ос. Модель безопасности ос ms Windows (2000/xp). Механизм учетных записей пользователей, регистрация в системе. Права доступа.

- •Инструменты конфигурирования и настройки ос ms Windows (2000/xp). Панель управления. Системное администрирование.

- •Системная база данных ос ms Windows - реестр. Общая организация, типы параметров. Утилиты для работы с реестром. Экспорт и импорт данных реестра.

- •51. Развертывание (инсталляция) ос на аппаратной платформе. Дистрибутив ос. Утилиты для установки.

- •52. Поддержка сетей в ос ms Windows. Сетевые компоненты, конфигурирование стека сетевых протоколов. Сетевые утилиты ос. Прикладные пользовательские сетевые сервисы.

Концепция виртуальной памяти. Трансляция виртуальных адресов.

Суть концепции виртуальной памяти состоит в том, что виртуальное пространство, с которым имеет дело процесс (программа), отделяется от реальных адресов вычислительной системы. Диапазон виртуальных адресов, к которым может обращаться процесс, называется виртуальным адресным пространством этого процесса, а диапазон реальных адресов называется реальным адресным пространством компьютера. Множество виртуальных адресов, как правило, значительно превосходит диапазон адресов реальной памяти. Перевод виртуального адреса в реальный адрес во время выполнения процесса называется динамическим преобразованием адресов. Адреса, смежные в V (виртуальное пространство), необязательно будут смежными в R (реальное пространство). Таким образом, пользователь освобождается от необходимости учитывать размещение своих процедур и данных в реальной памяти. Только небольшая часть кода и данных каждого процесса размещается в оперативной памяти. Остальная часть хранится во внешней памяти (диск).

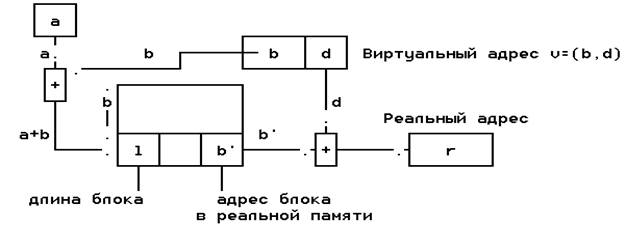

Системы виртуальной памяти требуют наличия таблиц отображения виртуального адреса в реальный. Главная задача разработчиков систем - это минимизация количества информации отображения при удовлетворительных скоростных характеристиках системы. Эта цель достигается поблочным отображением: информация группируется в блоки и система следит за тем, в каких местах реальной памяти размещаются различные блоки из виртуального пространства. Блоки фиксированного размера называются страницами; блоки переменного размера называются сегментами. В некоторых системах оба вида блоков комбинируются - применяются сегменты, состоящие из целых страниц. Адреса рассматриваются как упорядоченные пары

V=(b, d)

где b - номер блока с виртуальным адресом, d - смещение адреса относительно начала блока b. Таблица отображения блоков обычно хранится в кэш-памяти.

Преобразование виртуального адреса в реальный. Реальный адрес a таблицы загружается в специальный регистр начального адреса таблицы блоков. Таблица содержит по одной строке для каждого блока процесса, причем эти строки идут в порядке возрастания номеров (блок 0, блок 1, ...). Hомер блока суммируется с адресом а, образуя реальный адрес строки таблицы для блока b. Эта строка содержит реальный адрес b' блока в реальной памяти. К b' прибавляется смещение d и образуется реальный адрес r=b'+d.

Иерархическая организация памяти эвм. Принцип кэширования. Устройство кэш-памяти (созу) на процессоре. Алгоритмы работы кэш-памяти.

Иерархия запоминающих устройств. Принцип кэширования данных

Память вычислительной машины представляет собой иерархию запоминающих устройств (внутренние регистры процессора, различные типы сверхоперативной и оперативной памяти, диски, ленты), отличающихся средним временем доступа и стоимостью хранения данных в расчете на один бит. Пользователю хотелось бы иметь и недорогую и быструю память. Кэш-память представляет некоторое компромиссное решение этой проблемы.

Кэш-память - это способ организации совместного функционирования двух типов запоминающих устройств, отличающихся временем доступа и стоимостью хранения данных, который позволяет уменьшить среднее время доступа к данным за счет динамического копирования в "быстрое" ЗУ наиболее часто используемой информации из "медленного" ЗУ.

Кэш-памятью часто называют не только способ организации работы двух типов запоминающих устройств, но и одно из устройств - "быстрое" ЗУ. Оно стоит дороже и, как правило, имеет сравнительно небольшой объем. Важно, что механизм кэш-памяти является прозрачным для пользователя, который не должен сообщать никакой информации об интенсивности использования данных и не должен никак участвовать в перемещении данных из ЗУ одного типа в ЗУ другого типа, все это делается автоматически системными средствами.

Кэш-блок располагается между CPU и основной памятью; он состоит из кэш-контроллера и кэш-памяти SRAM. Они могут быть встроены в кристалл процессора (кэш-память, встроенная в кристалл), а могут существовать и в виде отдельного элемента. Имеются также смешанные модели (например, 386SL), в которых кэш-контроллер встроен в кристалл процессора, а собственно кэш-память оформлена в виде внешних схем SRAM. Кэш-память, имеющая емкость в 128-512 килобайт, обычно бывает в десять-тысячу раз меньше, чем основная память.

Когда процессор читает информацию, он обычно направляет соответствующий адрес в память. Однако в нашем случае между процессором и адресом основной памяти находится кэш-контроллер. Он определяет, находятся ли нужные данные в кэш-памяти SRAM. Если да, то ситуация называется "кэш-попаданием". Случай, когда нужные данные находятся в основной памяти, называется "кэш-промахом". В первом случае кэш-контроллер читает данные из быстрой кэш-памяти и направляет их процессору. Это обычно происходит без ожидания, т.е. с максимальной скоростью шины. Запрос на чтение перехватывается кэш-памятью, и основная память о нем не знает.

Кэширование, выполняемое операционной системой

Кэш оперативной памяти состоит из следующих элементов:

набор страниц оперативной памяти, разделённых на буферы, равные по длине блоку данных соответствующего устройства внешней памяти;

набор заголовков буферов, описывающих состояние соответствующего буфера;

хеш-таблицы, содержащей соответствие номера блока заголовку;

списки свободных буферов.

Алгоритм работы кэша с отложенной записью

Изначально все заголовки буферов помещаются в список свободных буферов. Если процесс намеревается прочитать или модифицировать блок, то он выполняет следующий алгоритм:

пытается найти в хеш-таблице заголовок буфера с заданным номером;

в случае, если полученный буфер занят, ждёт его освобождения;

в случае, если буфер не найден в хеш-таблице, берёт первый буфер из хвоста списка свободных;

в случае, если список свободных буферов пуст, то выполняется алгоритм вытеснения (см. ниже);

в случае, если полученный буфер помечен как «грязный», выполняет асинхронную запись содержимого буфера во внешнюю память.

удаляет буфер из хеш-таблицы, если он был помещён в неё;

помещает буфер в хеш-таблицу с новым номером.

Процесс читает данные в полученный буфер и освобождает его. В случае модификации процесс перед освобождением помечает буфер как «грязный». При освобождении буфер помещается в голову списка свободных буферов.

Таким образом:

если процесс прочитал некоторый блок в буфер, то велика вероятность, что другой процесс при чтении этого блока найдёт буфер в оперативной памяти;

запись данных во внешнюю память выполняется только тогда, когда не хватает «чистых» буферов, либо по запросу.

Алгоритм вытеснения

Основная статья: Алгоритмы кэширования

Если список свободных буферов пуст, то выполняется алгоритм вытеснения буфера. Алгоритм вытеснения существенно влияет на производительность кэша. Существуют следующие алгоритмы:

LRU (Least Recently Used) — вытесняется буфер, неиспользованный дольше всех;

MRU (Most Recently Used) — вытесняется последний использованный буфер;

LFU (англ.) (Least Frequently Used) — вытесняется буфер, использованный реже всех;

ARC (англ.) (Adaptive Replacement Cache) — алгоритм вытеснения, комбинирующий LRU и LFU, запатентованный IBM.

Применение того или иного алгоритма зависит от стратегии кэширования данных. LRU наиболее эффективен, если данные гарантированно будут повторно использованы в ближайшее время. MRU наиболее эффективен, если данные гарантированно не будут повторно использованы в ближайшее время. В случае, если приложение явно указывает стратегию кэширования для некоторого набора данных, то кэш будет функционировать наиболее эффективно.