- •Раздел 1. Общие принципы построения эвм

- •Тема 1.1 История и тенденции развития вычислительной техники. Поколения эвм

- •Тема 1.2. Основные характеристики и классификация эвм

- •Тема 1.3. Архитектура эвм

- •Тема 1.4. Структурные схемы и взаимодействие устройств эвм

- •Тема 1.5. Структурная схема и устройства пк

- •Тема 1.6. Микросхемы системной логики Chipset

- •Тема 1.7. Представление информации в компьютере, единицы измерения информации

- •Раздел 2. Программное обеспечение эвм

- •Тема 2.1. Структура программного обеспечения пк

- •Тема 2.2. Операционные системы

- •Тема 2.3. Файл и файловая система

- •Тема 2.4. Функции и характеристики сетевых ос

- •Тема 2.5. Эволюция режимов работы эвм

- •Раздел 3. Структура базового микропроцессора эвм

- •Тема 3.1. Классификация микропроцессоров

- •1. По числу бис:

- •2. По назначению:

- •3. По виду обрабатываемых сигналов:

- •4. По количеству выполняемых программ:

- •5. По характеру временной организации работы:

- •6. По объему набора инструкций:

- •Тема 3.2. Основные характеристики микропроцессоров

- •1.Разрядность регистров микропроцессора;

- •2.Разрядность шины данных;

- •Тема 3.3. Архитектура микропроцессора

- •Тема 3.4. Структура базового микропроцессора

- •Тема 3.5. Блок внутренних регистров базового микропроцессора

- •Тема 3.6. Сегментные регистры, регистр указателя команд и регистры флагов

- •Тема 3.7. Назначение и классификация уу

- •Тема 3.8. Назначение и классификация алу

- •1. По способу представления чисел:

- •2. По способу действия над операндами:

- •3. По выполняемым функциям алу подразделяются на:

- •4. По структурной организации алу подразделяются на устройства, имеющие:

- •Тема 3.9. Исполнение программного кода

- •Тема 3.10. Сегментная структура программ

- •Раздел 4. Основы программирования на ассемблере

- •Тема 4.1. Этапы создания программы на ассемблере

- •Тема 4.2. Формат команд и их классификация

- •Тема 4.3. Классификация операндов

- •Тема 4.4. Виды команд ассемблера

- •Раздел 5. Защищенный режим работы микропроцессора

- •Тема 5.1. Режимы работы микропроцессора

- •Тема 5.2. Адресация памяти в защищенном режиме

- •Тема 5.3. Дескрипторы и таблицы

- •Тема 5.5. Архитектурные особенности современных микропроцессоров

- •Тема 5.4. Суперскалярная архитектура

- •Принципы построения устройств внутренней памяти

- •4.1. Структура памяти эвм

- •3.2 Представление данных в памяти

- •3.3 Типы данных

- •Тема 6.2. Режимы адресации данных памяти

- •8.1. Общие принципы организации вв

- •10.1. Локальная системная шина

- •10.2. Шина расширения

- •11.1. Способы организации доступа к системной магистрали

- •11.2. Возможные структуры систем пдп

- •6.1. Характеристики систем прерывания

- •6.2. Возможные структуры систем прерывания

- •6.3. Организация перехода к прерывающей программе

11.2. Возможные структуры систем пдп

Конкретные технические реализации систем ПДП имеют множество вариантов. Они зависят от типа системной магистрали, архитектуры ЭВМ в целом, типа используемого процессора, целевого назначения ЭВМ, количества устройств на магистрали и т.д. В то же время они являются сложными комбинациями небольшого количества базовых структур систем ПДП. Ниже рассматриваются две основные базовые структуры – радиальная и цепочечная.

Радиальная структура

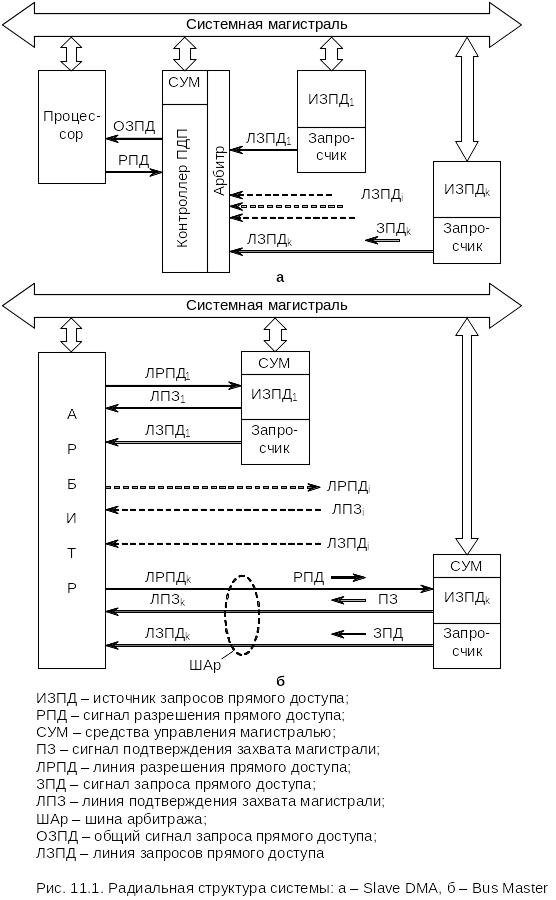

Упрощенные варианты обобщенных структур систем ПДП радиального типа представлены на рис. 11.1.

Характерной особенностью радиальной структуры является то, что каждый ИЗПД (в частном случае ПУ) подключен к отдельному входу контроллера ПДП (рис. 11.1, а) или арбитра (рис. 11.1, б). Отличие двух структур состоит в том, что в случае slave DMA для подключения ИЗПД достаточно одной линии ЛЗПД, по которой устройство выставляет запрос на обслуживание. В системе bus master DMA для подключения устройства к арбитру необходимы, как минимум, три линии – ЛЗПД, ЛПЗ и ЛРПД, которые можно назвать шиной арбитража (ШАр), имеющей собственный вход в арбитр. Каждый вход (в контроллер, в арбитр) обладает определенным уровнем приоритета. Число подключаемых ИЗПД определяется числом входов в контроллер или арбитр. При обслуживании устройств, использующих slave DMA (рис. 11.1, а), всем обменом управляет контроллер ПДП, обязательными компонентами которого являются блок СУМ и арбитр магистрали. Устройства магистрали пассивны и должны содержать только запросчик.

При обслуживании устройств, использующих bus master DMA (рис. 11.1, б), контроллер ПДП, как таковой, отсутствует и централизованно выполняется только арбитраж магистрали. Устройства магистрали активны, поэтому их обязательными компонентами являются запросчик и блок СУМ (как уже отмечалось, "ЦП" в системах bus mastering рассматривается как одно из ИЗПД). После захвата магистраль управляется блоком СУМ конкретного устройства, ведущего обмен (master). В качестве арбитра магистрали используется либо специализированное устройство, либо контроллер ПДП, в котором функции блока СУМ отключены. Линии ЛРПД, присутствующие в системе bus master DMA, предназначены для передачи сигнала РПД, позволяющего активному устройству захватить магистраль. Кроме того, в системе bus master DMA обязательно присутствуют линии ЛПЗ, сигналы которых информируют арбитр о захвате магистрали тем или иным устройством. Сигнал ПЗ всегда выставляет master и удерживает его на линии все время, пока осуществляет обмен (управляет магистралью), поэтому сигнал всегда представлен потенциалом.

В системах радиальной структуры контроллер ПДП может работать, как было отмечено выше, и в комбинированном режиме, т.е. поддерживать как систему slave DMA, так и систему bus master DMA (см. окончание п. 11.1). Запросы от ИЗПД в обеих системах DMA могут быть представлены как уровнем потенциала, так и его перепадом, поскольку поступают в контроллер или арбитр по отдельным линиям. Однако представление запроса потенциалом более предпочтительно, поскольку система DMA становится более устойчивой как к помехам, так и к сбоям аппаратуры. Это существенно снижает вероятность пропуска запроса от ИЗПД.

Основным преимуществом радиальной структуры является то, что упрощается аппаратура арбитра магистрали, поскольку каждый ИЗПД имеет собственную ЛЗПД. Кроме того, несколько упрощается аппаратура ИЗПД и конструкция слота даже в случае bus master DMA, поскольку все активные устройства магистрали имеют отдельную шину арбитража (ШАр). Все это удешевляет радиальную систему по сравнению с цепочечной, рассматриваемой ниже.

Цепочечная структура

Упрощенный вариант обобщенной структуры системы ПДП цепочечного типа представлен на рис. 11.2.

Характерной особенностью цепочечной структуры является то, что множество активных устройств магистрали (ИЗПД), обязательными компонентами которых являются блок СУМ и запросчик, подключены к одной или нескольким шинам арбитража (ШАр). На рис. 11.2 присутствуют две ШАр. После захвата магистраль управляется блоком СУМ конкретного устройства, ведущего обмен (master). Контроллер ПДП отсутствует, и централизованно выполняется только арбитраж магистрали. На рис. 11.2 арбитр изображен как отдельное устройство магистрали, хотя, как отмечено выше, арбитраж может осуществлять и процессор (один из процессоров). Каждая ШАр соответствует одному входу в арбитр и обладает собственным уровнем приоритета. Таким образом, ИЗПД, подключенные к разным ШАр, обладают различным приоритетом. Пассивные устройства магистрали (slave) к ШАр не подключены. Кроме того, приоритет устройств, подключенных к одной ШАр, определяется также их положением в цепи распространения сигнала разрешения прямого доступа (РПД).

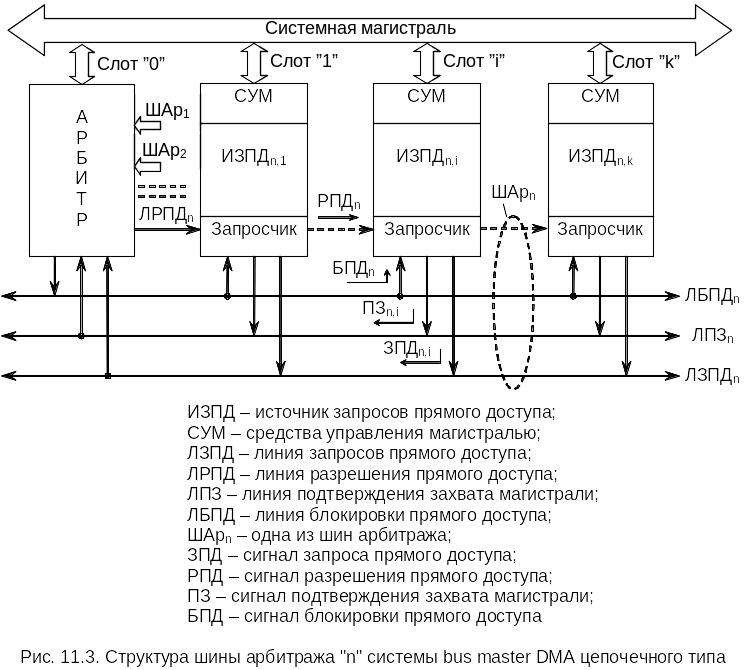

Рассмотрим этот момент более подробно на примере одной ШАрn системы bus master DMA, упрощенная структура которой приведена на рис. 11.3.

Из рисунка следует, что ШАр (для упрощения обозначений здесь и ниже индекс "n" опущен) в такой системе содержит, как минимум, четыре линии – ЛЗПД, ЛРПД, ЛПЗ и ЛБПД. В отличие от радиальной структуры, ИЗПД магистрали подключены к трем линиям ШАр (ЛЗПД, ЛПЗ и ЛБПД) параллельно, поэтому запросы от ИЗПД (сигналы ЗПД) всегда представлены уровнем потенциала. Выходные каскады аппаратных средств формирования запросов в каждом ИЗПД представляют собой ключи с открытым коллектором, объединенные по схеме монтажного "или". Это позволяет исключить потерю запросов, одновременно выставленных запросчиками разных ИЗПД на одну ЛЗПД.

Сигнал РПД распространяется последовательно через все устройства, пока его распространение не будет заблокировано запросчиком ИЗПДi, выставившим запрос прямого доступа (сигнал ЗПДi). Таким образом, приоритет ведущего устройства магистрали определяется его положением в цепи распространения сигнала РПД. Пусть арбитр расположен в слоте с номером "0". Тогда приоритет устройств, расположенных в последующих слотах, будет убывать с ростом номера слота. При отсутствии устройства в слоте необходимо принять меры для того, чтобы цепь распространения сигнала РПД не разрывалась. Это обеспечивается либо специальной конструкцией контактов слота, либо установкой перемычки на системной плате.

Сигнал линии ЛПЗ, как и в радиальной системе bus master DMA, информирует арбитр о захвате магистрали тем или иным устройством. Этот сигнал всегда выставляет master и удерживает его на линии все время, пока осуществляет обмен (управляет магистралью), поэтому сигнал всегда представлен потенциалом.

Линия ЛБПД – общая для всех ШАр и предназначена для передачи от арбитра сигнала блокировки прямого доступа (БПД), который запрещает bus mastering всем интеллектуальным устройствам магистрали. Необходимость в этом может возникнуть, например, при появлении запроса на линии ЛЗПД ШАр более высокого приоритета (при наличии нескольких ШАр) или в случае удержания магистрали одним устройством недопустимо долгое время.

Следует иметь в виду, что системы цепочечной структуры практически работают только в режиме bus master DMA, поскольку арбитр магистрали может идентифицировать только ЛЗПД, с которой поступил запрос, и определить его приоритет. При реализации режима slave DMA контроллеру DMA необходимо будет идентифицировать конкретное ИЗПД на данной линии. Такую операцию контроллер может выполнить только путем последовательного опроса устройств линии, что существенно увеличит время арбитража и усложнит аппаратуру устройств. Между тем техническая реализация таких систем возможна.

Основным преимуществом цепочечной структуры является практически неограниченное количество ИЗПД, подключаемых к одному входу арбитра (одной ШАр) без снижения быстродействия. Однако сложность и объем аппаратуры поддержки системы bus mastering в каждом ИЗПД увеличиваются, что ведет к увеличению стоимости системы.

7 Раздел

Основные принципы организации информационных процессов в вычислительных устройствах

Обработка информации и представление результатов обработки в удобном для человека виде производятся с помощью вычислительных средств. Научно-технический прогресс привел к созданию разнообразных вычислительных средств: электронных вычислительных машин (ЭВМ), вычислительных систем (ВС), вычислительных сетей. Они различаются структурной организацией и функциональными возможностями. Дать определение такому явлению, как ЭВМ, сложно. Достаточно сказать, что само по себе название ЭВМ, т.е. электронные вычислительные машины, не отражает полностью сущность концепции. Слово "электронные" подразумевало электронные лампы в качестве элементной базы, современные ЭВМ правильнее следовало бы называть микроэлектронными. Под словом "вычислительный" понимается устройство, предназначенное для проведения вычислений, однако анализ программ показывает, что современные ЭВМ не более 10 - 15% времени тратят на чисто вычислительную работу - сложение, вычитание, умножение и т.д. Основное время затрачивается на выполнение операций пересылки данных, сравнения, ввода-вывода и т.д. То же самое относится и к англоязычному термину "компьютер", т.е. "вычислитель". К понятию ЭВМ можно подходить с нескольких точек зрения. Представляется разумным определить ЭВМ с точки зрения ее функционирования. Целесообразно описать минимальный набор устройств, который входит в состав любой ЭВМ, и тем самым определить состав минимальной ЭВМ, а также сформулировать принципы работы отдельных блоков ЭВМ и принципы организации ЭВМ как системы, состоящей из взаимосвязанных функциональных блоков. Если же рассматривать ЭВМ как ядро некоторой информационно- вычислительной системы, может оказаться полезным показать информационную модель ЭВМ - определить ее в виде совокупности блоков переработки информации и множества информационных потоков между этими блоками. Принципы фон-Неймана. Большинство современных ЭВМ строится на базе принципов, сформулированных американским ученым, одним из "отцов" кибернетики Дж. фон-Нейманом. Впервые эти принципы были опубликованы фон Нейманом в 1945 г. в его предложениях по машине EDVAC. Эта ЭВМ была одной из первых машин с хранимой программой, т.е. с программой, запоминаемой в памяти машины, а не считываемой с перфокарты или другого подобного устройства. Фон Нейман не только выдвинул основополагающие принципы логического устройства ЭВМ, но и предложил ее структуру. Основными блоками, по Нейману, являются устройство управления (УУ) и арифметико- логическое устройство (АЛУ), обычно объединяемые в центральный процессор, память, внешняя память, устройства ввода и вывода. Схема устройства такой ЭВМ представлена на рисунке 12 (сплошные линии со стрелками указывают направление потоков информации, пунктирные - управляющих сигналов от процессора к остальными узлам ЭВМ). Информация кодируется в двоичной форме и разделяется на единицы, называемые словами. Внешняя память отличается от устройств ввода и вывода тем, что данные в нее заносятся в виде, удобном для компьютера, но недоступном для непосредственного восприятия человеком. Так, накопитель на магнитных дисках относится к внешней памяти, а клавиатура - к устройствам ввода; дисплей и печать - к устройствам вывода. Устройство управления и арифметико-логическое устройство в современных компьютерах объединены в один блок - процессор, являющийся преобразователем информации, поступающей из памяти и внешних устройств (сюда относятся выборка команд из памяти, кодирование и декодирование, выполнение различных, в том числе и арифметических, операций, согласование работы узлов компьютера). Память (ЗУ) хранит информацию (данные) и программы. Запоминающее устройство у современных компьютеров "многоярусно", оно включает оперативное запоминающее устройство (ОЗУ), хранящее ту информацию, с которой компьютер работает непосредственно в данное время (исполняемая программа, часть необходимых для нее данных, некоторые управляющие программы), и внешние запоминающие устройства (ВЗУ) гораздо большей емкости, чем ОЗУ, но с существенно более медленным доступом (и значительно меньшей стоимостью в расчете на 1 байт хранимой информации). На ОЗУ и ВЗУ классификация устройств памяти не заканчивается - определенные функции выполняют и СОЗУ (сверхоперативное запоминающее устройство), и ПЗУ (постоянное запоминающее устройство), и другие подвиды компьютерной памяти. Алгоритм представляется в форме последовательности управляющих слов, которые определяют смысл операции. Эти управляющие слова называются командами. Совокупность команд, представляющая собой алгоритм, называется программой. В построенной по описанной схеме ЭВМ происходит последовательное считывание команд из памяти и их выполнение. Номер (адрес) очередной ячейки памяти, из которой будет извлечена следующая команда программы, указывается специальным устройством - счетчиком команд в УУ. Его наличие также является одним из характерных признаков рассматриваемой архитектуры. Разработанные фон Нейманом основы архитектуры вычислительных устройств оказались настолько фундаментальными, что получили в литературе название "фон-неймановской архитектуры". Подавляющее большинство вычислительных машин на сегодняшний день - фон- неймановские машины. Исключение составляют лишь отдельные разновидности систем для параллельных вычислений, в которых отсутствует счетчик команд и имеются другие существенные принципиальные отличия от классической модели (примерами могут служить потоковая и редукционная вычислительные машины). По-видимому, значительное отклонение от фон-неймановской архитектуры произойдет в результате развития идеи машин пятого поколения, в основе обработки информации в которых лежат не вычисления, а логические выводы. Принципы фон Неймана практически можно реализовать множеством различных способов. Ниже рассмотрим два из них: ЭВМ с шинной и канальной организацией. Перед тем как описать принципы функционирования ЭВМ, введем несколько определений. Архитектура ЭВМ - абстрактное определение машины в терминах основных функциональных модулей, языка, структур данных. Архитектура не определяет особенности реализации аппаратной части ЭВМ, времени выполнения команд, степени параллелизма, ширины шин и других аналогичных характеристик. Архитектура отображает аспекты структуры ЭВМ, которые являются видимыми для пользователя: систему команд, режимы адресации, форматы данных, набор программно-доступных регистров. Другими словами, термин "архитектура" используется для описания возможностей, предоставляемых ЭВМ. Весьма часто употребляется термин "конфигурация ЭВМ", под которым понимается компоновка вычислительного устройства с четким определением характера, количества, взаимосвязей и основных характеристик его функциональных элементов. Термин "организация ЭВМ" определяет, как реализованы возможности ЭВМ. Команда - совокупность сведений, необходимых процессору для выполнения определенного действия при выполнении программы. Команда состоит из кода операции, содержащего указание на операцию, которую необходимо выполнить, и нескольких адресных полей, содержащих указание на места расположения операндов команды. Способ вычисления адреса по информации, находящейся в адресном поле команды, называется режимом адресации. Множество команд, реализованных в данной ЭВМ, образует ее систему команд.

ПРИНЦИПЫ ОРГАНИЗАЦИИ СИСТЕМ ПРЕРЫВАНИЯ ПРОГРАММ

В процессе выполнения программ внутри ЭВМ или во внешней среде могут возникнуть события, требующие немедленной реакции со стороны процессора. Реакция состоит в том, что процессор прерывает обработку текущей программы (прерываемой программы) и переходит к выполнению некоторой другой программы (прерывающей программы), специально предназначенной для данного события. По завершении этой программы процессор возвращается к выполнению прерванной программы. Рассматриваемый процесс называется прерыванием программы и может быть пояснен рис. 6.1.

Каждое событие, требующее прерывания, сопровождается сигналом, оповещающим об этом ЭВМ и называемым запросом прерывания. Прерывания могут порождаться внутренними и внешними событиями:

Внутренние – сбой в аппаратуре, переполнение разрядной сетки, деление на 0, выход из установленной зоны памяти, попытка обратиться к запрещенной зоне памяти, попытка обращения к защищенным программам операционной системы, сигнал от таймера и т.д.

Внешние – запрос от другой ЭВМ, сообщение от аварийных датчиков управляемого технологического процесса, запрос оператора, требование от ПУ операции обмена, запросы на обслуживание клавиатуры, мыши и т.д.

В общем случае запросы прерывания генерируются несколькими, развивающимися параллельно во времени процессами, которые в некоторый момент времени требуют вмешательства процессора. Общим во всех этих запросах является то, что моменты их поступления невозможно предусмотреть. Это существенно отличает процесс прерывания от рассмотренного ранее процесса передачи управления подпрограмме, происходящего в заранее известных точках основной программы.

Возможность прерывания – важное свойство ЭВМ, позволяющее эффективно использовать производительность процессора и прежде всего при организации параллельной работы процессора и периферийных устройств ЭВМ.

Для эффективной организации процесса прерывания и минимизации усилий программиста современные ЭВМ снабжены соответствующими программно-аппаратными средствами, которые получили название контроллера прерываний.

Контроллер прерываний в общем случае является достаточно сложным программируемым устройством, требующим соответствующей инициализации со стороны процессора. В процессе инициализации в управляющие регистры контроллера загружается информация о дисциплине обслуживания запросов прерывания, количестве используемых входов, режиме взаимодействия с процессором и т.д. Обычно инициализация контроллера выполняется при запуске вычислительной системы. Однако большинство контроллеров прерываний допускают перепрограммирование и в процессе обработки программы, в частности изменение дисциплины обслуживания поступающих запросов прерывания. Конструктивно контроллеры прерываний выполняются в виде отдельных специализированных БИС, но в ряде случаев могут быть встроены в другие устройства вычислительной системы. Простейшие контроллеры прерываний небольших микроЭВМ часто строятся на логических микросхемах общего назначения.

Основными функциями системы прерывания являются:

запоминание состояния прерываемой программы и осуществление перехода к прерывающей программе;

восстановление состояния прерванной программы и возврат к ней.

Под термином состояние программы (процессора), строго говоря, следует понимать совокупность состояний всех запоминающих элементов (триггеров, регистров, ячеек памяти) в соответствующий момент времени (например, после выполнения микрокоманды, команды, программы). Однако не вся эта информация искажается при переходе к другой команде или программе, поэтому из всего многообразия информации о состоянии программы (процессора) отбирают наиболее существенные ее элементы, изменяющиеся при переходе к другой команде или программе.

Вектор состояния в каждый момент времени должен содержать информацию, достаточную для запуска программы с точки, соответствующей моменту формирования данного вектора состояния. При этом предполагается, что другая информация о состоянии узлов процессора либо не существенна, либо может быть восстановлена программным путем.

Вектор состояния формируется в соответствующих регистрах процессора, изменяясь после выполнения каждой команды. Наборы информационных элементов, образующих вектор состояния, отличаются у ЭВМ разных типов и зависят от сложности процессора. В простейших процессорах эти наборы невелики. Например, в процессоре КР580ВМ80 (I8080) вектор состояния состоит из содержимого счетчика адреса команд (16 бит), содержимого регистра признаков (8 бит) и содержимого аккумулятора (8 бит). В более сложных процессорах вектор состояния может содержать существенно большее количество элементов.

Аналогично, вектор начального состояния должен содержать всю необходимую информацию для начального запуска программы. Во многих случаях вектор начального состояния содержит только один элемент – начальный адрес запускаемой программы.

При рассмотрении систем прерывания очень широко используется также термин вектор прерывания, который является ничем иным, как вектором начального состояния прерывающей программы (обработчика). Вектор прерывания содержит всю необходимую информацию для перехода к обработчику, в том числе его начальный адрес. Каждому уровню прерываний (см. п. 6.1), а в простых ЭВМ каждому входу прерывания (периферийному устройству) соответствует свой вектор прерывания, который инициализирует выполнение соответствующего обработчика. Обычно векторы прерывания хранятся в специально выделенных фиксированных ячейках памяти с короткими адресами. Таким образом, для перехода к соответствующей прерывающей программе процессор должен располагать не только вектором прерывания, но и адресом этого вектора.

Следует иметь в виду, что понятие вектор прерывания достаточно условно, поскольку в абсолютном большинстве случаев вектор прерывания состоит только из одного элемента – начального адреса прерывающей программы (обработчика).

При наличии нескольких источников запросов должен быть установлен определенный порядок обслуживания поступающих запросов, т.е. должны быть установлены приоритетные соотношения (дисциплина обслуживания). Они определяют, какой из нескольких запросов, поступивших одновременно, подлежит обработке в первую очередь, имеет ли право данный запрос прерывать ту или иную программу и т.д. Все это входит в процедуру перехода к прерывающей программе.