- •Раздел 1. Общие принципы построения эвм

- •Тема 1.1 История и тенденции развития вычислительной техники. Поколения эвм

- •Тема 1.2. Основные характеристики и классификация эвм

- •Тема 1.3. Архитектура эвм

- •Тема 1.4. Структурные схемы и взаимодействие устройств эвм

- •Тема 1.5. Структурная схема и устройства пк

- •Тема 1.6. Микросхемы системной логики Chipset

- •Тема 1.7. Представление информации в компьютере, единицы измерения информации

- •Раздел 2. Программное обеспечение эвм

- •Тема 2.1. Структура программного обеспечения пк

- •Тема 2.2. Операционные системы

- •Тема 2.3. Файл и файловая система

- •Тема 2.4. Функции и характеристики сетевых ос

- •Тема 2.5. Эволюция режимов работы эвм

- •Раздел 3. Структура базового микропроцессора эвм

- •Тема 3.1. Классификация микропроцессоров

- •1. По числу бис:

- •2. По назначению:

- •3. По виду обрабатываемых сигналов:

- •4. По количеству выполняемых программ:

- •5. По характеру временной организации работы:

- •6. По объему набора инструкций:

- •Тема 3.2. Основные характеристики микропроцессоров

- •1.Разрядность регистров микропроцессора;

- •2.Разрядность шины данных;

- •Тема 3.3. Архитектура микропроцессора

- •Тема 3.4. Структура базового микропроцессора

- •Тема 3.5. Блок внутренних регистров базового микропроцессора

- •Тема 3.6. Сегментные регистры, регистр указателя команд и регистры флагов

- •Тема 3.7. Назначение и классификация уу

- •Тема 3.8. Назначение и классификация алу

- •1. По способу представления чисел:

- •2. По способу действия над операндами:

- •3. По выполняемым функциям алу подразделяются на:

- •4. По структурной организации алу подразделяются на устройства, имеющие:

- •Тема 3.9. Исполнение программного кода

- •Тема 3.10. Сегментная структура программ

- •Раздел 4. Основы программирования на ассемблере

- •Тема 4.1. Этапы создания программы на ассемблере

- •Тема 4.2. Формат команд и их классификация

- •Тема 4.3. Классификация операндов

- •Тема 4.4. Виды команд ассемблера

- •Раздел 5. Защищенный режим работы микропроцессора

- •Тема 5.1. Режимы работы микропроцессора

- •Тема 5.2. Адресация памяти в защищенном режиме

- •Тема 5.3. Дескрипторы и таблицы

- •Тема 5.5. Архитектурные особенности современных микропроцессоров

- •Тема 5.4. Суперскалярная архитектура

- •Принципы построения устройств внутренней памяти

- •4.1. Структура памяти эвм

- •3.2 Представление данных в памяти

- •3.3 Типы данных

- •Тема 6.2. Режимы адресации данных памяти

- •8.1. Общие принципы организации вв

- •10.1. Локальная системная шина

- •10.2. Шина расширения

- •11.1. Способы организации доступа к системной магистрали

- •11.2. Возможные структуры систем пдп

- •6.1. Характеристики систем прерывания

- •6.2. Возможные структуры систем прерывания

- •6.3. Организация перехода к прерывающей программе

8.1. Общие принципы организации вв

В каждой ЭВМ применяются особые способы ВВ, различные конфигурации схем и типы устройств. Однако для большинства ЭВМ можно выделить следующие общие принципы:

Передача данных осуществляется по общей системной магистрали (что характерно для микроЭВМ) либо по специальной магистрали ВВ (что характерно для мини- и больших ЭВМ). Иногда отдельная быстродействующая магистраль ВВ выделяется только для обмена в режиме ПДП.

Подключение ПУ к системному интерфейсу осуществляется с помощью промежуточного интерфейса, поддерживаемого со стороны микроЭВМ и ПУ соответствующими адаптерами (см. п. 7.2).

Операции ВВ инициируются только в случае готовности ПУ к обмену. При наличии нескольких ПУ и обмене в режиме прерывания или ПДП вводится система приоритетов, позволяющая избежать конфликтов. В соответствии с этой системой контроллер прерываний или ПДП среди ПУ, готовых к обмену, в первую очередь обслуживает ПУ с высшим приоритетом (см. гл. 6 и гл. 11).

Передача данных осуществляется двумя способами:

отдельными битами, и тогда промежуточный интерфейс называется последовательным;

полными словами (например, целым байтом), и тогда промежуточный интерфейс называется параллельным.

Информация, передаваемая в процессе ВВ, подразделяется:

на собственно данные (обозначим D);

управляющие данные (обозначим U).

Управляющие данные от процессора называются также командными словами или приказами. Они инициируют действия, не связанные непосредственно с передачей данных (запуск устройства, запрещение прерываний, установка режимов и т.д.).

Управляющие данные от ПУ называются словами состояния. Они содержат информацию об определенных признаках (о готовности устройства к передаче данных, о наличии ошибок при обмене и т.д.). Состояние обычно представляется в декодированной форме – один бит для каждого признака.

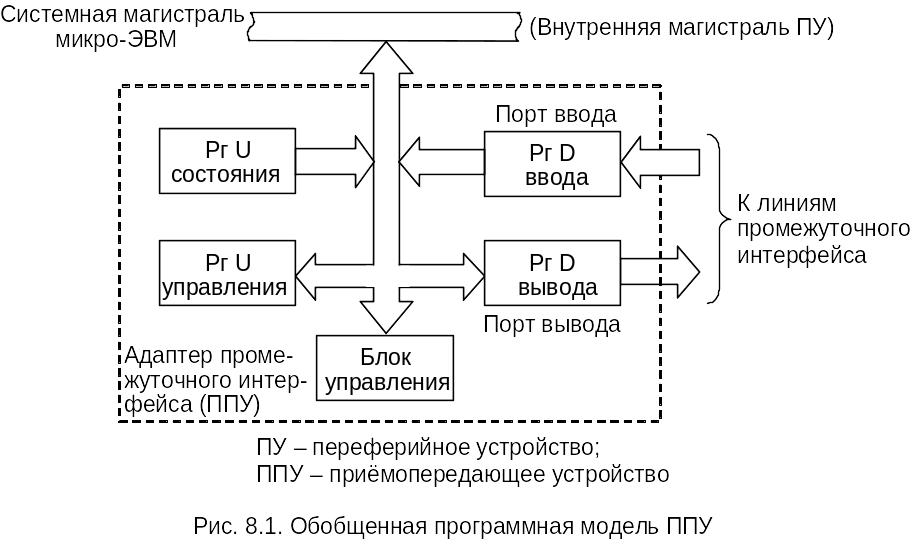

С учетом всего изложенного можно изобразить наиболее общую программную модель адаптера промежуточного интерфейса (ППУ), связывающего системную магистраль микроЭВМ и внутреннюю магистраль ПУ. Такая обобщенная программная модель ППУ представлена на рис. 8.1. Каждый из указанных регистров должен иметь адрес, который может идентифицироваться дешифратором адреса.

Естественно, что конкретная модель адаптера может отличаться от обобщенной схемы, например, регистр состояния и управления могут быть объединены в один регистр, вместо двух однонаправленных портов используют один двунаправленный, регистров управления может быть несколько. Однако при этом логические функции указанных четырех регистров остаются.

В соответствии с рассмотренными ранее различными структурами системной магистрали возможны два способа организации операций ВВ.

Изолированный ВВ (соответствует структуре с изолированными шинами)

Изолированный ВВ предполагает наличие специальных команд ВВ. В МП КР580 это команды IN и OUT. Адресное пространство регистров ППУ изолировано от адресного пространства ячеек памяти, т.е. регистры ППУ и ячейки памяти могут иметь одинаковый адрес. Команды IN и OUT – двухбайтовые. Первый байт – КОП, а второй несет информацию о номере адресуемого ППУ и номере адресуемого в нем регистра. При этом в МП КР580 предусмотрена возможность обмена данными по командам IN, OUT только между аккумулятором и адресуемыми регистрами.

ВВ по общей шине (соответствует структуре с общими шинами)

В этом случае адресация к регистрам ППУ осуществляется как к обычным ячейкам памяти, т.е. ячейки памяти и регистры ППУ имеют единое адресное пространство. Можно использовать все команды обращения к ячейкам памяти. Это удобно, однако часть адресного пространства памяти используется для адресации регистров ППУ, что может вызвать трудности, если программа большая и много ПУ.

ПУ и микроЭВМ могут обмениваться достаточно большими объемами информации, которые невозможно поместить только в регистрах процессора. Ввиду этого часто операции ВВ являются операциями обмена данными между ОП и ПУ. Как уже отмечалось, для повышения гибкости всей вычислительной системы в микроЭВМ предусмотрено три режима выполнения операций ВВ. Рассмотрим эти режимы подробнее.

ЭВОЛЮЦИЯ ШИННОЙ АРХИТЕКТУРЫ IBM PC

В начале настоящего курса (см. гл.1) было показано, что переход от мэйнфреймов к малым ЭВМ (мини и микро) сопровождался существенным упрощением внутренней структуры компьютера, а именно, переходом к магистрально-модульной структуре, простейший вариант которой представлен на рис. 1.4. Магистрально-модульная структура предполагает наличие в компьютере некоторой общей магистрали, к которой в необходимой номенклатуре и количестве подключены все устройства ЭВМ, выполненные в виде функционально законченных блоков. Эта магистраль получила название системной (см. п. 7.1). Первоначально это был единственный канал связи, по которому внутри ЭВМ передавалась информация между двумя и более компонентами системы. В процессе эволюции мини- и микроЭВМ, а также повышения быстродействия процессоров одной системной магистрали оказалось недостаточно. Однако необходимость преемственности программно-аппаратных средств серийно выпускаемых компьютеров разных поколений не позволила так просто заменить разработанные ранее системные магистрали на более быстродействующие, хотя их производительность не соответствовала производительности новых поколений процессоров. Компромиссным решением этой проблемы оказалось введение помимо основной системной магистрали ряда других, более быстродействующих магистралей, которые получили название локальных шин. В процессе эволюции ЭВМ некоторые из них потеряли свое значение и исчезли (например, VLB), другие продолжали развиваться, принимая на себя все больше функций основной системной магистрали (например, PCI). Ввиду этого в современных компьютерах помимо основной системной магистрали, имеется ряд быстродействующих локальных шин различного назначения.

Прежде чем перейти к рассмотрению основных этапов эволюции шинной архитектуры PC фирмы IBM, необходимо сделать ряд замечаний. Уже отмечалось, что в литературе встречаются различные термины для обозначения системной или общей магистрали. Это прежде всего термины: "общая шина", "системная шина", "шина ВВ" и "шина расширения". Последний термин отражает тот факт, что системная магистраль позволяет подключать к компьютеру дополнительные ПУ для расширения или изменения его возможностей, т.е. позволяет изменять конфигурацию оборудования. При этом часть устройств ВВ устанавливается непосредственно на системной (материнской) плате и не может быть заменена пользователем, а часть устройств ВВ размещается в слотах, установленных на системной магистрали. При взаимодействии с МП те и другие используют одну и ту же системную магистраль. Количество слотов расширения может быть разным. В первом IBM PC их было пять, а в PC/XT – восемь. В последующих моделях РС, имеющих быстродействующие локальные шины, их число изменялось в зависимости от конкретной конфигурации материнской платы.

При дальнейшем изложении материала будет использоваться термин шина расширения (ШР), поскольку сама системная магистраль уже в первых РС претерпела существенные изменения по сравнению с классическим вариантом структуры простейшей микроЭВМ, изображенным на рис. 1.4.