- •Раздел 1. Общие принципы построения эвм

- •Тема 1.1 История и тенденции развития вычислительной техники. Поколения эвм

- •Тема 1.2. Основные характеристики и классификация эвм

- •Тема 1.3. Архитектура эвм

- •Тема 1.4. Структурные схемы и взаимодействие устройств эвм

- •Тема 1.5. Структурная схема и устройства пк

- •Тема 1.6. Микросхемы системной логики Chipset

- •Тема 1.7. Представление информации в компьютере, единицы измерения информации

- •Раздел 2. Программное обеспечение эвм

- •Тема 2.1. Структура программного обеспечения пк

- •Тема 2.2. Операционные системы

- •Тема 2.3. Файл и файловая система

- •Тема 2.4. Функции и характеристики сетевых ос

- •Тема 2.5. Эволюция режимов работы эвм

- •Раздел 3. Структура базового микропроцессора эвм

- •Тема 3.1. Классификация микропроцессоров

- •1. По числу бис:

- •2. По назначению:

- •3. По виду обрабатываемых сигналов:

- •4. По количеству выполняемых программ:

- •5. По характеру временной организации работы:

- •6. По объему набора инструкций:

- •Тема 3.2. Основные характеристики микропроцессоров

- •1.Разрядность регистров микропроцессора;

- •2.Разрядность шины данных;

- •Тема 3.3. Архитектура микропроцессора

- •Тема 3.4. Структура базового микропроцессора

- •Тема 3.5. Блок внутренних регистров базового микропроцессора

- •Тема 3.6. Сегментные регистры, регистр указателя команд и регистры флагов

- •Тема 3.7. Назначение и классификация уу

- •Тема 3.8. Назначение и классификация алу

- •1. По способу представления чисел:

- •2. По способу действия над операндами:

- •3. По выполняемым функциям алу подразделяются на:

- •4. По структурной организации алу подразделяются на устройства, имеющие:

- •Тема 3.9. Исполнение программного кода

- •Тема 3.10. Сегментная структура программ

- •Раздел 4. Основы программирования на ассемблере

- •Тема 4.1. Этапы создания программы на ассемблере

- •Тема 4.2. Формат команд и их классификация

- •Тема 4.3. Классификация операндов

- •Тема 4.4. Виды команд ассемблера

- •Раздел 5. Защищенный режим работы микропроцессора

- •Тема 5.1. Режимы работы микропроцессора

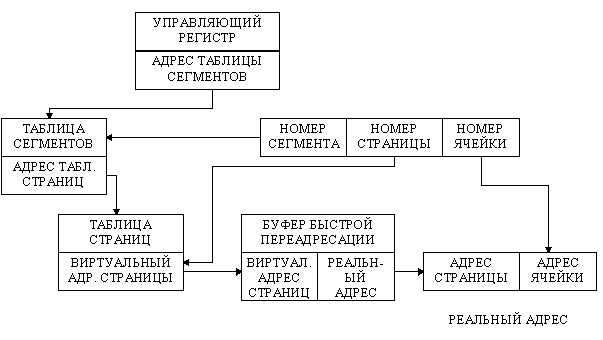

- •Тема 5.2. Адресация памяти в защищенном режиме

- •Тема 5.3. Дескрипторы и таблицы

- •Тема 5.5. Архитектурные особенности современных микропроцессоров

- •Тема 5.4. Суперскалярная архитектура

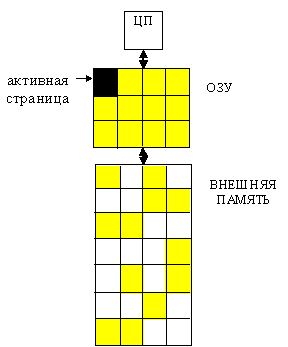

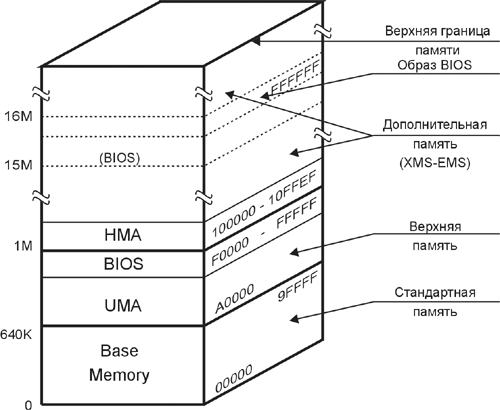

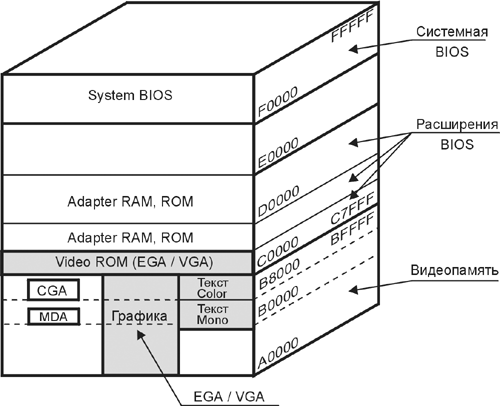

- •Принципы построения устройств внутренней памяти

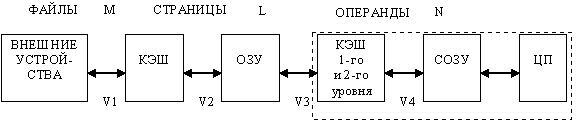

- •4.1. Структура памяти эвм

- •3.2 Представление данных в памяти

- •3.3 Типы данных

- •Тема 6.2. Режимы адресации данных памяти

- •8.1. Общие принципы организации вв

- •10.1. Локальная системная шина

- •10.2. Шина расширения

- •11.1. Способы организации доступа к системной магистрали

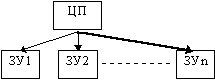

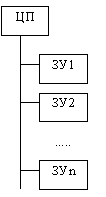

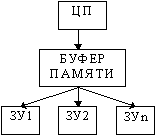

- •11.2. Возможные структуры систем пдп

- •6.1. Характеристики систем прерывания

- •6.2. Возможные структуры систем прерывания

- •6.3. Организация перехода к прерывающей программе

Тема 6.2. Режимы адресации данных памяти

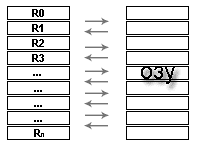

90% работы процессора связано с оперативной памятью. Он берет оттуда данные, обрабатывает их и отсылает обратно в память. Кроме этого, сам процессор имеет собственную память, называемую регистрами. Графически это можно изобразить так:

Рис.31 Регистры процессора

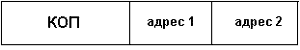

где слева регистры процессора R1, R2 … Rn, а справа ячейки памяти. В процессор поступают несколько операндов с которыми надо произвести некоторые действия. Но для того чтобы происходил обмен между процессором и оперативной памятью нужно использоать несколько режимов адресации. Но для начала нужно знать о формате команды. Под форматом команды понимают совокупность размера всех полей и их расположения в команде. Представим себе упрощенный вид команды:

![]()

Рис.32 Упрощенный вид команды

Команда делится на две области: область кода операции и область адресов. Вначале идет код операции (КОП) который говорит, что вообще необходимо делать, а затем идет адрес операнда/операндов с которым/которыми это надо делать. Адресная область может состоять из нескольких частей – это, так называемые многоадресные команды.

Адресная область состоит из трех полей: в первых двух лежат адреса операндов, а в третье будет записан адрес результата действия над операндами.

В двухадресных командах адресная область состоит из двух полей: поле адреса первого операнда и поле адреса второго операнда. Адрес результата действия над операндами будет записан в первое поле.

Рис.33 Адрес результата действия

В одноадресных командах адресная область состоит из одного единственного поля, в котором лежит адрес операнда, а адрес второго операнда и результата совпадает с сумматором. Существуют так же и безадресные команды, которые применяются при работе со стеками. Чаще всего используются двух-, одно- и безадресные команды.

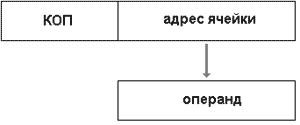

Для того, чтобы процессор нашел нужные операнды, в поле адреса операнда вкладывают … адрес операнда (то есть тот адрес, по которому, обратившись, процессор найдет операнд или, проще говоря, необходимые данные).

Существует несколько типов адресации. Начнем с непосредственной адресации –когда вместо адреса операнда в команде указывается сам операнд (правда, если он представляет целое число). Выбрав из памяти код операции, процессору уже нет необходимости лезть опять в память за самим операндом, ведь он передается вместе с КОП.

![]()

Рис.34 Непосредственная адресация

Но такое не всегда бывает. Если в команде указан полный адрес ячейки, где лежат необходимые данные, то это уже полный или абсолютный тип адресации.

Рис.35 Полный или абсолютный тип адресации

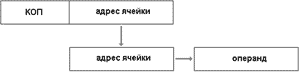

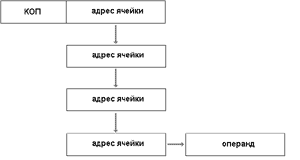

Кроме этого, в поле адреса операнда может быть указан адрес или регистра или ячейки памяти, в которой лежит то же адрес, по которому можно найти ячейку с нужным операндом.

Рис.36 Ячейка с нужным операндом

Такой способ адресации называться косвенным. При косвенной адресации количество ячеек с адресами других ячеек может быть несколько (цепочка).

Рис.37 Косвенная адресация

Количество звеньев (или ступеней перехода) называется глубиной косвенной адресации.

Все выше приведенные типы адресации касались одного операнда. А как же быть в случае с несколькими операндами, т.е массивами? Тогда обычно указывается адрес массива и номер (индекс) элемента. Базовый (начальный) адрес указывается в команде. Кроме этого, там же, в команде, есть поле, где указан номер регистра, в котором лежит значение индекса или номер ячейки в массиве относительно начального адреса. Тогда адрес каждой ячейки массива будет получаться из суммы начального адреса и того, что содержит указанный регистр, это называется модификацией адресов. Кроме того, существует тип адресации, когда в регистре лежит начальный адрес. В команде указан адрес этого регистра, а так же записано смещение относительно начального адреса. Все остальные адреса операндов будут получены из суммы адреса и смещения. Такой вот тип адресации называется относительным.

При относительной адресации можно еще и модифицировать адреса. В этом случае адрес будет равен сумме начального адреса плюс смещение плюс содержимое индексного регистра.

Если система использует несколько типов адресации, то в команде обязательно записывается, какой способ будет применен в данный момент, т.е в команде указывается признак адресации в поле признака операции.

Способы организации памяти. Адресная память

Функционально ЗУ любого типа всегда состоят из запоминающего массива, хранящего информацию, и вспомогательных, весьма сложных блоков, служащих для поиска в массиве, записи и считывания (и, если требуется, для регенерации).

Запоминающий массив (ЗМ) состоит из множества одинаковых запоминающих элементов (ЗЭ). Все ЗЭ организованы в ячейки, каждая из которых предназначена для хранения единицы информации в виде двоичного кода, число разрядов которого определяется шириной выборки. Способ организации памяти зависит от методов размещения и поиска информации в ЗМ. По этому признаку различают адресную, ассоциативную и стековую память.

Адресная память

В памяти с адресной организацией размещение и поиск информации в ЗМ основаны на использовании адреса хранения единицы информации, которую в дальнейшем для краткости будем называть словом. Адресом служит номер ячейки ЗМ, в которой это слово размещается. При записи (считывании) слова в ЗМ инициирующая эту операцию команда должна указывать адрес (номер) ячейки, по которому надо произвести запись (считывание).

На рис. 4.2 изображена обобщенная структура адресной памяти.

Цикл обращения к памяти инициализируется поступающим в БУП сигналом "Обращение". Общая часть цикла обращения включает в себя прием в РгА с шины адреса (ША) адреса обращения и прием в БУП управляющего сигнала "Операция", указывающего вид запрашиваемой операции (считывание или запись).

Считывание. БАВ дешифрирует адрес и посылает сигнал, выделяющий заданную адресом ячейку ЗМ. В общем случае БАВ может также посылать в выделенную ячейку памяти сигналы, настраивающие ЗЭ ячейки на запись или считывание. После этого записанное в ячейку слово считывается усилителями БУС и передается в РгИ. Затем в памяти с разрушающим считыванием происходит регенерация информации путем записи слова из РгИ через БУЗ в ту же ячейку ЗМ. Операция считывания завершается выдачей слова из РгИ на выходную информационную шину ШИвых.

Запись. Помимо указанной выше общей части цикла обращения происходит прием записываемого слова с входной шины ШИвх в РгИ. Сама запись в общем случае состоит из двух операций – очистки ячейки и собственно записи. Для этого БАВ сначала производит выборку и очистку ячейки, заданной адресом в РгА. Очистка ячейки ЗМ (приведение в исходное состояние) может осуществляться по-разному. В частности, в памяти с разрушающим считыванием очистку можно производить сигналом считывания слова в ячейке при блокировке БУС (чтобы в РгИ не поступила информация). Затем в выбранную ячейку записывается новое слово.

Необходимость в операции очистки ячейки перед записью, так же как и в операции регенерации информации при считывании, определяется типом используемых ЗЭ, способами управления, особенностями электронной структуры БИС памяти, поэтому в полупроводниковых памятях эти операции могут отсутствовать.

БУП генерирует необходимые последовательности управляющих сигналов, инициирующих работу отдельных узлов памяти. Следует иметь в виду, что БУП может быть весьма сложным устройством (своеобразным управляющим контроллером, имеющим собственную кэш-память), придающим БИСу памяти в целом специальные потребительские свойства, такие как многопортовость, конвейерная выдача информации и т.п.

Ассоциативная память

В памяти этого типа поиск информации происходит не по адресу, а по ее содержанию. Под содержанием информации в данном случае понимается не смысловая нагрузка лежащего на хранении в ячейке памяти слова, а содержание ЗЭ ячейки памяти, т.е. побитовый состав записанного двоичного слова. При этом ассоциативный запрос (признак) также представляет собой двоичный код с определенным побитовым составом. Поиск по ассоциативному признаку происходит параллельно во времени для всех ячеек ЗМ и представляет собой операцию сравнения содержимого разрядов регистра признака с содержимым соответствующих разрядов ячеек памяти. Для организации такого поиска все ЗЭ ЗМ снабжены однобитовыми процессорами, поэтому в ряде случаев память такого типа рассматривают как многопроцессорную систему.

Полностью ассоциативная память большого объема является очень дорогостоящим устройством, поэтому для ее удешевления уменьшают число однобитовых процессоров до одного на ячейку памяти. В этом случае сравнение ассоциативного запроса с содержимым ячеек памяти идет последовательно для отдельных разрядов, параллельно во времени для всех ячеек ЗМ.

При очень больших объемах памяти на определенных классах задач ассоциативный поиск существенно ускоряет обработку данных и уменьшает вероятность сбоя в ЭВМ. Кроме того, ассоциативные ЗУ с блоками соответствующих комбинационных схем позволяют выполнить в памяти достаточно сложные логические операции: поиск максимального или минимального числа в массиве, поиск слов, заключенных в определенные границы, сортировку массива и т.д.

Следует отметить, что ассоциативный поиск можно реализовать и в компьютере с обычной адресной памятью, последовательно вызывая записанные в ячейки памяти слова в процессор и сравнивая их с некоторым ассоциативным признаком (шаблоном). Однако при больших объемах памяти на это будет затрачено много времени. При использовании ассоциативной памяти можно, не считывая слов из ОП в процессор, за одно обращение определить количество слов, отвечающих тому или иному ассоциативному запросу. Это позволяет в больших базах данных очень оперативно реализовать запрос типа: сколько жителей области не представило декларацию о доходах и т.п.

В некоторых специализированных ЭВМ ОП или его часть строится таким образом, что позволяет реализовать как ассоциативный, так и адресный поиск информации.

Упрощенная структурная схема ассоциативной памяти, в которой все ЗЭ ЗМ снабжены однобитовыми процессорами, приведена на рис. 4.3.

Первоначально рассмотрим операцию, называющуюся контроль ассоциации. Эта операция является общей для операции считывания и записи, а также имеет самостоятельное значение.

По входной информационной шине в РгАП поступает n-разрядный ассоциативный запрос, т.е. заполняются разряды от 0 до n-1. Одновременно в РгМ поступает код маски поиска, при этом n-й разряд РгМ устанавливается в 0. Ассоциативный поиск производится лишь для совокупности разрядов РгАП, которым соответствуют 1 в РгМ (незамаскированные разряды РгАП). Для слов, в которых цифры в разрядах совпали с незамаскированными разрядами РгАП, КС устанавливает 1 в соответствующие разряды РгСв и 0 в остальные разряды.

Комбинационная схема формирования результата ассоциативного обращения ФС формирует из слова, образовавшегося в РгСв, как минимум три сигнала:

0 – отсутствие в ЗМ слов, удовлетворяющих ассоциативному признаку;

1 – наличие одного такого слова;

2 – наличие более чем одного слова.

Возможны и другие операции над содержимым РгСв, например подсчет количества единиц, т.е. подсчет слов в памяти, удовлетворяющих ассоциативному запросу, и т.п.

Формирование содержимого РгСв и 0, 1, 2 по содержимому РгАП, РгМ, ЗМ и называется операцией контроля ассоциации.

Считывание. Сначала производится контроль ассоциации по признаку в РгАП.

Затем:

0 = 1 – считывание отменяется из-за отсутствия искомой информации;

1 = 1 – считывается в РгИ найденное слово, после чего выдается на ШИвых;

2 = 1 – считывается слово, имеющее, например, наименьший номер среди ячеек, отмеченных 1 в РгСв, после чего выдается на ШИвых.

Запись. Сначала отыскивается свободная ячейка (полагаем, что в разряде занятости свободной ячейки записан 0). Для этого выполняется контроль ассоциации при РгАП=111...10 и РгМ=000...01, т.е. n-й разряд РгАП устанавливается в 0, а n-й разряд РгМ – в 1. При этом свободная ячейка отмечается 1 в РгСв. Для записи выбирают свободную ячейку, например, с наименьшим номером. В нее записывается слово, поступившее с ШИвх в РгИ.

Следует отметить, что на данной схеме не изображены блоки БУП, БУС, БУЗ, которые есть в реальных устройствах. Кроме того, для построения ассоциативной памяти требуются запоминающие элементы, допускающие считывание без разрушения.

Стековая память (магазинная)

Стековая память, так же как и ассоциативная, является безадресной. Стековая память может быть организована как аппаратно, так и на обычном массиве адресной памяти.

В случае аппаратной реализации ячейки стековой памяти образуют одномерный массив, в котором соседние ячейки связаны друг с другом разрядными цепями передачи слов (рис. 4.4). При этом возможны два типа устройств (а, б), принципы функционирования которых различны. Рассмотрим первоначально структуру на рис. 4.4, а.

Запись нового слова, поступившего с ШИвх, производится в верхнюю (нулевую) ячейку, при этом все ранее записанные слова (включая слово в ячейке 0) сдвигаются вниз, в соседние ячейки, номера которых на единицу больше. Считывание возможно только из верхней (нулевой) ячейки памяти. Основной режим – это считывание с удалением. При этом все остальные слова в памяти сдвигаются вверх, в соседние ячейки с меньшими номерами. В такой памяти реализуется правило: последний пришел – первый ушел. Стеки подобного типа принято называть стеками LIFO (Last In – First Out).

В ряде случаев устройства стековой памяти предусматривают также операцию простого считывания слова из ячейки 0 без его удаления и сдвига остальных слов. При использовании стека для запоминания параметров инициализации контроллеров каких-либо устройств ЭВМ обычно предусматривается возможность считывания содержимого любой ячейки стека без его удаления, т.е. считывание содержимого не только ячейки 0.

О первом слове, посылаемом в стек, говорят, что оно располагается на дне стека. О последнем посланном (по времени) в стек слове говорят, что оно находится в вершине стека. Таким образом, ячейка N-1 – дно стека, а ячейка 0 – вершина.

Обычно аппаратный стек снабжается счетчиком стека СчСт, показывающим общее количество занесенных в память слов (СчСт = 0 – стек пустой). При заполнении стека полностью он запрещает дальнейшие операции записи.

Стековый принцип организации памяти можно реализовать не только в специально предназначенных для этого устройствах. Стековая организация данных возможна и на обычной адресной памяти с произвольным обращением (программный стек). Для организации стека LIFO в этом случае необходима еще одна ячейка памяти (регистр), в которой всегда хранится адрес вершины стека и которая называется указателем стека. Обычно в качестве указателя стека используют один из внутренних регистров процессора. Кроме этого, требуется соответствующее программное обеспечение. Принципы стековой организации данных на обычной адресной памяти иллюстрируются схемой на рис. 4.5.

В отличие от аппаратного стека данные, размещенные в программном стеке, при записи нового числа или считывании не перемещаются. Запись каждого нового слова осуществляется в ячейку памяти, следующую по порядку за той, адрес которой содержится в указателе стека. После записи нового слова содержимое указателя стека увеличивается на единицу (см. рис. 4.5). Таким образом, в программном стеке перемещаются не данные, а вершина стека. При считывании слова из стека происходит обратный процесс. Слово считывается из ячейки, адрес которой находится в указателе стека, после чего содержимое указателя стека уменьшается на единицу.

Если вновь загружаемые в стек слова размещаются в ячейках памяти с последовательно увеличивающимися адресами, стек называют прямым. Если адреса последовательно убывают, то – перевернутым. В большинстве случаев используется перевернутый стек, что связано с особенностями аппаратной реализации счетчиков внутри процессора.

Чем удобна такая форма организации памяти? Забегая вперед, можно отметить, что любая команда, выполняемая в процессоре, в общем случае должна содержать код операции (КОП), адрес первого и второго операндов и адрес занесения результата. Для экономии памяти и сокращения времени выполнения машинной команды процессором желательно уменьшить длину команды. Пределом такого уменьшения является длина безадресной команды, т.е. просто КОП. Именно такие команды оказываются возможными при стековой организации памяти, так как при правильном расположении операндов в стеке достаточно последовательно их извлекать и выполнять над ними соответствующие операции.

Помимо рассмотренной выше стековой памяти типа LIFO в ЭВМ используются стековые памяти другого типа, реализующие правило: первый пришел – первый ушел. Стеки подобного типа принято называть стеками FIFO (First In – First Out). Такая стековая память широко используется для организации различного рода очередей (команд, данных, запросов и т.д.). Обобщенная структура аппаратного стека типа FIFO представлена на рис. 4.4, б.

Как и в предыдущем случае, ячейки стековой памяти образуют одномерный массив, в котором соседние ячейки связаны друг с другом разрядными цепями передачи слов. Запись нового слова, поступившего с ШИвх, осуществляется в верхнюю (нулевую) ячейку, после чего оно сразу перемещается вниз и записывается в последнюю по счету незаполненную ячейку. Если стек перед записью был пустой, слово сразу попадает в ячейку с номером N-1, т.е. на дно стека. Считывание возможно только из нижней ячейки с номером N-1 (дно стека). Основной режим – это считывание с удалением. При этом все последующие (записанные) слова сдвигаются вниз, в соседние ячейки, номера которых на единицу больше. При заполнении стека счетчик (СчСт) запрещает дальнейшие операции записи в стек.

Таким образом, в отличие от стека LIFO, в стеке FIFO перемещается не дно, а вершина. Записываемые в стек FIFO слова постепенно продвигаются от вершины ко дну, откуда и считываются по мере необходимости, причем темп записи и считывания определяются внешними управляющими сигналами и не связаны друг с другом.

Программная реализация стека FIFO в настоящем разделе не рассматривается, поскольку на практике используется достаточно редко.

Структуры адресных ЗУ. ЗУ типа 2D

Адресные ЗУ наиболее широко используются в современных ЭВМ для построения самых разнообразных устройств памяти. В процессе эволюции ЭВМ принципы построения и аппаратная реализация данных ЗУ прошли очень большой путь развития от первых ЗУ на электромагнитных реле до современных БИСов памяти емкостью в сотни Мбайт, которые в качестве ЗЭ используют либо разнообразные триггерные схемы на биполярных полупроводниках, либо МОП-структуры. При этом тип используемых ЗЭ влияет на структуру ЗУ. Кроме того, структура ЗУ во многом определяется особенностями его применения в конкретных устройствах ЭВМ. Все это привело к тому, что в процессе развития возникло весьма большое разнообразие структур ЗУ, которые различаются по способу организации, быстродействию, объему, аппаратурным затратам, стоимости.

Ранее отмечалось, что основной частью любой памяти является запоминающий массив (ЗМ), представляющий собой совокупность ЗЭ, соединенных определенным образом. ЗМ называют еще запоминающей матрицей. Каждый ЗЭ хранит бит информации и должен реализовывать следующие режимы работы:

хранение состояния (0 или 1);

выдачу сигнала состояния (считывание);

запись информации (0 или 1).

К ЗЭ должны поступать управляющие сигналы для задания режима работы, а также сигналы при записи. При считывании ЗЭ должен выдавать сигнал о своем состоянии, поэтому любой ЗМ имеет систему адресных и разрядных линий (проводников).

Адресные линии используются для выделения по адресу совокупности ЗЭ, которым устанавливается режим считывания или записи. Число ЗЭ, входящих в эту совокупность, равно ширине выборки. Иными словами, с помощью адресных линий происходит выбор необходимой ячейки памяти. Разрядные линии используются для записи или считывания информации в ЗЭ каждого разряда ячейки памяти.

Адресные и разрядные линии носят общее название линий выборки. В зависимости от числа таких линий, соединенных с одним ЗЭ, различают двух-, трехкоординатные ЗУ и т.д., называемые ЗУ типа 2D, 3D, 2.5D, 2D-M (от слова dimension – размерность), и их разнообразные модификации.

ЗУ типа 2D

Организация ЗУ типа 2D обеспечивает двухкоординатную выборку каждого ЗЭ ячейки памяти. Основу ЗУ составляет плоская матрица из ЗЭ, сгруппированных в 2k ячеек по n разрядов. Обращение к ячейке задается k-разрядным адресом, что дает одну координату. Выделение разрядов производится разрядными линиями записи и считывания, что дает вторую координату. Очень упрощенная структура ЗУ типа 2D представлена на рис. 4.6.

А дрес

из k разрядов поступает на блок адресной

выборки БАВ (который называют также

адресным формирователем), управляемый

сигналами Чт и Зап. Основу БАВ составляет

дешифратор с 2k

выходами, который при поступлении на

его вход адреса формирует сигнал для

выбора линии i. В зависимости от сигнала

Чт или Зап БАВ в общем случае выдает

сигнал, настраивающий ЗЭ i-й ячейки (i-й

линии) на чтение либо на запись. Выделение

разряда j в i-м слове (ЗУ серого цвета)

производится второй координатной

линией. При записи по линии j от БУЗ

поступает сигнал, устанавливающий

выбранный для записи ЗЭi,j

в состояние 0 или 1. При считывании на

БУС по линии j поступает сигнал о состоянии

ЗЭi,j.

дрес

из k разрядов поступает на блок адресной

выборки БАВ (который называют также

адресным формирователем), управляемый

сигналами Чт и Зап. Основу БАВ составляет

дешифратор с 2k

выходами, который при поступлении на

его вход адреса формирует сигнал для

выбора линии i. В зависимости от сигнала

Чт или Зап БАВ в общем случае выдает

сигнал, настраивающий ЗЭ i-й ячейки (i-й

линии) на чтение либо на запись. Выделение

разряда j в i-м слове (ЗУ серого цвета)

производится второй координатной

линией. При записи по линии j от БУЗ

поступает сигнал, устанавливающий

выбранный для записи ЗЭi,j

в состояние 0 или 1. При считывании на

БУС по линии j поступает сигнал о состоянии

ЗЭi,j.

Следует иметь в виду, что ЗЭ должны допускать объединение выходов для работы на общую линию с передачей сигналов только от выбранного ЗЭ. Это свойство ЗЭ используется во всех современных ЗУ.

Таким образом, каждая адресная линия выборки ячейки памяти в общем случае передает три сигнала:

выборка при записи;

выборка при считывании;

отсутствие выборки.

Однако во многих современных ЗУ достаточно только двух сигналов – выборка и отсутствие выборки.

Каждая разрядная линия записи передает в ЗЭ записываемый бит информации, а разрядная линия считывания – считываемый из ЗЭ бит информации. Линии записи и считывания могут быть объединены в одну при использовании ЗЭ, допускающих соединение выхода со входом записи. В современных ЗУ широко используются совмещенные функции линий считывания и записи.

ЗУ типа 2D являются быстродействующими и достаточно удобными для реализации. Однако такие ЗУ неэкономичны по объему оборудования из-за наличия дешифратора на 2k выходов. В настоящее время структуры типа 2D используются, в основном, в ЗУ небольшой емкости (не более 1 К).

ЗУ типа 3D

Для построения ЗУ больших объемов используют другую схему и другие типы ЗЭ, которые имеют не один, а два конъюнктивно связанных входа выборки. В этом случае адресная выборка осуществляется только при одновременном появлении двух сигналов. Использование таких ЗЭ позволяет строить ЗУ с трехкоординатным выделением ЗЭ. Итак, ЗУ типа 3D отличается от 2D тем, что к каждому ЗЭ подходят три линии выборки: две координатные и одна разрядная.

Запоминающий

массив ЗУ типа 3D представляет собой

пространственную матрицу, составленную

из n плоских матриц. Каждая плоская

матрица представляет собой ЗМ для

запоминания j-х разрядов всех слов, т.е.

запоминающие элементы для одноименных

разрядов всех хранимых в ЗУ чисел

сгруппированы в квадратную матрицу из

![]() рядов по

ЗЭ в каждом. Это означает, что к записи

или считыванию готов только тот элемент,

для которого сигналы адресной выборки

по координатам X и Y совпали. Для адресной

выборки ЗЭ в плоской матрице необходимо

задать две его координаты в ЗМ.

рядов по

ЗЭ в каждом. Это означает, что к записи

или считыванию готов только тот элемент,

для которого сигналы адресной выборки

по координатам X и Y совпали. Для адресной

выборки ЗЭ в плоской матрице необходимо

задать две его координаты в ЗМ.

Структура матрицы j-го разряда в ЗУ типа 3D представлена на рис. 4.7. Код адреса i-й ячейки памяти разделяется на старшую и младшую части, каждая из которых поступает на свой адресный формирователь. Адресный формирователь БАВ1 выдает сигнал выборки на линию i', а БАВ2 – на линию i''. В результате в ЗМ оказывается выбранным ЗЭ, находящийся на пересечении этих линий (двух координат), т.е. адресуемый кодом i=i' / i'' (ЗЭ серого цвета). Адресные формирователи управляются сигналами Чт и Зап и в зависимости от них выдают сигналы выборки для считывания или для записи. При считывании сигнал о состоянии выбранного ЗЭ поступает по j-линии считывания к БУС (третья координата ЗЭ при считывании). При записи в выбранный ЗЭ будет занесен 0 или 1 в зависимости от сигнала записи в j-й разряд, поступающего по j-й линии от БУЗ (третья координата ЗЭ при записи). Для полупроводниковых ЗУ характерно объединение в одну линию разрядных линий записи и считывания.

Для построения n-разрядной памяти используется n матриц рассмотренного вида. Адресные формирователи здесь могут быть общими для всех разрядных ЗМ.

Запоминающие

устройства типа 3D более экономичны по

оборудованию, чем ЗУ типа 2D. Действительно,

сложность адресного формирователя с m

входами пропорциональна 2m,

отсюда сложность двух адресных

формирователей ЗУ типа 3D, пропорциональная

![]() ,

значительно меньше сложности адресного

формирователя ЗУ типа 2D, пропорциональной

2k.

Поэтому структура типа 3D позволяет

строить ЗУ большего объема, чем структура

2D.

,

значительно меньше сложности адресного

формирователя ЗУ типа 2D, пропорциональной

2k.

Поэтому структура типа 3D позволяет

строить ЗУ большего объема, чем структура

2D.

С труктура

типа 3D является наиболее удобной для

построения статических ЗУ на многоэмиттерных

биполярных транзисторах.

труктура

типа 3D является наиболее удобной для

построения статических ЗУ на многоэмиттерных

биполярных транзисторах.

Динамическая память

Элемент памяти, микросхема памяти, модуль памяти, графическая память

Динамическая память - DRAM (Dynamic RAM) - получила свое название от принципа действия элемента памяти, хранящего один бит информации. Запоминающим элементом служит конденсатор, являющийся емкостью перехода исток - сток полевого транзистора. При записи логической единицы в элемент памяти конденсатор заряжается, при записи нуля - разряжается. При чтении информации конденсатор тоже разряжается и, если заряд был не нулевым, усилитель считывания устанавливает на выходе единичное значение потенциала, и конденсатор специальной схемой перезаписи снова заряжается до потенциала логической единицы. При отсутствии обращения к элементу динамической памяти со временем, за счет токов утечки, конденсатор разряжается и информация теряется, поэтому такая память требует постоянного периодического перезаряда конденсаторов методом перезаписи каждого элемента (регенерации). Следовательно, память может работать только в динамическом режиме, с постоянным перезарядом конденсаторов ячеек памяти. Этим она принципиально отличается от статической памяти, реализуемой на триггерных ячейках и хранящей информацию без обращений к ней статично, сколь угодно долго при включенном питании. Благодаря относительной простоте ячейки динамической памяти, на одном кристалле удается размещать миллионы ячеек и получать сравнительно недорогую полупроводниковую память, пускай и недостаточно высокого быстродействия, но с умеренным энергопотреблением. Используется динамическая память в качестве оперативной памяти компьютера и оперативной памяти видеоадаптера.

Работа запоминающего элемента динамической памяти

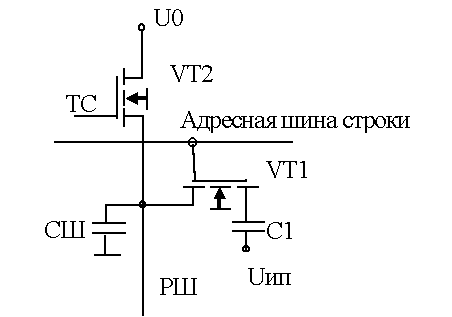

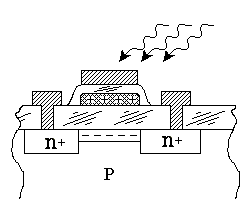

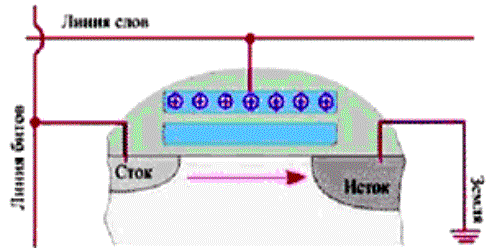

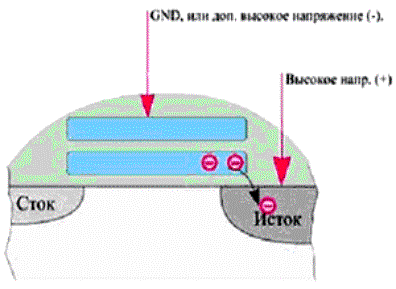

Микросхема динамической памяти состоит из миллионов элементов, каждый из которых хранит всего один бит информации. На физическом уровне элементы памяти объединяются в прямоугольную матрицу, горизонтальные линейки элементов называются строками (ROW), а вертикальные - столбцами (Column). Элементы всей строки матрицы могут считываться в современных микросхемах динамической памяти в буферный регистр - этот набор ячеек принято называть страницей (Page). Из-за высокой интеграции микросхем памяти становится невозможным обратиться к ячейке памяти, установив на шине адреса адрес ячейки памяти полностью. Слишком много разрядов должна иметь эта шина. Поэтому шину адреса делают в два раза уже и устанавливают адрес дважды. Сначала адрес строки, затем адрес столбца. Чтобы различать, установка какой части адреса происходит вводятся дополнительные сигналы управления RAS и CAS. Адрес строки передается по шине адреса и принимается в регистр адреса строки микросхемы памяти по спаду импульса RAS (Row Access Strobe). Адрес колонки передается по этой же шине и принимается в регистр адреса колонки микросхемы памяти по спаду импульса CAS (Column Access Strobe). На пересечении линии строки и колонки находится элемент памяти. Поскольку обращение (запись или чтение) к различным ячейкам памяти обычно происходит в случайном порядке, то для поддержания сохранности данных производится регулярная регенерация (Memory Refresh - "освежение" памяти) - регулярный циклический перебор ячеек памяти с холостыми циклами перезаписи. Регенерация в микросхеме происходит одновременно по всей строке матрицы при обращении к любой из ее ячеек. Если динамическая память используется в видеобуферах графических адаптеров, то специальных циклов регенерации такая память не требует т.к. частота ее чтения для воспроизведения изображения на экране видеомонитора вполне достаточна для сохранения информации при чтении и сопровождающей чтение перезаписи. Частоту регенерации можно определить следующим образом, если ток утечки составляет 0.1 нА, а емкость конденсатора порядка 0,1 пф, время разряда конденсатора на 1 вольт произойдет за время t порядка одной миллисекунды. Если считать такое падение напряжения максимально допустимым, то для выдачи состояния низкого или высокого уровня необходимо осуществлять периодическое восстановление информации (или ее регенерацию) с периодом t ref <=1мс. Таким образом, максимальный период обращения к каждой строке TRF (refresh time) для гарантированного сохранения информации должен быть менее 1мс. Микросхемы динамической памяти строятся на основе биполярных МОП- транзисторов. Элемент динамической памяти на МОП- структурах показан на рис.1. В основе запоминающего элемента лежит один конденсатор С1 и один МОП- транзистор VT1. На схеме конденсатор показан в виде отдельного элемента, хотя реально его функции выполняет емкость затвор-подложка. Транзистор VT2 открывается сигналом ТС=1 и от источника U0 емкость СШ заряжается до напряжения U0.

Рис.1. Элемент динамической памяти на МОП- структурах.

При выборке данных транзистор VT1 выполняет функции ключа: при подаче сигнала на шину адреса строки он открывается и соединяет запоминающий конденсатор С1 с шиной столбца РШ (разрядной шиной). Емкость запоминающего конденсатора 0.1-0.2 пф, что значительно меньше емкости конденсатора шины (СШ), поэтому возникает незначительное изменение потенциала шины, которое усиливается при считывании информации высокочувствительными дифференциальными усилителями. На вход дифференциального усилителя подается напряжение разрядной шины и опорное напряжение для определения разности. Опорный элемент построен аналогично запоминающему, он поддерживает опорное напряжение U0. В каждом столбце матрицы памяти расположены усилители, к которым подключаются элементы памяти и элементы, поддерживающие опорное напряжение. Считан может быть сигнал только с одного элемента памяти столбца, ключи остальных элементов в это время закрыты, но открыты все элементы строки. При этом заряды всей строки поступают на усилители и через некоторое время могут быть считаны. Такая операция называется активизацией строки. Сигнал с выхода чувствительного дифференциального усилителя подается на формирующий выходной сигнал триггер-усилитель, выполняющий также функции элемента, который автоматически осуществляет регенерацию информации. Еще раз подчеркнем, что регенерация информации в рассматриваемой схеме производится сразу во всей строке. Считывание информации происходит при при установке сигнала Read на шине управления, при директиве Write происходит запись информации. Пока строка остается активной, возможны считывание или запись и других ячеек памяти. После того, как истекает время активности строки происходит закрытие строки, которое сопровождается подзарядкой (Precharge) элементов памяти строки. Последующее считывание данных этой строки невозможно без ее повторной активизации (установки адреса строки). Микросхема динамической памяти

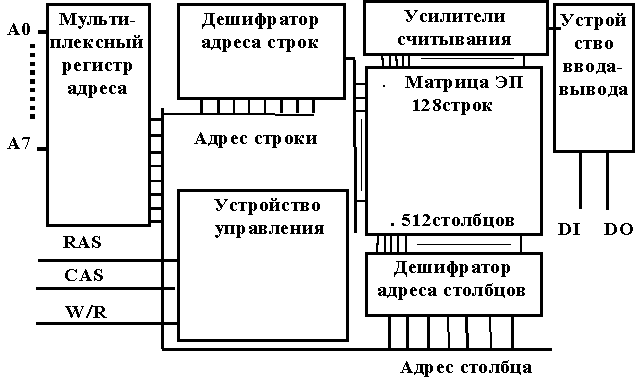

Главные особенности микросхем динамической памяти заключаются в следующем:

отсутствуют источники для питания элементов запоминающих ячеек;

необходимы логические схемы, обеспечивающие регенерацию информации;

максимально проста схема накопителя, обеспечивающая минимум занимаемой площади;

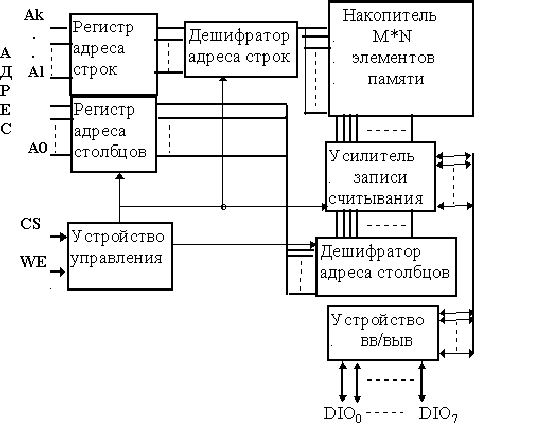

мала потребляемая мощность, поскольку динамический запоминающий элемент не потребляет тока в отрезки времени, когда к нему не происходит обращение. Для формирования внутренних сигналов, управляющих включением и выключением в определенной последовательности различных узлов микросхемы, в структуре микросхемы предусмотрена схема управления. Входные, выходные и управляющие сигналы микросхемы памяти: RAS (Row Adress Strobe) - строб адреса строки; CAS (Column Adress Strobe) - строб адреса столбца; W/R (запись/чтение); вход данных - DI; выход данных - DO. Микросхема имеет усилители считывания и регенерации в каждом столбце матрицы, регистр адреса, дешифраторы адреса строк и адреса столбцов, устройство управления и устройство ввода и вывода данных. Структура микросхемы приведена на рис.2.

Рис.2. Структура микросхемы динамической памяти

На линиях RAS (row address strobe - строб адреса строки) и CAS (column address strobe - строб адреса столбца) в спокойном состоянии поддерживается высокий уровень сигнала, что означает, что никакой информации на адресных линиях нет и никаких действий, связанных с чтением или записью данных. В случае строчной регенерации, регенерация информации осуществляется путем обращения к каждой строке динамической памяти перебором строчных адресов в любом режиме работы. В современных микросхемах памяти регенерацию производит устройство регенерации, встроенное в микросхему памяти. Нарушение режима регенерации может привести к нарушению логических состояний микросхем памяти. Поэтому в схемах регенерации применяются защитные схемы, поддерживающие истинность логических состояний элементов матрицы микросхемы памяти совместно с генератором циклов регенерации. Микросхема подключается к шине адреса и данных. Линии адреса служат для выбора адреса ячейки памяти, а линии данных - для чтения или записи данных в память. Низкий уровень сигнала W/R готовит микросхему к считыванию состояния шины данных и записи полученной информации в соответствующую ячейку, а высокий, наоборот, заставляет считать содержимое ячейки и установить его на линиях шины данных. Использование одной и той же шины данных для вывода данных и для чтения данных позволяет в два раза уменьшить количество выводов шины данных. Это, как и уменьшение ширины шины адреса позволяет уменьшить размеры микросхемы, а значит, получить более высокие рабочие частоты. Рассмотрим, какие факты мешают повышению рабочей частоты микросхемы памяти: 1. Скорости распространения электрических сигналов ограничены, поэтому длины проводников, подведенных к различным ножкам микросхемы, не должны сильно отличаться друг от друга, иначе сигнал от одного вывода будет опережать сигнал от другого. 2. Длины проводников не должны быть очень велики, задержка распространения сигнала не позволит повысить быстродействие. 3. Любой проводник действует как приемная и как передающая антенна, создавая помехи. Уровень помех резко усиливается с ростом тактовой частоты. 4. Любой проводник обладает электрической емкостью. Чем больше емкость, тем меньше скорость передачи данных. Совмещение выводов шины для вывода и ввода данных увеличивает скорость обмена с памятью, но не позволяет осуществлять чтение и запись одновременно. Интересно, что в первых компьютерах специальная схема приостанавливала (прерывала) работу процессора на время регенерации, для управления процессом регенерации. На рис.2 приведена микросхема асинхронной динамической памяти, в которой разрядность данных - 1 бит. Далее мы узнаем как совершенствовалась память и чем отличается синхронная динамическая память от асинхронной. А сейчас поговорим об организации микросхем памяти и построении модулей памяти. Микросхемы памяти могут иметь и другую организацию. Например, распространенные (2006г.) микросхемы (чипы) синхронной динамической памяти DDR SDRAM фирмы Samsung : K 4 H 5 6 0 8 3 8 E — T C B 3 (рис.3) имеют емкость 36 мегабайт (256 мегабит). Адресуемая ячейка памяти чипа 8 битная.

Рис.3. Микросхема памяти DDR SDRAM фирмы Samsung

Для того, чтобы исключить ожидания при регенерации считанных данных, современные микросхемы памяти имеют несколько матриц. Последовательные обращения к данным при чтении будут происходить без задержек, если последовательные ячейки памяти расположены на разных матрицах. Таким образом можно избежать задержек на регенерацию при чтении последовательных данных. Рассматриваемая нами микросхема имеет 4 матрицы (допускает при построении модуля памяти использование четырех банков памяти).

Организация модуля памяти

Память, устанавливаемая в слоты (разъемы) расширения памяти персонального компьютера или других вычислительных систем, изготавливается в виде отдельных модулей. Модуль - маленькая печатная плата на которой размещены микросхемы памяти. На рис. 4 показан DIMM модуль памяти емкостью 256 мегабайт, построенный на микросхемах (чипах) K 4 H 5 6 0 8 3 8 E — T C B 3 (рис.3). 8 таких чипов устанавливается на одном модуле DDR DIMM и дают его полную емкость в 256 мегабайт.

Рис. 4. DDR DIMM модуль емкостью 256 мегабайт

Абревиатура DIMM (Dual In-Line Memory Module) означает - модуль памяти с двойным выводом контактов. DIMM модули имеют 64-х битные шины адреса и данных. Используя DIMM модули можно устанавливать всего одну плату памяти, так как чередование блоков памяти обеспечивается внутренней структурой микросхем. Организация микросхемы памяти K 4 H 5 6 0 8 3 8 E — T C B 3 8 бит - это разрядность ячейки памяти, следовательно восемь установленных на DIMM модуле микросхем обеспечивают в сумме 64 бита шины данных для всего модуля DDR DIMM. В микросхеме имеется четыре внутренних банка памяти, поэтому и модуль памяти имеет 4 банка памяти. Микросхемы (и модуль) требуют 2,5 вольт питания. DDR (Double Data Rate) - сокращение от Double Data Rate-Synchronous DRAM (синхронная DRAM с двойной скоростью передачи данных), тип синхронной памяти SDRAM. Она осуществляет пересылку данных два раза за такт – по восходящему и нисходящему фронту стробирующего синхросигнала , что удваивает скорость предачи данных. SDRAM (Synchronous DRAM) означает, что это микросхема синхронной динамической памяти, работающая синхронно с частотой работы центрального процессора, в результате чего исключаются режимы ожидания (простоя процессора). Время доступа к данным микросхемы K 4 H 5 6 0 8 3 8 E — T C B 3 составляет 6 нс., т.к. память синхронная, то обращение к данным происходит каждый такт, следовательно это память DDR 333. Она работает на частоте (1/6)109 = 166 МГц , пропускная способность памяти с учетом DDR определится так : ( (2*166) * 64) =21 Гбит/сек., или ((2*166)*8)= 2,6 Гбайт/сек.

Графическая память Для установки на видеокарты используется графическая DDR SGRAM память (рис.4).

Рис. 4. Микросхема графической DDR SGRAM памяти

128-мегабитный чип организация чипа х32 (32 разряда в слове), чип имеет 4 банка внутренней памяти. 2,5 В - напряжение питания чипа. 2,86 нс. - время доступа к данным. Рабочая частота составляет 350 МГц ( частота передачи данных — 700 МГц, т.к. память DDR).

Динамическая память FPM DRAM (Fast Page Mode ), временные диаграммы страничного чте6ния и записи

С увеличением частоты процессора, все более жесткие требования предъявляются к временным характеристикам памяти. В запоминающем устройстве, работавшем с процессором 80386 (16 МГц), время выборки данных соответствовало двум циклам процессора, т.е. составляло 2 х 62,5 нс. = 125 нс. Это означало, что для работы без периодов ожиданий достаточно было иметь запоминающее устройство с временем выборки 100 или даже 120 нс. Однако каждый раз, когда процессор осуществлял выборку данных из динамического запоминающего устройства требовалась перезапись содержимого памяти до того, как ее снова можно будет использовать. Для большинства динамических запоминающих устройств время перезаписи лишь немного меньше, чем время выборки. Кроме того, в динамических запоминающих устройствах требуется периодическая регенерация хранимой в памяти информации. На регенерацию уходит время, составляющее в среднем 6-12% от времени выборки. С учетом указанных обстоятельств фактическое быстродействие динамических запоминающих устройств определялось как время выборки 100 нс. + время перезаписи 90 нс. + дополнительное время на регенерацию. В сумме это составляло более 200 нс. А это означает, что в персональных компьютерах даже на базе микропроцессора 80386 с временем цикла 125 нс. применение динамического запоминающего устройства с временем выборки 100 нс. не позволяло обеспечить работу процессора с памятью без периодов ожиданий. Современные схемы динамической памяти имеют время выборки порядка 5 - 10 нсек., но по прежнему не могут обеспечить работу процессора без периодов ожидания, так как тактовая частота процессоров уже превышает 4 ГГц (длительность такта менее 0,25нсек.). Повышение быстродействия памяти достигается сегодня благодаря совершенствованию технологий и схемных решений. Обеспечение необходимого быстродействия системы процессор - память становится все более важным. Существует несколько способов повышения быстродействия системы процессор - память:

1. Расположить последовательные ячейки памяти в разных банках памяти;

2. Реализовать метод страничной выборки, который заключается в том, что при обращении к памяти задается адрес страницы (строки), а не отдельной ячейки памяти;

3. Организовать синхронную работу памяти и процессора за счет использования внутренней конвейерной архитектуры;

4. Включить в строку динамической памяти встроенный статический КЭШ;

5. Увеличить ширину шины;

6. Повысить тактовую частоту шины и увеличить время в тактах, в течение которого данные доступны для чтения.

При использовании первого метода уменьшение времени обращения к памяти достигается при помощи метода interleaving (чередование), суть которого заключается в том, что в подсистеме памяти организуется последовательное обращение к разным банкам памяти. В системных платах для 386 и 486 процессоров использовался контроль четности. Для выявления одиночной ошибки количество единиц в каждом байте дополнялось до четного значения. Поэтому модули памяти выпускались с дополнительным разрядом шины данных, отведенным для контроля четности. В типичных настольных персональных компьютерах контроль четности оказался избыточным и производители микросхем отказались от такого контроля. Модули DIMM допускают работу с современными процессорами при установке даже нечетного числа модулей, т.к. каждый DIMM модуль может включать в себя несколько банков памяти. В простейшей модели динамического ОЗУ имеются два банка: в одном банке размещены все байты с четными адресами, в другом с нечетными. Периодов ожидания не будет, если процессор выполняет команды, извлекаемые из последовательных адресов памяти. Если программа становится непоследовательной, такая ситуация возникает, например, когда имеют место условные или безусловные переходы, вероятность готовности банка к работе становится равной 50%. При последовательном переборе адресов, когда схема управления памятью находится в режиме ожидания данных, считываемых по следующему адресу памяти из первого банка, она устанавливает адрес данных во втором банке. Следующий адрес может считываться немедленно без периода ожидания. Если микропроцессор считывает 10 последовательных участков памяти, требуется один период ожидания только для первого считывания. В результате, среднее число периодов ожидания на весь цикл считывания будет равно 0,1. Подобная архитектура памяти обеспечивает работу динамического ОЗУ с быстродействующими процессорами, но при этом усложняется устройство управления памятью, что связано с необходимостью организации работы банков. Традиционный разрыв между скоростью работы памяти и процессора сокращается за счет внедрения новых технологий производства СБИС памяти. Долгое время наиболее распространенной была память, работающая в режиме быстрого страничного обмена (Fast Page Mode, или FPM DRAM). Эта память отличается тем, что после выбора строки удерживается сигнал RAS и допускается многократная установка адреса столбца по сигналу CAS, что позволяет организовать блочную передачу данных всей строки матрицы памяти, называемой страницей обмена. Из предыдущего описания работы элемента и микросхемы памяти мы знаем, что столбцы и строки матрицы памяти адресуются при помощи единых адресных линий. В случае квадратной матрицы количество адресных линий сокращается вдвое, но и выбор конкретной ячейки памяти отнимает вдвое больше тактов, ведь номера столбца и строки приходится передавать последовательно. Причем, возникает неоднозначность, что именно в данный момент находится на адресной линии: номер строки или номер столбца? Решение этой проблемы потребовало двух дополнительных выводов, сигнализирующих о наличии столбца или строки на адресных линиях RAS и CAS. Контроллер преобразует физический адрес ячейки памяти в номер строки и номер столбца, а затем посылает первый из них на адресные линии. Дождавшись, когда адресные сигналы стабилизируются, контроллер устанавливает низкий уровень на линии RAS, сообщая микросхеме памяти о наличии информации на линии. Микросхема считывает этот адрес и подает на соответствующую строку матрицы электрический сигнал. Все транзисторы, подключенные к этой строке, открываются и напряжения с конденсаторов подаются на входы чувствительных усилителей. Чувствительный усилитель строки сохраняет полученную информацию в специальном буфере. Когда микросхема завершает чтение строки в буфер и вновь готова к приему информации, контроллер подает на адресные линии номер колонки и, дав сигналам адреса колонки стабилизироваться, устанавливает на линии CAS низкий уровень. Устройство управления микросхемы памяти преобразует номер колонки в смещение ячейки внутри буфера. Остается установить уже подготовленные данные на линиях шины данных. Это занимает еще какое-то время, в течение которого контроллер ждет запрошенную информацию. На финальной стадии цикла обмена контроллер считывает состояние линий данных, cнимает сигналы RAS и CAS, устанавливая высокий потенциал, а микросхема становится недоступной на время восстановительной перезаписи строки и необходимую регенерацию. Задержка между подачей номера строки и номера столбца называется "RAS to CAS delay" ( tRCD). Задержка между подачей номера столбца и получением содержимого ячейки на выходе "CAS delay" ( tCAC), а задержка между чтением последней ячейки и подачей номера новой строки "RAS precharge" (tRP).

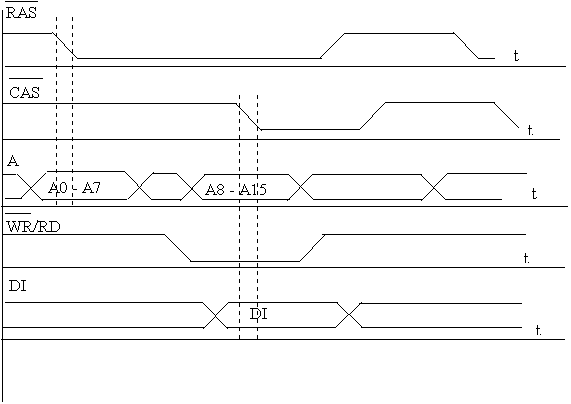

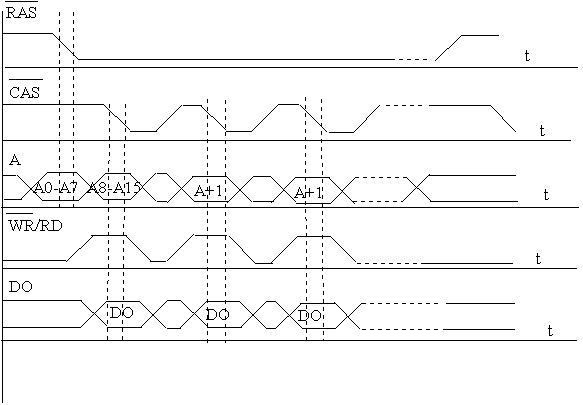

Рассмотрим работу микросхемы памяти при чтении/записи одного слова (рис.1). На шине адреса контроллер памяти установил адрес строки, затем сигнал RAS, по перепаду адрес принят микросхемой памяти и контроллер памяти устанавливает адрес столбца на шине адреса, затем сигнал CAS, по которому адрес столбца будет принят микросхемой памяти. В результате будет получен доступ к ячейке памяти, которая находится на пересечении строки и столбца. По сигналу WR/RD данные будут прочитаны, или записаны в ячейку памяти. На установку и прием каждого адреса необходимо 3 такта системной шины. Поэтому доступ к данным возможен только после 6 тактов системной шины.

Рис.1. Временная диаграмма режима записи/чтения одного слова (при чтении на линии WR/RD высокий потенциал).

Страничное чтение производится при активизации строки за счет удержания сигнала RAS. Строка остается активной на все время чтения страницы памяти ( четырех последовательно расположенных слов), что увеличивает скорость чтения из памяти. Например цикл чтения в пакетном режиме четырех ячеек памяти типа FPM может выполняться с затратой шести тактов (установка и дешифрация адреса строки, установка и дешифрация адреса столбца) на чтение первого слова и трех тактов на каждое из следующих трех слов. (рис.2).

Рис. 2. Временные диаграммы страничного режима записи (чтения).

При работе с обычной DRAM (рис.1) после считывания данных сигнал RAS деактивируется, подготавливая микросхему к новому циклу обмена. В памяти FPM-DRAM контроллер удерживает сигнал RAS в низком состоянии, избавляясь от повторной пересылки номера строки. Строб (импульс) CAS сопровождает установку каждого слова строки (выбор столбца). При последовательном чтении ячеек памяти время доступа сокращается т.к. обрабатываемая строка находится во внутреннем буфере микросхемы, и обращаться к матрице памяти нет необходимости. Если последовательно поступают запросы запросы на чтение данных из ячеек, принадлежащих разным страницам, то страничная память не дает выигрыша и работа FPM-DRAM происходит в режиме обычной DRAM. Если очередная запрашиваемая ячейка лежит вне текущей (так называемой, открытой) строки, контроллер вынужден деактивировать RAS, выдержать паузу RAS precharge на регенерацию микросхемы, передать номер строки, выдержать паузу RAS to CAS delay и лишь затем приступить к передаче номера столбца. Ситуация, когда запрашиваемая ячейка находится в открытой строке, называется "попаданием на страницу" (Page Hit), в противном случае говорят, что произошел промах (Page Miss). Непостоянство времени доступа затрудняет измерение производительности микросхем памяти и сравнение их скоростных показателей друг с другом. В худшем случае время обращения к ячейке памяти (Tобр) составляет: Tобр= (RAS to CAS Delay + CAS Delay + RAS precharge) нс. В лучшем случае, если строка активна: Tобр= CAS Delay нс. Если память готова к обращению и не требует регенерации: Tобр= ( RAS to CAS Delay + CAS Delay) нс.

Таким образом, оценка производительность микросхемы требует для своего выражения как минимум трех чисел. Производители микросхем обычно приводят только два значения - время полного доступа (RAS to CAS Delay + CAS Delay); и время рабочего цикла, время доступа к ячейке открытой строки (CAS Delay). Время, необходимое для регенерации микросхемы (RAS precharge), из полного времени доступа обычно исключено. Оно указывается лишь в технической документации, где приводятся все временные значения. К середине девяностых годов, когда широко использовалась FPM DRAM среднее значение RAS to CAS Delay составляло порядка 30 нс., CAS Delay - 40 нс., а RAS precharge - менее 30 нс. При частоте системной шины в 60 МГц (1такт ~17 нс.) когда на открытие и доступ к первой ячейке страницы уходило около 6 тактов, а на доступ к остальным ячейкам открытой страницы - около 3 тактов была введена схематическая запись, получившая название формулы памяти 6-3-x-x. На первом месте этой формулы записывается время обращения к микросхеме памяти ( RAS to CAS Delay + CAS Delay) выраженное в тактах системной шины, три последующих значения - время цикла CAS Delay, так же выраженное в тактах системной шины. Повышение быстродействия памяти достигается сегодня благодаря совершенствованию схемных решений. Разрыв между скоростью работы памяти и процессора сократился за счет внедрения новых технологий производства СБИС памяти о которых мы поговорим далее.

Развитие новых технологий организации динамической памяти

Формула памяти позволяет проводить сравнение различных микросхем динамической памяти друг с другом. В микросхемах памяти со страничным чтением практическое значение имеет сравнение лишь времени рабочего цикла. Совершенствуя ядро памяти, производители сократили время цикла до 30 нс., но скоростные характеристики динамической памяти все еще не обеспечивали работы процессора без режимов ожидания. Дальнейшее усовершенствование памяти было связано с усовершенствованием вывода данных на шину данных. Была разработана память нового типа EDO-DRAM. EDO-DRAM (Extended Data Out DRAM) - память с усовершенствованным выходом. Если оснастить микросхему специальным регистром-защелкой, сохраняющим данные после снятия сигнала CAS, станет возможным деактивировать CAS до окончания чтения данных, подготавливая в это время микросхему к приему номера следующего столбца. Это позволяет выиграть один такт системной щины. При работе EDO памяти, как и в FPM памяти, активизируется строка памяти, затем столбец, но выходной буфер не блокируется, а остается активным до начала следующего цикла чтения, при этом устраняется состояние ожидания процессора и цикл чтения сокращается от 6-3-3-3 до 5-2-2-2, таким образом экономится четыре такта при передаче пакета из четырех слов. Продолжительность рабочего цикла EDO-DRAM сократилась до 20 нс. прирост производительности (в сравнении с FPM-DRAM) составлял около 30%. Память EDO проста в реализации, стоимость ее производства возросла незначительно по сравнению с динамической памятью типа FPM. Дальнейшее улучшение характеристик памяти было связано с использованием сверхбыстрого страничного режима в памяти BEDO DRAM Burst EDO DRAM (BEDO DRAM) - улучшенная пакетная память со сверхбыстрым страничным режимом. Если программные приложения производят обмен с памятью пакетами из четырех циклов обращения к памяти, то после нахождения первого адреса в памяти BEDO DRAM, три остальные устанавливаются микросхемой памяти. На кристалле памяти расположен счетчик, осуществляющий слежение за следующим адресом и две ступени конвейера (два регистра), позволяющие цикл страничного доступа разделить на две части. При чтении данные выдаются на выходную ступень конвейера и устанавливаются на шине данных. Быстрый доступ к данным достигается за счет того, что данные заранее готовятся к выдаче на первой ступени конвейера и для выдачи следующего слова достаточно одного тактирующего сигнала. Применение технологии BEDO-DRAM позволило получить двукратное увеличение производительности. Добавив в микросхему генератор номера столбца, конструкторы ликвидировали задержку CAS Delay, сократив время цикла до 15 нс. После обращения к произвольной ячейке микросхема BEDO автоматически, без указаний со стороны контроллера, увеличивает номер столбца на единицу, не требуя его явной передачи. из-за ограниченной разрядности адресного счетчика ( два бита) максимальная длина пакета не могла превышать четырех последовательных ячеек. Формула памяти для BEDO-DRAM выглядит так: 5-1-1-1, что на ~40% быстрее EDO-DRAM. Несмотря на скоростные показатели (время рабочего цикла составляло 15 нс. - 1 такт для системной шины, работающей на частоте 66 MГц), память BEDO-DRAM оказалась не конкурентоспособной и не получила широкого распространения. Но принципы ее организации были использованы при проектировании нового типа памяти - синхронной динамической памяти. Причина перехода к синхронной памяти в том, что BEDO, как и все ее предшественники, оставаясь асинхронной памятью не может обеспечить высокой скорости обмена данными за счет несогласованности ее работы с системной шиной. Так как тактовая частота контроллера памяти и микросхемы памяти не синхронизованы, нет никаких гарантий, что начало рабочего цикла микросхемы памяти совпадет с началом такового импульса контроллера, вследствие чего рабочий цикл микросхемы памяти не совпадает с началом тактового импульса. Несколько наносекунд уходит на формирование контроллером управляющих сигналов RAS или CAS, за счет чего они также не совпадают с началом тактирующих импульсов. Еще несколько наносекунд требуется для установления сигнала и реакции на него микросхемы. Сколько именно дополнительного времени потребуется на это заранее определить невозможно, т.к. на результат влияет температура, длина проводников, наведенные помехи и т.д. Стандартная, асинхронная DRAM работала без управления ввода таймером, который не требовался для передачи данных вплоть до второго десятилетия развития микропроцессоров. В системах с более быстрыми процессорами, которые использовали стандартную DRAM необходимо было принудительно устанавливать состояния ожидания (временные задержки), чтобы согласовать скорость работы процессора с памятью. Состояние ожидания, это когда микропроцессор приостанавливает исполнение программы, так как не получил из памяти необходимый программный код.

SDRAM (Synchronous DRAM) - синхронная динамическая память Появление вычислительных систем с системными шинами, работающими на частоте 100 MГц привело к пересмотру механизма управления памятью. Была разработана синхронная динамическая память - SDRAM (Synchronous-DRAM). Микросхемы SDRAM памяти работают синхронно с системной шиной, в них реализован усовершенствованный пакетный режим обмена. Контроллер может запросить одну или несколько последовательных ячеек памяти, или всю строку целиком. Для выполнения такой операции требуется адресный счетчик, не ограниченный двумя битами, как в BEDO-DRAM. Количество (матриц) банков памяти в SDRAM увеличено с одного до двух или даже четырех. Это позволяет обращаться к ячейкам одного банка, осуществляя регенерацию другого, что вдвое увеличивает предельно допустимую тактовую частоту. Помимо этого появилась возможность одновременного открытия двух (четырех) страниц памяти, причем открытие одной страницы (т.е. передача номера строки) может происходить во время считывания информации с другой, что позволяет обращаться по новому адресу столбца ячейки памяти на каждом тактовом цикле. В отличие от всех видов асинхронной памяти, выполняющих перезапись ячеек памяти при закрытии страницы (т.е. при деактивации сигнала RAS), синхронная память проделывает эту операцию автоматически, позволяя держать страницы открытыми сколь угодно долго. Разрядность шины данных увеличилась с 32 до 64 бит, что еще вдвое увеличило производительность синхронной памяти. Формула чтения произвольной ячейки из закрытой строки для SDRAM обычно выглядит так: 5-1-1-1, а из открытой строки так: 3-1-1-1. Синхронизация операций в памяти тактовыми сигналами процессорной шины упрощает реализацию интерфейсов и уменьшает время обращения к столбцу. Режим обмена данными с SDRAM программируется при помощи внутри кристального регистра режима. При программировании задается длина пакета и запаздывание, что позволяет произвести оптимальную настройку системы обмена процессор - память. Корпорация NEC ввела новую технологию памяти - VCM (Virtual Channel Memory), повышающую производительность вычислительных систем приблизительно на 20%. Изменилась внутренняя конструкция модуля памяти. Единственный внутренний канал модуля памяти расщепляется на множество виртуальных, информация образует очередь. Наиболее простой VCM- чип представляет собой 64 мегабитную SDRAM, включающую 16 виртуальных каналов памяти. Синхронная динамическая память SDRAM, в отличие от стандартной и асинхронной DRAM, имеет внутренний таймер ввода данных. Системный таймер, который пошагово контролирует деятельность микропроцессора, управляет и работой SDRAM. Свойства SDRAM:

синхронное функционирование,

чередование банков ячеек,

возможность работы в пакетно-конвейерном режиме

Конвейерная адресация позволяет осуществлять доступ к запрошенным вторыми данными, до завершения обработки запрошенных первыми данными. Следующий шаг в развитии SDRAM - DDR SDRAM или SDRAM II.

DDR SDRAM (Double Data Rate SDRAM) или SDRAM II Эта синхронная память может передавать данные по переднему фронту и спаду сигнала синхронизации шины, что позволило увеличить пропускную способность до 1.6 Гб/сек при частоте шины в 100MHz. Пропускная способность памяти увеличилась вдвое по сравнению с ранее существовавшей SDRAM. Synchronous DRAM II, или DDR (Double Data Rate - удвоенная скорость передачи данных) основана на тех же самых принципах, что и SDRAM, однако включает некоторые усовершенствования, позволяющие увеличить быстродействие. Основные отличия от стандартного SDRAM: 1. используется синхронизация по фронту и по спаду, отсутствующая в SDRAM; 2. DDR использует DLL (delay-locked loop - цикл с фиксированной задержкой) для выдачи сигнала DataStrobe, означающего доступность данных на выходных контактах. Используя один сигнал DataStrobe на каждые 16 выводов данных, контроллер памяти может осуществлять доступ к данным более точно и синхронизировать данные, поступающие из разных модулей памяти, находящихся в одном банке. DDR фактически увеличивает скорость доступа вдвое, по сравнению с SDRAM, используя при этом ту же частоту, т.к. позволяет читать данные по восходящему и падающему уровню, выполняя два доступа за время одного обращения стандартной SDRAM. Дополнительно, DDR может работать на большей частоте благодаря замене сигналов TTL уровня (порядка 4В) на сигналы более низких уровней SSTL3 (порядка 1,8 B).

Память типа SLDRAM, (SyncLink) продукт DRAM-консорциума, является ближайшим конкурентом Rambus. Этот консорциум объединяет двенадцать производителей DRAM. SLDRAM продолжает дальнейшее развитие технологии SDRAM, расширяя четырехбанковую архитектуру модуля до шестнадцати банков. Кроме того, добавляется новый интерфейс и управляющая логика, позволяющая использовать пакетный протокол для адресации ячеек памяти. SLDRAM передает данные так же как и RDRAM, по каждому такту системного таймера.

Память типа RDRAM (Rambus) Память типа RDRAM (Rambus)- имеет многофункциональный протокол обмена данными между микросхемами, позволяющий передачу данных по упрощенной шине, работающей на высокой частоте. RDRAM представляет собой интегрированную на системном уровне технологию. Ключевыми элементами RDRAM являются: модули DRAM, базирующиеся на Rambus; ячейки Rambus ASIC (RACs); схема соединения чипов, называемая Rambus Channel.

Память RamBus, впервые использована в графических рабочих станциях в 1995 году, в ней используется уникальная технология RSL (Rambus Signal Logic - сигнальная логика Rambus), позволяющая использование частот передачи данных до 600MHz в обычных вычислительных системах. Было разработано три вида Rambus - RDRAM, Rambus Concurrent и Direct RDRAM. Rambus использует низковольтовые сигналы и обеспечивает передачу данных по фронту и по спаду уровней сигнала системного таймера. Технология Concurrent Rambus использует улучшенный протокол, показывающий хорошее быстродействие даже на маленьких, случайно расположенных блоках данных, отличается высокой эффективностью, необходимой для графических и мультимедийных приложений. По сравнению с RDRAM, применен новый синхронный параллельный протокол для чередующихся или перекрывающихся данных. Эта технология позволяет передавать данные со скоростью 800Мб/сек на канал и с частотой до 800MГц с синхронным параллельным протоколом, который повышает эффективность еще на 80%. Технология Direct Rambus - еще одно расширение RDRAM. Direct RDRAM имеют те же уровни сигналов (RSL: Rambus Signaling Level - уровень сигналов Rambus), но более широкую шину, более высокие частоты (выше 800MHz) и улучшенный протокол (эффективность выше на 90%). Вычислительные системы на Рentium4 было решено выпускать с использованием памяти RDRAM, в настоящее время только этот вид памяти способен обеспечить работу процессора Рentium4 без режимов ожидания. На этот раз разработчики аппаратного обеспечения перегнали прогресс и теперь уже программисты оказались не готовыми использовать новые возможности параллельной обработки, которые предоставляет им быстрая память. Достигнутые возможности RDRAM памяти пока остаются не востребованными в вычислительных системах широкого пользования (сведения на 2006г.). Однобанковый модуль RDRAM обеспечивал скорость передачи 1.6 Гбайт/сек, двубанковый - 3.2 Гбайт/сек. Но RDRAM память настолько дорогая, что в персональных компьютерах от нее пришлось отказаться и перейти на менее дорогую DDR SDRAM память.

Статическая память. Структура микросхемы, элемент статической памяти.

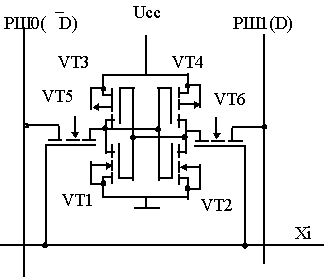

Статическая память - SRAM (Static Random Access Memory), как и следует из ее названия, способна хранить информацию в статическом режиме - то есть сколь угодно долго при отсутствии обращений (но при наличии питающего напряжения). Ячейки статической памяти реализуются на триггерах - элементах с двумя устойчивыми состояниями. По сравнению с динамической памятью эти ячейки более сложны и занимают больше места в кристалле, однако они проще в управлении и не требуют регенерации. Быстродействие и энергопотребление статической памяти определяется технологией изготовления и схемотехникой запоминающих ячеек. Самая экономичная статическая память КМОП (или CMOS Memory) в тоже время и самая медленная память такого типа, имеет время доступа более 100 наносекунд, но зато пригодна для длительного хранения информации при питании от маломощной батареи. Применяется CMOS память в персональных компьютерах для хранения данных о конфигурации и для реализации внутренних часов. Самая быстродействующая статическая память имеет время доступа в несколько наносекунд, что позволяет ей работать на частоте системной шины процессора, не требуя от него тактов ожидания. Относительно высокая удельная стоимость хранения информации и высокое энергопотребление при низкой плотности упаковки элементов не позволяет использовать SRAM в качестве оперативной памяти компьютеров. Статические запоминающие устройства (SRAM) имеют перед динамическими то преимущество, что у них время выборки практически равно времени цикла записи или чтения. Выполненная по той же технологии что и процессор, статическая память имеет высокое быстродействие. Главным ограничением в использовании статической памяти является стоимость. При равной емкости с динамической, статическая память примерно в четыре раза дороже. Поэтому данный вид памяти получил распространение в высокопроизводительных системах в качестве внешней (относительно процессора) кэш памяти. Соотношение цена/производительность в этих системах играет не столь существенную роль. Однако, с появлением микросхем статической памяти большой емкости и ее удешевлением произойдет изменение сложившегося стереотипа использования схем памяти и производители компьютеров, возможно, пойдут на замену динамической памяти статической, пока же элементы статической памяти используются в оперативной динамической памяти, как быстрый конвейерный буфер для подготовки данных к выдаче на шину данных каждый такт системной шины. Структура микросхемы статической памяти Элементом памяти в статических ОЗУ является триггер, выполненный на транзисторах. Структура микросхемы статической памяти (рис.1.) включает матрицу накопителя содержащую М x N элементов памяти.

Для временного хранения адреса используются адресные регистры кода адреса строки и кода адреса столбца. В состав микросхемы памяти входят дешифраторы кодов адреса строк и столбцов, усилители записи/считывания, устройство ввода/вывода и устройство управления. Для управления интегральной схемой (ИС) предназначены адресные сигналы A0 ...АК, обеспечивающие обращение к заданному элементу памяти (ЭП). Если статическая память выполнена в виде самостоятельной микросхемы, а не располагается непосредственно на кристалле процессора ( внутренняя кэш память), линии ее входа чаще всего объединяют с линиями выхода, и требуемый режим работы приходится определять по состоянию специального вывода WE (Write Enable) - разрешение записи. Высокое состояние вывода WE готовит микросхему к чтению данных, а низкое - к записи. В статической памяти, размещенной на одном кристалле с процессором линии входа и выхода данных не объединяют, и поэтому содержимое одной ячейки можно читать параллельно с записью другой. Для выбора микросхемы используется управляющий сигнал CS (Chip Select), разрешающий доступ к накопителю по информационным входам/выходам DIO. Матрица накопителя состоит из строк и столбцов, на пересечении которых размещены элементы памяти. По своему устройству матрица элементов статической памяти практически ничем не отличается от аналогичной ей матрицы элементов динамической памяти. Важное отличие интерфейса статической памяти от интерфейса динамической памяти заключается в том, что в микросхемах статической памяти, имеющих значительно меньшую емкость (следовательно, меньшее количество адресных линий), можно не прибегать к мультиплексированию адреса строки и колонки. Для достижения наивысшей производительности, номера строк и столбцов передаются одновременно. Если в динамической памяти обращение к первой ячейке памяти требует 5-6 тактов, то в статической памяти для первого обращения достаточно 2-3х тактов системной шины. Адрес ячейки памяти принимается в адресный регистр. Затем номера столбцов и строк поступают на декодеры адреса столбца и строки соответственно. После декодирования расшифрованный номер строки поступает на дополнительный декодер, вычисляющий, принадлежащую ей матрицу (обычно при организации микросхемы используется несколько матриц элементов памяти). В результате таких преобразований адреса открывается доступ к требуемой ячейке памяти или странице (современные микросхемы статической памяти, как и динамической, имеют страничную организацию). В зависимости от выбранного режима работы чувствительный усилитель, подсоединенный к шине данных матрицы, либо считывает состояние триггеров соответствующей строки матрицы, либо осуществляет запись информации. Элемент статической памяти Элемент статической памяти, вариант схемотехнической реализации которого по КМДП технологии приведен на pис.2, составляет статический триггер на МДП- транзисторах. Для построения триггера используются транзисторы VT1 - VT2 с каналами n - типа, VT3 - VT4 с каналами p - типа и ключи на транзисторах VT5, VT6, через которые триггер подключается к информационным шинам PШ0 и PШ1. Состояние ключей зависит от уровня сигнала дешифратора на шине строки Xi. При Xi = “1” - ключи открыты и информация с шин PШ0 и PШ1 записывается в триггер или передается из него на выход. Прием и передача информации производится парафазным кодом. Если состояние РШ1=D, то состояние РШ2 = D, при “0” на шине строки Xi - ключи закрыты, и триггер находится в режиме хранения. Для хранения информации в триггере необходим источник питания. При обращении к ИС для записи “0” или “1” следует подать соответствующие уровни на входы DIO, а затем подать код адреса, разрешающий сигнал CS и сигнал WR, соответствующий режиму записи. при подаче указанных сигналов возбуждается строка, выбранная дешифратором кода адреса строк, и открывается доступ по информационным (разрядным) шинам ко всем ЭП данной строки, одновременно возбуждается один из выходов дешифратора кода адреса столбцов, который коммутирует соответствующие столбцы читаемого слова на устройство ввода.

Рис.2.

Элемент статической памяти.

Рис.2.

Элемент статической памяти.

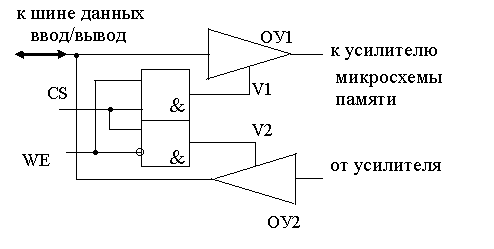

Доступ к разрядным шинам выбранного столбца со стороны устройства ввода/вывода обеспечивает сигнал CS =1. Hастpойка устройства ввода/вывода на прием сигнала со входа DIO осуществляется сигналом WR = “1”. Обращение к ИС для считывания информации происходит аналогично при значении сигнала WR равном “0”. Чтение и запись данных, организация ввода/вывода Обычно для реализации устройств ввода/вывода применяют усилители - формирователи ключевого типа с тремя состояниями выхода. Для одного разряда данных два таких усилителя образуют устройство ввода ОУ2 и вывода ОУ1 информации (рис.3.) Вход ОУ1 и выход ОУ2 соединены с шиной ввода-вывода с системной шиной данных. Для управления состоянием ключей предназначены сигналы V1 и V2, которые могут принимать значения "0" или "1", причем в одних устройствах выход переходит в третье состояние при "1" на управляющем входе V, в других - при “0”. Уровни сигналов CS и WE определяют уровни сигналов V1 и V2 так, что при запрещении сигналом CS=0 обращения к матрице накопителя, сигналы управления имеют нулевое значение и выходы ключей переходят в третье (высокоимпедансное) состояние. В режиме записи CS="1", WE ="1" открыт ключ У1, а у ключа У2 выход находится в третьем состоянии, в режиме считывания наоборот, открыт ключ У2, а у ключа У1 выход находится в третьем состоянии.

Рис.3. Устройство ввода/вывода

Быстрая и дорогая статическая память используется обычно в качестве кэш (процессорного внутреннего или внешнего), где хранится наиболее часто используемая процессором информация. При этом процессор оказывается менее зависим от быстродействия динамического ОЗУ. Высокопроизводительные микросхемы динамических ОЗУ, выполненные по новым технологиям, не в состоянии пока обеспечить достаточно высокого уровня производительности динамической оперативной памяти без использования статической кэш памяти.

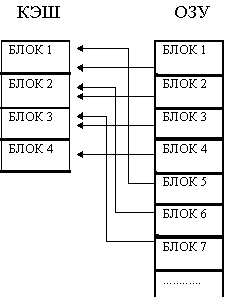

Организация кэш памяти