- •Раздел 1. Общие принципы построения эвм

- •Тема 1.1 История и тенденции развития вычислительной техники. Поколения эвм

- •Тема 1.2. Основные характеристики и классификация эвм

- •Тема 1.3. Архитектура эвм

- •Тема 1.4. Структурные схемы и взаимодействие устройств эвм

- •Тема 1.5. Структурная схема и устройства пк

- •Тема 1.6. Микросхемы системной логики Chipset

- •Тема 1.7. Представление информации в компьютере, единицы измерения информации

- •Раздел 2. Программное обеспечение эвм

- •Тема 2.1. Структура программного обеспечения пк

- •Тема 2.2. Операционные системы

- •Тема 2.3. Файл и файловая система

- •Тема 2.4. Функции и характеристики сетевых ос

- •Тема 2.5. Эволюция режимов работы эвм

- •Раздел 3. Структура базового микропроцессора эвм

- •Тема 3.1. Классификация микропроцессоров

- •1. По числу бис:

- •2. По назначению:

- •3. По виду обрабатываемых сигналов:

- •4. По количеству выполняемых программ:

- •5. По характеру временной организации работы:

- •6. По объему набора инструкций:

- •Тема 3.2. Основные характеристики микропроцессоров

- •1.Разрядность регистров микропроцессора;

- •2.Разрядность шины данных;

- •Тема 3.3. Архитектура микропроцессора

- •Тема 3.4. Структура базового микропроцессора

- •Тема 3.5. Блок внутренних регистров базового микропроцессора

- •Тема 3.6. Сегментные регистры, регистр указателя команд и регистры флагов

- •Тема 3.7. Назначение и классификация уу

- •Тема 3.8. Назначение и классификация алу

- •1. По способу представления чисел:

- •2. По способу действия над операндами:

- •3. По выполняемым функциям алу подразделяются на:

- •4. По структурной организации алу подразделяются на устройства, имеющие:

- •Тема 3.9. Исполнение программного кода

- •Тема 3.10. Сегментная структура программ

- •Раздел 4. Основы программирования на ассемблере

- •Тема 4.1. Этапы создания программы на ассемблере

- •Тема 4.2. Формат команд и их классификация

- •Тема 4.3. Классификация операндов

- •Тема 4.4. Виды команд ассемблера

- •Раздел 5. Защищенный режим работы микропроцессора

- •Тема 5.1. Режимы работы микропроцессора

- •Тема 5.2. Адресация памяти в защищенном режиме

- •Тема 5.3. Дескрипторы и таблицы

- •Тема 5.5. Архитектурные особенности современных микропроцессоров

- •Тема 5.4. Суперскалярная архитектура

- •Принципы построения устройств внутренней памяти

- •4.1. Структура памяти эвм

- •3.2 Представление данных в памяти

- •3.3 Типы данных

- •Тема 6.2. Режимы адресации данных памяти

- •8.1. Общие принципы организации вв

- •10.1. Локальная системная шина

- •10.2. Шина расширения

- •11.1. Способы организации доступа к системной магистрали

- •11.2. Возможные структуры систем пдп

- •6.1. Характеристики систем прерывания

- •6.2. Возможные структуры систем прерывания

- •6.3. Организация перехода к прерывающей программе

Тема 3.8. Назначение и классификация алу

АЛУ – одна из основных функциональных частей процессора, осуществляющая непосредственное преобразование информации.

Все операции, выполняемые в АЛУ, можно разделить на следующие группы:

операции двоичной арифметики для чисел с фиксированной точкой;

операции двоичной (шестнадцатеричной) арифметики для чисел с плавающей точкой;

операции десятичной арифметики над числами, представленными в двоично-десятичном коде;

операции адресной арифметики (при модификации адресов команд);

операции специальной арифметики (нормализация, сдвиг);

логические операции;

операции над алфавитно-цифровыми полями.

Для выполнения перечисленных операций в АЛУ включают следующие функциональные узлы:

сумматор (для выполнения суммирования и других действий над кодами операндов);

регистры (для хранения кодов операндов на время выполнения действия над ними);

сдвигатели (для сдвига кода на один или несколько разрядов вправо или влево);

преобразователи (для преобразования прямого кода числа в обратный или дополнительный);

комбинационные схемы (для реализации логических операций, мультиплексирования данных, управляемой передачи информации, формирования признаков результата).

Регистры и в некоторых случаях сумматоры имеют цепи управления приемом, выдачей и сбросом кодов операндов. Логические операции, операции сдвига и преобразования кодов могут выполняться не только специальными устройствами, но и с помощью дополнительных связей регистров и сумматора.

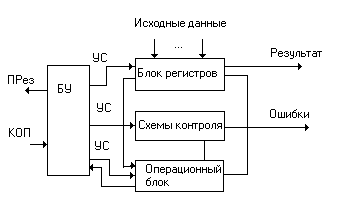

Рис.25 Структурная схема АЛУ

Обобщенная структурная схема АЛУ (рис. 25) включает:

- блок регистров (БР) для приема и размещения операндов и результатов;

- операционный блок, в котором осуществляется преобразование операндов в соответствии с реализуемыми алгоритмами;

- схемы контроля, обеспечивающие непрерывный оперативный контроль и диагностирование ошибок;

- блок управления (БУ), в котором после приема кода операции (КОП) из центрального устройства управления формируются управляющие сигналы (УС), координирующие взаимодействие всех узлов АЛУ между собой и с другими блоками процессора.

Блок регистров (БР) связан с РОН центрального процессора и кэш-памятью данных.

Иногда АЛУ не содержит своего БР, в этом случае операционный блок непосредственно работает с регистрами общего назначения процессора. Для оперативного управления выполнением операции в ОБ на разных этапах анализируется преобразуемая информация и формируются сигналы признаков (флаги), которые используются в БУ для выработки и посылки в процессор сигнала признака результата (ПРез).

Классификация АЛУ

1. По способу представления чисел:

для чисел с фиксированной точкой;

для чисел с плавающей точкой;

для десятичных чисел.

2. По способу действия над операндами:

последовательные;

В последовательных АЛУ операнды представляются в последовательном коде, а операции производятся последовательно во времени над их отдельными разрядами. Такие АЛУ, как правило, используют конвейерный метод обработки, при котором совмещаются во времени фазы выполнения операции для различных разрядов операндов.

параллельные.

В параллельных АЛУ операнды представляются параллельным кодом и операции совершаются параллельно во времени над всеми разрядами операндов.