- •Раздел 1. Общие принципы построения эвм

- •Тема 1.1 История и тенденции развития вычислительной техники. Поколения эвм

- •Тема 1.2. Основные характеристики и классификация эвм

- •Тема 1.3. Архитектура эвм

- •Тема 1.4. Структурные схемы и взаимодействие устройств эвм

- •Тема 1.5. Структурная схема и устройства пк

- •Тема 1.6. Микросхемы системной логики Chipset

- •Тема 1.7. Представление информации в компьютере, единицы измерения информации

- •Раздел 2. Программное обеспечение эвм

- •Тема 2.1. Структура программного обеспечения пк

- •Тема 2.2. Операционные системы

- •Тема 2.3. Файл и файловая система

- •Тема 2.4. Функции и характеристики сетевых ос

- •Тема 2.5. Эволюция режимов работы эвм

- •Раздел 3. Структура базового микропроцессора эвм

- •Тема 3.1. Классификация микропроцессоров

- •1. По числу бис:

- •2. По назначению:

- •3. По виду обрабатываемых сигналов:

- •4. По количеству выполняемых программ:

- •5. По характеру временной организации работы:

- •6. По объему набора инструкций:

- •Тема 3.2. Основные характеристики микропроцессоров

- •1.Разрядность регистров микропроцессора;

- •2.Разрядность шины данных;

- •Тема 3.3. Архитектура микропроцессора

- •Тема 3.4. Структура базового микропроцессора

- •Тема 3.5. Блок внутренних регистров базового микропроцессора

- •Тема 3.6. Сегментные регистры, регистр указателя команд и регистры флагов

- •Тема 3.7. Назначение и классификация уу

- •Тема 3.8. Назначение и классификация алу

- •1. По способу представления чисел:

- •2. По способу действия над операндами:

- •3. По выполняемым функциям алу подразделяются на:

- •4. По структурной организации алу подразделяются на устройства, имеющие:

- •Тема 3.9. Исполнение программного кода

- •Тема 3.10. Сегментная структура программ

- •Раздел 4. Основы программирования на ассемблере

- •Тема 4.1. Этапы создания программы на ассемблере

- •Тема 4.2. Формат команд и их классификация

- •Тема 4.3. Классификация операндов

- •Тема 4.4. Виды команд ассемблера

- •Раздел 5. Защищенный режим работы микропроцессора

- •Тема 5.1. Режимы работы микропроцессора

- •Тема 5.2. Адресация памяти в защищенном режиме

- •Тема 5.3. Дескрипторы и таблицы

- •Тема 5.5. Архитектурные особенности современных микропроцессоров

- •Тема 5.4. Суперскалярная архитектура

- •Принципы построения устройств внутренней памяти

- •4.1. Структура памяти эвм

- •3.2 Представление данных в памяти

- •3.3 Типы данных

- •Тема 6.2. Режимы адресации данных памяти

- •8.1. Общие принципы организации вв

- •10.1. Локальная системная шина

- •10.2. Шина расширения

- •11.1. Способы организации доступа к системной магистрали

- •11.2. Возможные структуры систем пдп

- •6.1. Характеристики систем прерывания

- •6.2. Возможные структуры систем прерывания

- •6.3. Организация перехода к прерывающей программе

Тема 3.3. Архитектура микропроцессора

Архитектура микропроцессора — это совокупность сведений о составе его компонентов, организации обработки в нем информации и обмена информацией с внешними устройствами ЭВМ, а также о функциональных возможностях микропроцессора, выполняющего команды программы.

Структура микропроцессора — это сведения только о составе его компонентов, соединениях между ними, обеспечивающих их взаимодействие. Таким образом, архитектура является более общим понятием, включающим в себя кроме структуры еще и представление о функциональном взаимодействии компонентов этой структуры между собой и с внешней средой.

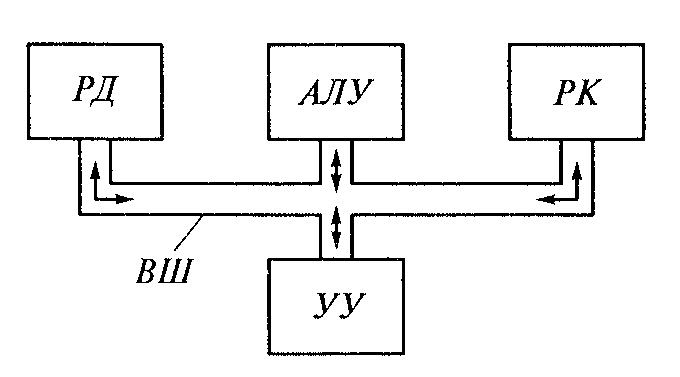

О сновой

любого МП (рис.14) является арифметико-логическое

устройство АЛУ,

выполняющее

обработку информации — арифметические

и логические действия над исходными

данными и соответствии с командами.

Сами данные (исходные, промежуточные

и конечный результат) находятся в

регистрах данных РД,

а

команды — в регистре команд РК.

Управление

всеми процессами по вводу и выводу

информации, взаимодействию между АЛУ,

РД и

РК

осуществляет

многофункциональное устройство

управления УУ.

Данные,

команды и управляющие сигналы передаются

по внутренней шине ВШ.

сновой

любого МП (рис.14) является арифметико-логическое

устройство АЛУ,

выполняющее

обработку информации — арифметические

и логические действия над исходными

данными и соответствии с командами.

Сами данные (исходные, промежуточные

и конечный результат) находятся в

регистрах данных РД,

а

команды — в регистре команд РК.

Управление

всеми процессами по вводу и выводу

информации, взаимодействию между АЛУ,

РД и

РК

осуществляет

многофункциональное устройство

управления УУ.

Данные,

команды и управляющие сигналы передаются

по внутренней шине ВШ.

Рис.14 Типовая структурная схема МП

Каждый микропроцессор имеет свой внутренний язык, называемый множеством микрокоманд или составом команд – это набор команд, которые понимает и может выполнять данный микропроцессор.

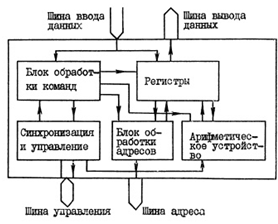

В течение каждого цикла команды ЦП выполняет много управляющих функций:

1) помещает адрес команды в адресную шину памяти;

2) получает команду из шины ввода данных и дешифрирует ее;

3) выбирает адреса и данные, содержащиеся в команде; адреса и данные могут находиться в памяти или в регистрах;

4) выполняет операцию, определенную в коде команды. Операцией может быть арифметическая или логическая функция, передача данных или функция управления;

5) следит за управляющими сигналами, такими как прерывание, и реагирует соответствующим образом;

6) генерирует сигналы состояния, управления и времени, которые необходимы для нормальной работы УВВ и памяти.

Таким образом, ЦП является «мозгом», определяющим действия ЭВМ.

Рис.15 Цикл команды процессора

По характеру исполняемого кода и организации устройства управления выделяется несколько типов архитектур:

Процессор со сложным набором инструкций, англ. CISC — Complex Instruction Set Computer. Эту архитектуру характеризует большое количество сложных инструкций, и как следствие сложное устройство управления. В ранних вариантах CISC-процессоров и процессоров для встроенных приложений характерны большие времена исполнения инструкций (от нескольких тактов до сотни), определяемые микрокодом устройства управления. Для высокопроизводительных суперскалярных процессоров свойственны глубокий анализ программы, внеочередное исполнение операций.

Процессор с упрощённым набором инструкций, англ. RISC — Reduced Instruction Set Computer. В этой архитектуре значительно более простое устройство управления. Большинство инструкций RISC-процессора содержат одинаковое малое число операций (1, иногда 2-3), а сами командные слова в подавляющем числе случаев имеют одинаковую ширину (PowerPC, ARM), хотя бывают исключения (Coldfire). У суперскалярных процессоров — простейшая группировка инструкций без изменения порядка исполнения.

Процессор с явным параллелизмом, англ. EPIC — Explicitly Parallel Instruction Computer (-ing, термин ® Intel, HP). Отличается от прочих прежде всего тем, что последовательность и параллельность исполнения операций и их распределение по функциональным устройствам явно определены программой. Такие процессоры могут обладать большим количеством функциональных устройств без особого усложнения устройства управления и потерь эффективности. Обычно такие процессоры используют широкое командное слово, состоящее из нескольких слогов, определяющих поведение каждого функционального устройства в течение такта.

Процессор с минимальным набором инструкций, англ. MISC — Minimal Instruction Set Computer. Эта архитектура определяется прежде всего сверхмалым количеством инструкций (несколько десятков), и почти все они нуль-операндные. Такой подход даёт возможность очень плотно упаковать код, выделив под одну инструкцию от 5 до 8 бит. Промежуточные данные в таком процессоре обычно хранятся на внутреннем стеке, и операции производятся над значениям на вершине стека. Эта архитектура тесно связана с идеологией программирования на языке Forth и обычно используется для исполнения программ, написанных на этом языке.

Процессор с изменяемым набором инструкций, англ. WISC — Writable Instruction Set Computer. Архитектура, позволяющая перепрограммировать себя, изменяя набор инструкций, подстраивая его под решаемую задачу.

Транспорт-управляемый процессор, англ. TTA — Transort Triggered Architecture. Архитектура изначально ответвилась от EPIC, но принципиально отличающаяся от остальных тем, что инструкции такого процессора кодируют функциональные операции, а так называемые транспорты — пересылки данных между функциональными устройствами и памятью в произвольном порядке.

По способу хранения программ выделяется две архитектуры:

Архитектура фон Неймана. В процессорах этой архитектуры используется одна шина и одно устройство ввода-вывода для обращения к программе и данным.

Гарвардская архитектура. В процессорах этой архитектуры для выборки программ и обмена данным существуют отдельные шины и устройства ввода-вывода. Во встроенных микропроцессорах, микроконтроллерах и ПЦОС это также определяет существование двух независимых запоминающих устройств для хранения программ и данных. В центральных процессорах это определяет существование отдельного кэша инструкций и данных. За кэшем шины могут быть объединены в одну посредством мультиплексирования.

По организации регистрового файла ФУ можно выделить следующие типы процессоров.

Регистровая архитектура — характеризуется свободным доступом к регистрам для выборки всех аргументов и записи результата. Элементарны арифметико-логические операции в таких процессорах кодируются в двух-, или трёхоперандные инструкции (регистр+регистр→регистр, иногда регистр результата совпадает с источником одного из агрументов).

Аккумуляторная архитектура — из регистров выделяется один из несколько регистров-аккумуляторов. Регистр-аккумулятор является источником одного из аргументов и приёмником результата вычислений. Операции кодируются как правило в однооперандные инструкции (аккумулятор+операнд→аккумулятор). Такая архитектура характерная для многих CISC-процессоров (напр. Z80).

Стековая архитектура — определяется организацией регистрового файла в виде стека, и косвенной адресацией регистров через указатель стека, который определяет положение вершины стека, операции производятся над значениями на вершине стека и результат кладётся также на вершину. Арифметические операции кодируются в нуль-операндные инструкции. Стековая архитектура является неотъемлемой частью MISC-процессоров.

Архитектуры и микроархитектуры процессоров

архитектура Intel 32

микроархитектура P6

микроархитектура NetBurst

архитектура Intel 64

микроархитектура Core

микроархитектура Core 2

микроархитектура Itanium

микроархитектура Nehalem

Наборы команд

система команд микропроцессоров x86

расширения архитектуры x86

MMX - Дополнительный «мультимедийный» (англ. Multi-MediaeXtensions) набор инструкций, выполняющих по несколько характерных для процессов кодирования/декодирования потоковых аудио/видеоданных действий за одну машинную инструкцию.

SSE (англ. Streaming SIMD Extensions — потоковое SIMD-расширение) — это SIMD (англ. Single Instruction, Multiple Data — «одна инструкция — множество данных») набор инструкций, разработанный Intel и впервые представленный в процессорах серии Pentium III.

AES расширение системы команд Advanced Encryption Standard (AES), также известный как Rijndael (произносится (Рейндол) ) — симметричный алгоритм блочного шифрования, в котором для шифрования и расшифровывания применяется один и тот же криптографический ключ.

AVX расширение системы команд Advanced Vector Extensions (AVX) — расширение системы команд x86 для микропроцессоров Intel и AMD.

Технологии, применяемые в архитектуре процессора

Hyper-threading — параллелизм на уровне потоков в каждом процессоре обеспечивает ещё большую производительность современных многопоточных приложений. Hyper-threading (англ. Hyper-threading — Гиперпоточность, официальное название Hyper-ThreadingTechnology (HTT)).

Функция SpeedStep SpeedStep — энергосберегающая технология Intel, в основе которой лежит динамическое изменение частоты и энергопотребления процессора в зависимости от используемого источника питания.

Функция Turbo Boost (англ. Turbo Boost — досл. перев. Турбо Подъём (тж. Турбо Разгон, Турбо Ускорение)) — технология компании Intel для автоматического увеличения тактовой частоты процессора свыше номинальной, если при этом не превышаются ограничения мощности, температуры и тока в составе расчетной мощности (TDP).

Аппаратная виртуализация — дополнительная гибкость и максимальная эффективность использования ресурсов систем благодаря консолидации нескольких рабочих сред на одном сервере, рабочей станции или ПК

Функция Execute Disable Bit обеспечивает защиту от вредоносных атак посредством переполнения буфера при поддержке этой функции операционной системой

Intel Active Management Technology — удалённое управление ПК, даже когда они выключены или не работают

Centrino — платформа ноутбука

Intel Atom — процессор для применения в ультрамобильных компьютерах, коммуникаторах и других портативных устройствах

Larrabee — архитектура будущих процессоров, представляющих собой сочетание центрального и графического процессоров

Moorestown — платформа для мобильных интернет устройств (MID)

Доверенная загрузка (аппаратные средства) — технология Intel Trusted Execution обеспечивает защиту конфиденциальности и целостности важных документов от программных атак.