- •6. Счетчики

- •6.1. Введение

- •6.2. Двоичный счетчик

- •6.3. Счетчик по модулю 4

- •8.4. Счетчик по модулю 8

- •6.5. Счетчик по модулю 2n

- •6.6. Одновременная и последовательная подача сигналов на входы элементов счетчика

- •6.7. Синхронные счетчики обратного счета

- •6.8. Счетчик по модулю 5

- •6.9. Двоично-десятичный счетчик

- •6.10. Двоично-десятичный счетчик обратного счета

- •6.11. Десятичный счетчик, использующий код Грея

- •6.12. Реверсивные счетчики по модулю 16

- •Р ис. 6.13. Реализация счетчика по модулю 16 прямого и обратного расчета

- •6.13. Асинхронные двоичные счетчики

- •6.14. Асинхронный десятичный счетчик

- •6.15. Асинхронные счетчики с автоматическим сбросом

- •6.16. Счетчики на интегральных схемах

- •6.17. Каскадирование счетчиков на интегральных схемах

- •Упражнения

6.17. Каскадирование счетчиков на интегральных схемах

Соединим последовательно две микросхемы 7490 и 7493, реализующие десятичный счетчик и счетчик по модулю 16, соответственно (рис. 6.20). Частота входного сигнала первой микросхемы равна 320 кГц. Тогда частота сигнала, появляющегося на выходе шестнадцатеричного счетчика, будет равна 2 кГц. Единственный используемый на практике способ деления частоты на большое число заключается в каскадировании счетчиковых схем.

А

Рис. 6.22.

Трехдекадный счетчик с отображением

результатов счета

С оединим последовательно три микросхемы десятичных счетчиков (рис. 6.22). Результирующую схему можно использовать как трехдекадный счетчик, работающий в коде NBCD. Предположим, что необходимо периодически получать изображения результатов работы счетчика. Тогда информация, снимаемая с выходов каждой микросхемы, сначала декодируется, а затем подается на вход системы отображения, как показано на рис. 6.22.

Упражнения

У6.1. Спроектировать синхронный счетчик по модулю 12 на основе логических элементов И-НЕ и следующих элементов: а) Т-триггеров; б) SR-триггеров; в) JK-триггеров; г) D-триггеров.

Разработать логическую схему декодирования результатов счета.

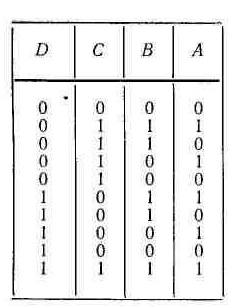

У6.2. Используя JK-триггеры и элементы И-НЕ, спроектировать циклический генератор для последовательности из таблицы, внизу, справа.

Проследить за поведением схемы в неиспользуемых состояниях и показать, что одно из неиспользуемых состояний является запирающим. Предложить способ устранения запирающего состояния.

У6.3. Преобразовать двоичный код (см. таблицу на стр. 116) в соответствующий код Грея и разработать схему счетчика, работающего в этом коде, используя JK-триггеры и элементы И-НЕ.

У6.4. Ниже приведены правила, характеризующие работу PQ-триггера:

PQ = 00 следующее состояние триггера 1 независимо от его текущего состояния;

PQ = 01 следующее состояние триггера является инверсией его текущего состояния;

PQ = 10 следующее состояние триггера такое же, как и текущее;

PQ = 11 следующее состояние триггера 1 независимо от текущего состояния.

Используя приведенную выше информацию, построить управляющую таблицу PQ-триггера, а для двоичного счетчика по модулю восемь, построенного на PQ-триггерах, получить выражение для входных сигналов.

У6.5. Схему, показанную на рис. У6.5, необходимо использовать для генерации импульса Q, длительность которого равна сумме 14 периодов тактового сигнала. Нарисовать временные диаграммы, отражающие поведение наиболее важных сигналов схемы. Спроектировать счетчик и управляющую логику на основе JK-триггеров тина «хозяина - слуга» и элементов И-НЕ.

У 6.6.

В пятиразрядном счетчике со сквозным

переносом использованы триггеры, имеющие

время задержки 30 нс и время декодирования

50 нс. Определить максимально допустимую

частоту работы счетчика. Для случая,

когда счетчик работает на максимальной

частоте, начертить временные диаграммы

работы триггеров при переходе из

состояния 01111 в состояние 10000.

6.6.

В пятиразрядном счетчике со сквозным

переносом использованы триггеры, имеющие

время задержки 30 нс и время декодирования

50 нс. Определить максимально допустимую

частоту работы счетчика. Для случая,

когда счетчик работает на максимальной

частоте, начертить временные диаграммы

работы триггеров при переходе из

состояния 01111 в состояние 10000.

П редположим,

что счетчик действует на частоте 8,33

МГц. Начертить временные диаграммы,

характеризующие поведение счетчика в

интервале времени между пятнадцатым и

шестнадцатым тактовыми импульсами.

редположим,

что счетчик действует на частоте 8,33

МГц. Начертить временные диаграммы,

характеризующие поведение счетчика в

интервале времени между пятнадцатым и

шестнадцатым тактовыми импульсами.

У6.7. Начертить временные диаграммы для следующих асинхронных счетчиков:

а) четырехразрядного двоичного счетчика обратного счета;

б) четырехразрядного двоичного счетчика, считая, что используемые для счета триггеры срабатывают в момент появления положительного фронта импульса, подаваемого на тактовый вход.

У6.8. Спроектировать счетчик по модулю 822, используя микросхемы десятичных счетчиков. Предусмотреть схему запирания, которая необходима для устранения трудностей, связанных с разным временем сброса триггеров.