- •1)Базовый лабораторный стенд.

- •1)Базовый лабораторный стенд.

- •1)Базовый лабораторный стенд.

- •Базовый лабораторный стенд

- •1)Базовый лабораторный стенд;

- •Базовый лабораторный стенд

- •4. Название указывает, что сдвиг данных от разряда к разряду может производиться, как в одну сторону, так и в другую.

- •Базовый лабораторный стенд

- •1)Базовый лабораторный стенд.

- •1)Базовый лабораторный стенд.

1)Базовый лабораторный стенд.

2) Лабораторный модуль Lab 5 для исследования работы четырехразрядного параллельного сумматора.

Внешний вид модуля выглядит так:

Таблица истинности, снятая при помощи лабораторного модуля:

Ответы на вопросы.

1.Сумматор служит для сложения двоичных или десятичных чисел.

Обозначается в виде прямоугольника со входами на левой стороне и выходами на правой стороне. Внутри имеется надпись SM

2. Полусумматор отличается от сумматора тем, что не имеет входа переноса из предыдущего разряда, а сумматор его имеет.

3. Основное отличие сумматоров параллельного и последовательного действия в быстродействии выполнения операции, которая выше у первых.

4. Функции переноса формируются с целью создания сигнала переполнения модуля системы счисления сумматора, а также для правильного отображения результата.

5. Разрядность сумматора можно увеличить , применяя одноразрядные сумматоры, соединяя выход переноса предыдущего со входом переноса следующего сумматора.

Лабораторная работа № 6

ИССЛЕДОВАНИЕ РАБОТЫ ЦИФРОВОГО КОМПАРАТОРА

Цель работы : ознакомление , исследование работы цифрового компаратора

Краткие сведения:

Цифровые компараторы (от английского compare — сравнивать) выполняют сравнение двух чисел А, В одинаковой разрядности, заданных в двоичном или двоично-десятичном коде. В зависимости от схемного исполнения компараторы могут определять равенство А = В или неравенства А<В, А>В. Результат сравнения отображается в виде логического сигнала на одноименных выходах. Цифровые компараторы применяются для выявления нужного числа (слова) в цифровых последовательностях, для отметки времени в часовых приборах, для выполнения условных переходом и вычислительных устройствах, а также в адресных селекторах. Схема одноразрядного компаратора приведена на рис. 9.23. Компаратор состоит из двух элементов НЕ, четырех элементов Ии одного элемента ИЛИ-НЕ.

Схема

одноразрядного цифрового компаратора

Для

исследования компаратора к нему подключен

логический преобразователь. Подсоединяя

его клемму OUT к каждому выходу компаратора,

можно получить таблицу истинности

и булево выражение для каждого режима

работы компаратора. Для случая А=В,

показанного на рис. 9.23, результаты

моделирования представлены на рис.

9.24, откуда видно, что условию А=В

соответствуют две комбинации сигналов

на входе: А=В=1 или А=В=0. Этому условию и

отвечает булево выражение на

дополнительном дисплее.

Схема

одноразрядного цифрового компаратора

Для

исследования компаратора к нему подключен

логический преобразователь. Подсоединяя

его клемму OUT к каждому выходу компаратора,

можно получить таблицу истинности

и булево выражение для каждого режима

работы компаратора. Для случая А=В,

показанного на рис. 9.23, результаты

моделирования представлены на рис.

9.24, откуда видно, что условию А=В

соответствуют две комбинации сигналов

на входе: А=В=1 или А=В=0. Этому условию и

отвечает булево выражение на

дополнительном дисплее.

Результаты моделирования цифрового компаратора Описание лабораторного стенда:

В лабораторный стенд входит :

Базовый лабораторный стенд

Лабораторный модуль Lab 12 дляисследование работы двоичного счетчика

Счетный режим счетчика :

Диаграмма истинности цифрового компаратора :

Ответы на вопросы :

Цифровые компараторы применяются для выявления нужного числа (слова) в цифровых последовательностях, для отметки времени в часовых приборах, для выполнения условных переходом и вычислительных устройствах, а также в адресных селекторах

Первый случай: A>B

Схема:

Результат

моделирования:

Второй

случай: A<b

Схема:

Широкое распространение на практике получило сравнение аналоговых электрических сигналов (чаще всего электрических напряжений), которые получаются на выходе преобразователей неэлектрических величин в электрические с помощью электронных компараторов.

По результатам расчета определены типы и номиналы элементов компаратора, который отвечает решению поставленной задачи. Определен ток потребления, который в свою очередь определяет потребляемую мощность.Определенная потребляемая мощность является отправной точкой для расчета параметров источника питания.

Импульсы компаратора управляют электронным ключом, который в свою очередь подает напряжение питания Vп , на двигатель. При этом чем шире импульсы, тем больше величина Vср - среднее напряжение на двигатель, и он вращается быстрее.

Лабораторная работа №7

Исследование работы RS-триггера

Цель работы- исследование работы RS–триггера

Краткие теоретические сведения

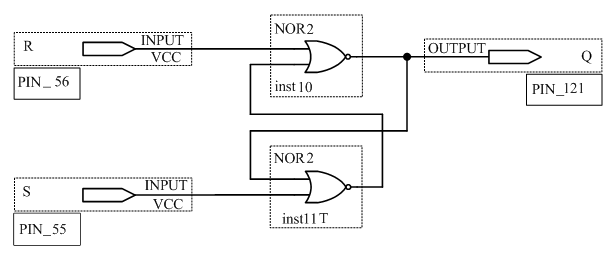

Триггеры предназначены для запоминания двоичной информации. Использование триггеров позволяет реализовывать устройства оперативной памяти (то есть памяти, информация в которой хранится только на время вычислений). Однако триггеры могут использоваться и для построения некоторых цифровых устройств с памятью, таких как счётчики, преобразователи последовательного кода в параллельный или цифровые линии задержки.

Основным триггером, на котором базируются все остальные триггеры является RS-триггер.

RS-триггер имеет два логических входа: R - установка 0 (от слова reset);

S - установка 1 (от слова set). RS-триггер имеет два выхода: Q - прямой; Q- обратный (инверсный).

Состояние триггера

определяется состоянием прямого выхода.

Простейший RS-триггер состоит из двух

логических элементов, охваченных

перекрёстной положительной обратной

связью. .

.

рис.1

1. Асинхронный RS-триггер

рис.2

рис.2

2. Синхронный RS-триггер

рис.3

рис.3

Ответы на вопросы.

Триггер - это устройство последовательного типа с двумя устойчивыми состояниями равновесия, предназначенное для записи и хранения информации. Под действием входных сигналов триггер может переключаться из одного устойчивого состояния в другое. Последовательностными называют такие логические устройства, выходные сигналы которых определяются не только сигналами на входах, но и предысторией их работы, то есть состоянием элементов памяти

Пусть на входы R и S подаются единичные потенциалы. Если на выходе верхнего логического элемента "2И-НЕ" Q присутствует логический ноль, то на выходе нижнего логического элемента "2И-НЕ" появится логическая единица. Эта единица подтвердит логический ноль на выходе Q. Если на выходе верхнего логического элемента "2И-НЕ" Q первоначально присутствует логическая единица, то на выходе нижнего логического элемента "2И-НЕ" появится логический ноль. Этот ноль подтвердит логическую единицу на выходе Q. То есть при единичных входных уровнях схема RS триггера работает точно так же как и схема на инверторах.

Если на входы R и S подать одновременно нулевые сигналы, то на обоих выходах Q и появятся единицы . Если теперь одновременно снять нули со входов R и S, то оба элемента начнут переключаться в нулевое состояние, каждый стремясь при этом оставить своего партнера в состоянии 1. Какой элемент одержит в этом поединке победу, будет зависеть от скоростей переходных процессов и ряда других неизвестных заранее факторов. Для разработчика схемы результирующее состояние триггера оказывается неопределенным, неуправляемым. Поэтому комбинация R=S=0 считается запрещенной, и в обычных условиях ее не используют. Такую комбинацию допустимо применять, лишь когда обеспечено не одновременное, а строго поочередное снятие R и S-сигналов.

RS-триггеры – триггеры с двумя установочными входами.Возможны следующие состояния триггера, в зависимости от комбинации входных сигналов:Rn, Rn = 0, сигнал на выходе может быть Qn+1 = 1 или Qn+1 = 0, что соответствует нейтральному состоянию (режим хранения информации);Sn = 1, Rn = 0, Qn+1 = 1 – установка триггера в единичное состояние;

Sn = 0, Rn = 1, Qn+1 = 0 – установка в нулевое состояние;Sn = 1, Rn = 1 – состояние не определено. Если затем входная комбинация станет Sn = 0, Rn = 0, то триггер с равной вероятностью может установиться или в нулевое, или в единичное состояние, поэтому входная комбинация Sn = 1, Rn = 1 недопустима.

К катоду тиристора подключается выход триггера Q, к управляющему электроду подключается вход S, к аноду подключается постоянное напряжение через полевой транзистор с изолированным затвором, к затвору полевого транзистора подключается вход R.

Триггер - устройство, предназначенное для хранения значения одной логической переменной. Интегральные триггеры, реализуемые на активных и пассивных логических уровнях элементов И-НЕ и ИЛИ-НЕ.

Схема синхронного RS-триггера совпадает со схемой одноступенчатого парафазного (двухфазного) D-триггера, но не наоборот, так как в парафазном (двухфазном) D-триггере не используются комбинации S=0, R=0 и S=1, R=1.Алгоритм функционирования синхронного RS-триггера можно представить формулой

где

x — неопределённое состояние.

где

x — неопределённое состояние.

Лабораторная работа № 8

ИССЛЕДОВАНИЕ РАБОТЫ JK ТРИГГЕРА

Цель работы –ИССЛЕДОВАНИЕ РАБОТЫ JK ТРИГГЕРА.

Краткие теоретические сведения

JK-триггер является

весьма распространенным, универсальным

типом триггера.Триггер имеет два

информационных входа и, предназначенные

для установки его выхода в логическое

состояние 1 или 0. В интегральной

схемотехнике - триггеры обычно выполняются

синхронными, поэтому сигналы на

информационных входах влияют на состояние

- триггера только при поступлении

тактового сигнала на его вход синхронизации.

сигнала на его вход синхронизации.

Рис.1

В состав лабораторного стенда входят: