- •!Шестиуровневая модель компьютера. (Способы поддержки уровней, по, объекты…)

- •Многоуровневая структура компьютера: языки, уровни и виртуальные машины

- •Современные многоуровневые компьютеры

- •Уровень 0: Цифровой логический уровень

- •Уровень 1: уровень Микроархитектуры

- •Уровень 2: уровень архитектуры набора команд

- •Уровень 3: уровень операционной системы

- •Уровень 4: уровень Ассемблера

- •Уровень 5: уровень языка прикладных программистов

- •!Вентили и булева алгебра (транзисторные схемы, значки, таблицы истинности…)

- •Вентили

- •Булева алгебра

- •Реализация булевых функций

- •Построение схемы с использованием одного типа вентилей.

- •Эквивалентность схем

- •!Устройство цп. Цикл выполнения команды (Упрощенная схема…)

- •Устройство центрального процессора

- •Выполнение команд

- •!Многоступенчатый конвейер.

- •!Организация (адресация) памяти.

- •Методы адресации

- •Адресное пространство

- •Исполнение программ

- •Кодирование адресов

- •Вычисление адресов

- •Индексация

- •!Исправление ошибок. Диаграмма Венна. Код Хэмминга.

- •!Описание и диаграмма полной микроархитектуры машины Mic-1.

- •!Микроархитектура процессора 8051

- •!Классификация архитектур м. Flynn (sisd, misd, simd, mimd).

- •!Поколения эвм

- •Основные этапы развития компьютеров

- •Нулевое поколение — механические компьютеры (1642-1945)

- •Первое поколение — электронные лампы (1945-1955)

- •Второе поколение — транзисторы (1955-1965)

- •Третье поколение — интегральные схемы (1965-1980)

- •Четвертое поколение — сверхбольшие интегральные схемы (1980-?)

- •Пятое поколение — невидимые компьютеры

- •Заключение

- •!Закон Мура

- •И стория

- •!Технология Интел «Тик-так»

- •«Тик-так» на дорожной карте Intel

- •!Одноразовые компьютеры. Rfid – системы

- •Что такое rfid?

- •Сфера применения rfid технологий

- •Развитие технологии rfid продолжается

- •!Микроконтроллеры. Функциональная схема.

- •Описание

- •Применение

- •Программирование

- •!Виды пк. Состав компьютерной системы.

- •Виды компьютеров по назначению

- •Универсальные компьютеры

- •Проблемно-ориентированные компьютеры

- •Специализированные компьютеры

- •Виды компьютеров по функциям и внешним параметрам

- •Настольный компьютер

- •Обычный настольный компьютер (десктоп, моноблок)

- •Стационарный нетбук (неттоп)

- •Переносной компьютер

- •Ноутбук (лэптоп)

- •Планшетный компьютер

- •Носимый компьютер (микрокомпьютер)

- •Автоматизированное рабочее место (арм)

- •Мейнфрейм

- •Суперкомпьютер

- •Шаг первый. Cisc

- •!Регистры. Обозначения. Регистр флагов (psw).

- •Операции

- •Регистр флагов

!Микроархитектура процессора 8051

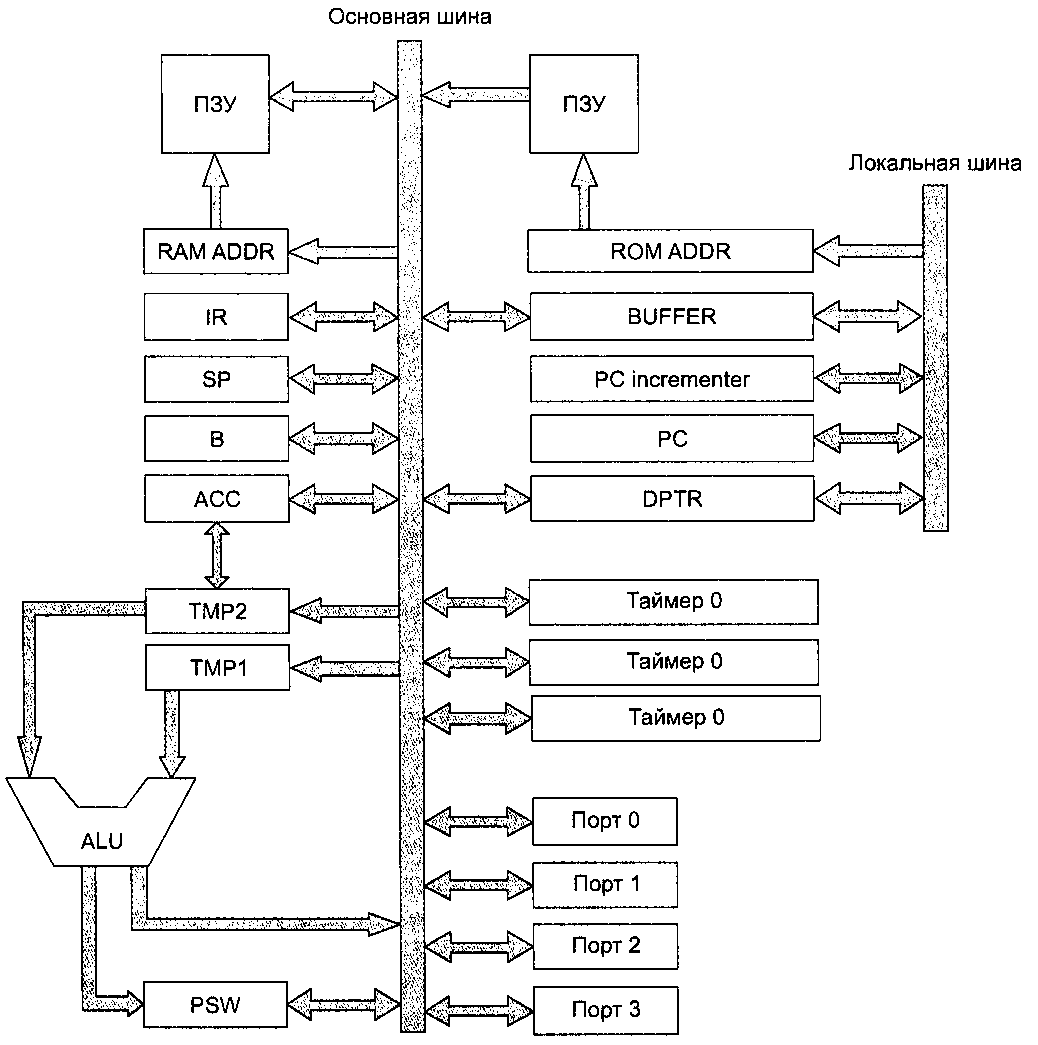

Микроархитектура процессора 8051 (рис. 4.35) значительно проще двух предыдущих - Pentium и UltraSPARC. Дело в том, что размер этой микросхемы очень мал (она состоит из 60 ООО транзисторов), а разрабатывалась она задолго до того, как конвейерная технология стала популярной. Кроме того, перед разработчиками 8051 ставилась задача создать дешевую, а не быструю микросхему. Как известно, "дешевый" и "простой" - очень близкие понятия, в то время как дешевизна и быстродействие в нашем контексте редко сочетаются.

Рис. 4.35. Микроархитектура процессора 8051

Центральное положение в микроархитектуре 8051 занимает основная шина. С ней связаны немногочисленные регистры, причем для большинства из них операции чтения и записи выполняются программно. Регистр АСС представляет собой основной арифметический регистр, в котором сохраняется большая часть результатов вычислений. Через него проходят почти все арифметические команды. Регистр В применяется для умножения и деления; кроме того, при хранении результатов он выполняет роль временного регистра. Регистр SP является указателем стека, как и в большинстве других систем он указывает на вершину стека. В регистре команд IR содержатся команды, выполняемые в данный момент.

Регистры ТМР1 и ТМР2 - это защелки, обслуживающие АЛУ. Перед выполнением операций в АЛУ соответствующие операнды копируются в эти защелки. Результаты вычислений в АЛУ записываются в любой регистр записи, доступ к которому обеспечивает основная шина. Коды состояний, обозначающие нулевые, отрицательные и тому подобные результаты, записываются в регистр PSW (Program Status Word - слово состояния программы).

В 8051 предусмотрены независимые модули памяти для размещения данных и кода. Емкость ОЗУ для размещения данных составляет 128 (модель 8051) или 256 (модель 8052) байт; соответственно, 8-разрядного регистра RAM ADDR вполне достаточно для полной адресации этой памяти. В процессе адресации ОЗУ адрес целевого байта размещается в регистре RAM ADDR, после чего производится обращение к памяти. Емкость памяти кода может достигать 64 Кбайт (при условии размещения модуля памяти вне микросхемы), поэтому разрядность регистра ROM ADDR составляет 16 бит. Схема адресации к программному коду в ПЗУ с помощью регистра ROM ADDR аналогична вышеописанной схеме для памяти данных.

Регистр DPTR (Double PoinTeR - двойной указатель) - это 16-разрядный временный регистр, предназначенный для управления и сборки 16-разрядных адресов. Регистр PC представляет собой 16-разрядный счетчик команд; иными словами, он определяет адрес следующей команды, которую требуется вызвать и выполнить. Регистр PC incrementer - это специальный аппаратный модуль, выполняющий роль псевдорегистра. Когда в него копируется, а затем считыва-ется содержимое регистра PC, его значение автоматически увеличивается на единицу. Ни к PC, ни к PC incrementer нельзя обратиться через основную шину. Наконец, BUFFER - это еще один 16-разрядный временный регистр. На самом деле каждый 16-разрядный регистр процессора 8051 состоит из пары 8-разрядных регистров, с каждым из которых можно выполнять разные операции.

В дополнение ко всему, на микросхеме 8051 устанавливаются три 16-разрядных таймера, необходимых для выполнения приложений в реальном времени. Также предусмотрено четыре 8-разрядных порта ввода-вывода, через которые процессор 8051 может управлять 32 внешними кнопками, световыми индикаторами, датчиками, выключателями и т. д. Именно наличие таймеров и портов ввода-вывода делает возможным применение 8051 в качестве встроенного процессора без установки дополнительных микросхем.

Процессор 8051 относится к категории синхронных - большинство команд, которые он обрабатывает, завершаются за один цикл. Каждый цикл делится на шесть частей, называемых состояниями. В первом состоянии следующая команда вызывается из ПЗУ, и по основной шине отправляется в регистр IR. Во втором состоянии проводится декодирование этой команды, а значение в регистре PC увеличивается на единицу. В третьем состоянии подготавливаются операнды; в четвертом один из них передается основной шине, после чего, как правило, размещается в регистре ТМР1 и выполняет роль операнда АЛУ. В этом же состоянии возможно копирование содержимого АСС в регистр ТМР2, после чего оба АЛУ становятся готовы к дальнейшей обработке. В пятом состоянии происходит выполнение команд АЛУ. Наконец, в шестом состоянии результаты выполнения команд АЛУ передаются обратно основной шине. Одновременно в регистре ROM ADDR проводится подготовка к вызову следующей команды.

Об устройстве 8051 можно было бы рассказать подробнее, однако имеющегося описания и схемы, изображенной на рис. 4.35, вполне достаточно для того, чтобы получить общее представление. Резюмируя вышеизложенное, отметим, что 8051 состоит из одной основной шины (что позволяет уменьшить размер микросхемы), гетерогенного набора регистров, трех таймеров и четырех портов, подключенных к основной шине, а также нескольких дополнительных регистров, соединенных с локальной шиной. В течение каждого цикла тракта данных два АЛУ получают на входе по одному операнду, после чего, как и в более современных системах, результаты сохраняются в регистре.