- •Пассивные компоненты электронных устройств: резисторы, конденсаторы, катушки индуктивности.

- •Электронные переходы. Р-п переход. Р-п переход при прямом и обратном смещении. Виды пробоев р-п переходов.

- •Диоды. Выпрямительные диоды. Стабилитроны. Импульсные диоды. Диоды Шотки.

- •Электронные усилители. Понятие, классификация, параметры, характеристики. Усилители постоянного тока. Дифференциальный усилитель. Обратная связь в усилителях.

- •Фильтры: понятие, разновидности, активные фильтры низких и высоких частот, полосовые фильтры.

- •Генераторы, их разновидности. Rc –генераторы.

- •Импульсные устройства. Компаратор. Триггер Шмитта. Мультивибраторы.

- •Цифровые интегральные схемы. Конструктивно-технологическая реализация, сравнение параметров. Семейство ттл-схем. Логические элементы на кмоп-транзисторах.

- •Особенности проектирования цифровых схем. Общие требования к оформлению цифровых схем.

- •Преобразование и упрощение логических выражений. Упрощение логических функций с помощью карт Карно. Частично-определенная функция и ее упрощение.

- •Режимы неиспользуемых входов логических элементов. Режимы неиспользуемых логических элементов, наращивание числа входов логических элементов.

- •Шифраторы и дешифраторы. Мультиплексоры и демультиплексоры. Сумматоры.

- •Запоминающие устройства (память). Постоянные (пзу) и оперативные (озу) запоминающие устройства.

- •Масочные пзу

- •Масочные пзу на основе диодной матрицы

- •Масочные пзу на основе матрицы моп-транзисторов

- •Масочные пзу на основе матрицы биполярных транзисторов

- •Статическое озу

Шифраторы и дешифраторы. Мультиплексоры и демультиплексоры. Сумматоры.

Дешифратор – это устройство, предназначенное для преобразования двоичного кода в напряжение логической единицы (логического нуля) на том выходе, номер которого совпадает со значением двоичного кода на входе. При n входах в полном дешифратореимеется 2n выходов, т.е. для каждой комбинации входных сигналов имеется соответствующий выход. Дешифратор, у которого при nвходах число выходов меньше 2n, называется неполным. Другое название дешифратора - декодер.

Соответствующие таблице истинности ФАЛ имеют вид

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() .Структурная

схема трехразрядного дешифратора,

синтезированная на основании полученных

ФАЛ приведена на рис.

4.10,а,

а его УГО - на рис.

4.10,б.

.Структурная

схема трехразрядного дешифратора,

синтезированная на основании полученных

ФАЛ приведена на рис.

4.10,а,

а его УГО - на рис.

4.10,б.

б)

Рис. 4.10.Структурная схема и УГО трехразрядного дешифратора.

В общем случае логические уравнения для выходных переменных дешифратора n-разрядного числа имеют вид

![]()

![]()

![]()

![]()

![]() .Построенные

по полученным формулам дешифраторы

называются линейными.

К преимуществу линейных дешифраторов

можно отнести высокое быстродействие,

поскольку входные переменные одновременно

поступают на все элементы И. Одновременно,

без дополнительных задержек, формируется

и результат на выходах этих элементов.

Очевидно, что для реализации линейного

дешифратораn-разрядного

числа необходимо иметь 2n логических

элементов И с n-входами.

В существующих микросхемах логических

элементов количество входов ограничено.

Следовательно, ограничена и разрядность

реализуемых на их основе линейных

дешифраторов, что является недостатком.

Кроме того, недостатком является и то,

что предыдущие элементы, работающие на

входы дешифратора, должны иметь высокую

нагрузочную способность, т.е. должны

быть рассчитаны на подключение большого

числа логических элементов И. Каждый

из входов дешифратора подключен к

0,5·2n логическим

элементам И. Поскольку нагрузочная

способность базовых логических элементов

ИС не превышает величины N=10¸20,

то максимальная разрядность дешифрируемых

чисел для линейных дешифраторов n=4¸5.Указанного

недостатка лишены пирамидальные

дешифраторы.

Принцип построения этих дешифраторов

состоит в том, что сначала строят линейный

дешифратор для двухразрядного

числа X1, X2,

для чего необходимы 22=4

двухвходовые схемы И. Далее, каждая

полученная конъюнкция логически

умножается на входную переменную X3 в

прямой и инверсной форме. Полученная

конъюнкция снова умножается на входную

переменную X4 в

прямой и инверсной форме и т.д. Наращивая

таким образом структуру, можно построить

пирамидальный дешифратор на произвольное

число входов. На рис.

4.11 приведена

структура пирамидального дешифратора

для трех разрядов.

.Построенные

по полученным формулам дешифраторы

называются линейными.

К преимуществу линейных дешифраторов

можно отнести высокое быстродействие,

поскольку входные переменные одновременно

поступают на все элементы И. Одновременно,

без дополнительных задержек, формируется

и результат на выходах этих элементов.

Очевидно, что для реализации линейного

дешифратораn-разрядного

числа необходимо иметь 2n логических

элементов И с n-входами.

В существующих микросхемах логических

элементов количество входов ограничено.

Следовательно, ограничена и разрядность

реализуемых на их основе линейных

дешифраторов, что является недостатком.

Кроме того, недостатком является и то,

что предыдущие элементы, работающие на

входы дешифратора, должны иметь высокую

нагрузочную способность, т.е. должны

быть рассчитаны на подключение большого

числа логических элементов И. Каждый

из входов дешифратора подключен к

0,5·2n логическим

элементам И. Поскольку нагрузочная

способность базовых логических элементов

ИС не превышает величины N=10¸20,

то максимальная разрядность дешифрируемых

чисел для линейных дешифраторов n=4¸5.Указанного

недостатка лишены пирамидальные

дешифраторы.

Принцип построения этих дешифраторов

состоит в том, что сначала строят линейный

дешифратор для двухразрядного

числа X1, X2,

для чего необходимы 22=4

двухвходовые схемы И. Далее, каждая

полученная конъюнкция логически

умножается на входную переменную X3 в

прямой и инверсной форме. Полученная

конъюнкция снова умножается на входную

переменную X4 в

прямой и инверсной форме и т.д. Наращивая

таким образом структуру, можно построить

пирамидальный дешифратор на произвольное

число входов. На рис.

4.11 приведена

структура пирамидального дешифратора

для трех разрядов.

>Рис. 4.11. Пирамидальный дешифратор для трехразрядного числа.Характерным отличием пирамидальных дешифраторов от линейных является использование только двухвходовых логических элементов вне зависимости от разрядности дешифрируемого числа. В то же время количество логических элементов в пирамидальном дешифраторе больше. Однако следует иметь ввиду, что количество логических элементов, располагаемых в одном корпусе ИС, определяется главным образом требуемым количеством выводов. Следовательно, в одном корпусе ИС можно расположить большее число двухвходовых элементов, чем трехвходовых, четырехвходовых и т.д. И значит, пирамидальная структура дешифратора по числу корпусов ИС может оказаться более предпочтительной, чем линейная.

Шифраторы выполняют задачу обратную той, которую выполняют дешифраторы: появление логической единицы (логического нуля) на определенном входе приводит к появлению соответствующей кодовой комбинации на выходе. Также как и дешифраторы, шифраторы бывают полными и неполными. Работа восьмивходового полного шифратора задается следующей таблицей истинности.На основании таблицы истинности можно записать ФАЛ, задающие работу восьмивходового шифратора:

![]()

![]()

![]() .Синтезированная

на основании приведенных логических

уравнений структурная схема шифратора

представлена на рис.

4.12,а,

а его условное графическое обозначение

– на рис.

4.12,б.

.Синтезированная

на основании приведенных логических

уравнений структурная схема шифратора

представлена на рис.

4.12,а,

а его условное графическое обозначение

– на рис.

4.12,б.

а) б)

Рис. 4.12.Структура и УГО восьмивходового шифратора.

Мультиплексор - это устройство, которое осуществляет выборку одного из нескольких входов и подключает его к своему выходу, в зависимости от состояния двоичного кода. Другими словами, мультиплексор - переключатель сигналов, управляемый двоичным кодом и имеющий несколько входов и один выход. К выходу подключается тот вход, чей номер соответствует двоичному коду. Ну и навороченное определение: мультиплексор - это устройство, преобразующее параллельный код в последовательный. Структуру мультиплексора можно представить различными схемами, но более понятна, на мой взгляд, вот эта:

Рис. 1 - Структура мультиплексора

Самая большая хренотень есть не что иное, как элемент И-ИЛИ. Конкретно здесь элемент 4-х входовый. Ну а квадратики с единичками внутри, если кто не помнит, инверторы. Разберем выводы. Те, что слева, а именно D0-D3, называются информационными входами. На них чего-нибудь подают. Входы посередке, а именно А0-А1, называются адресными входами. Вот сюда именно и подается двоичный код, от которого зависит, какой из входов D0-D3 будет подключен к выходу, на этой схеме обозначенному как Y. Вход С, черт его знает, нафига он здесь. Вроде бы как разрешение работы, а может просто для понта. Ну его в баню. На схеме еще есть входы адреса с инверсией. Так вот они тоже показаны здесь для понта. На этом рисунке показан четырехвходовой, или как еще его называют, 4Х1 мультиплексор. Потому и адресных входов всего 2. Как нам известно, максимальное число переменных определяется как 2n, где n - разряд кода. Здесь мы видим, что переменных четыре штуки, а значит разряд будет равен 2 (22 = 4). Для пояснения принципа работы этой схемы посмотрим на табличку истинности:

A1 |

A0 |

Y |

0 |

0 |

D0 |

0 |

1 |

D1 |

1 |

0 |

D2 |

1 |

1 |

D3 |

Вот так двоичный код выбирает нужный вход. Т. е., если имеем четыре объекта, ну, скажем, они пуляют сигналы, а устройство отображения у нас одно. Берем мультик (мультиплексор) и втуляем его в схему. В зависимости от двоичного кода к устройству отображения подключается сигнал от нужного объекта. Такой вот, дохленький пример.

Микросхемой мультик обозначается вот так:

Рис. 2 - Мультиплексор

Вообще, мультиплексоров всяких дофига. Есть и сдвоенные четырехвходовые, восьмивходовые, 16-ти входовые, счетверенные двухвходовые и пр. Тот, что на рисунке сделан от фонаря.

Демультиплексор. Демультиплексор - устройство, обратное мультиплексору. Т. е., у демультиплексора один вход и куча выходов. Двоичный код определяет, какой выход будет подключен ко входу. Другими словами, демультиплексор - это устройство, которое осуществляет выборку одного из нескольких выходов и подключает его к своему входу или, это переключатель сигналов, управляемый двоичным кодом и имеющий один вход и несколько выходов. Ко входу подключается тот выход, чей номер соответствует состоянию двоичного кода. И навороченное определение: демультиплексор - это устройство, которое преобразует последовательный код в параллельный.

Обычно в качестве демультиплексора используют дешифраторы двоичного кода в позиционный, в которых вводят дополнительный вход стробирования. Из-за схожести структур мультиплексора и демультиплексора в КМОП сериях есть микросхемы, которые одновременно являются мультиплексорром и демультиплексором, смотря с какой стороны подавать сигналы, например, К561КП1, работающая как переключатель 8х1 и переключатель 1х8 (то бишь, как мультиплексор и демультиплексор с восемью входами или выходами). Кроме того, в КМОП микросхемах помимо переключения цифровых сигналов (лог. 0 или 1) существует возможность переключения аналоговых. Другими словами, это переключатель аналоговых сигналов, управляемый цифровым кодом. Такие микросхемы называются коммутаторами. К примеру, с помощью коммутатора можно переключать сигналы, поступающие на вход усилителя (селектор входов). Вот напоследок простенькую схемку селектора входов УМЗЧ мы и рассмотрим. Построим ее, ну скажем, с использованием триггеров и мультиплексора.

Рис. 3 - Селектор входных сигналов

Вот такая нехитрая схемка. Итак, разберем работу и деталюшки. На триггерах микросхемы DD1 собран кольцевой счетчикнажатий кнопки разрядностью 2 (два триггера - 2 разряда). Двухразрядный двоичный код поступает на адресные входы D0-D1 микросхемы DD2. Микросхема DD2 представляет собой сдвоенный четырехканальный коммутатор. В соответствии с двоичным кодом к выходам микросхемы А и В подключаются входы А0-А3 и В0-В3 соответственно. Элементы R1, R2, C1 устраняют дребезг контактов кнопки. Дифференцирующая цепь R3C2 устанавливает триггеры в нулевое состояние при включении питания, при этом к выходу подключается первый вход. При нажатии на кнопку триггер DD1.1 переключается в состояние лог. 1 и к выходу подключается второй вход и т. д. Перебор входов идет по кольцу, начиная с первого.

С одной стороны просто, с другой немного неудобно. Черт его знает, сколько раз нажали на кнопку после включения и какой вход подключен к выходу. Хорошо бы поставить индикатор подключенного входа. Вот тут-то и пригодится семисегментный дешифратор. Нажимаем ссылочку, вспоминаем семисегментный дешифратор и смотрим на схемку (там, где циферки бегут). Берем дешифратор и индикатор, обрубаем счетчик и другую галиматью, переносим дешифратор с индикатором на схему коммутатора и первые два входа дешифратора (на схеме обозначен как DD3), т. е. 1 и 2 (выв. 7 и 1) подключаем к прямым выходам триггеров DD1.1 DD1.2 (выв. 1 и 13). Входы дешифратора 4 и 8 (выв. 2 и 6) кидаем на корпус (т. е. подаем лог. 0). Все! Индикатор будет показывать состояние кольцевого счетчика, а именно циферки от 0 до 3. Цифиря 0 соответствует первому входу, 1 - 2-му и т. д.

Сумматор.

К суммирующим схемам относятся сумматоры и схемы вычитания. Эти схемы используются для решения алгебраических уравнений и в устройстваханалоговой обработки сигналов. Сумматором называется устройство, на выходе которого сигналы, подаваемые на его входы, суммируются. Сумматоры

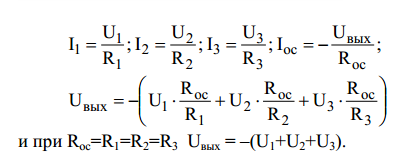

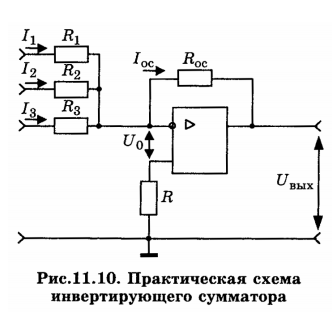

строятся с использованием инвертирующих и неинвертирующих усилителей.Схема инвертирующего сумматора с тремя входными сигналами привед. на рис. 11.10. Для простоты рассуждений принимаем, что R1=R2=R3=Roc. Поскольку у идеального ОУ KU→∞,Rвx→∞, а ток смещения очень мал посравнению с током обратной связи, то согласно закона Кирхгофа I1+I2+I3=Iос. (11.19)Вследствие того, чтоинвертирующий вход имеетпрактически нулевой потенциал, то внем отсутствует взаимное влияние

входных сигналов. Выражение(11.19) может быть представлено ввиде

Следовательно

на выходе получается инвертированная

сумма входныхнапряжений. Если R1≠R2≠R3,

то на выходе получается инвертированная

суммавходных напряжений (11.20) с различными

масштабными коэффициентами. Инвертирующий

сумматор объединяет в себе функции

сумматора и усилителяпри сохранении

простоты схемы. Резистор R служит для

компенсации сдвигануля на выходе ОУ,

вызванного временными и температурными

колебаниямивходного тока. Сопротивление

R выбирают токай величины, чтобы

эквивалентные сопротивления, подключенные

ко входам ОУ были одинаковы:R=Roc||R1||R2||R3.

Следовательно

на выходе получается инвертированная

сумма входныхнапряжений. Если R1≠R2≠R3,

то на выходе получается инвертированная

суммавходных напряжений (11.20) с различными

масштабными коэффициентами. Инвертирующий

сумматор объединяет в себе функции

сумматора и усилителяпри сохранении

простоты схемы. Резистор R служит для

компенсации сдвигануля на выходе ОУ,

вызванного временными и температурными

колебаниямивходного тока. Сопротивление

R выбирают токай величины, чтобы

эквивалентные сопротивления, подключенные

ко входам ОУ были одинаковы:R=Roc||R1||R2||R3.

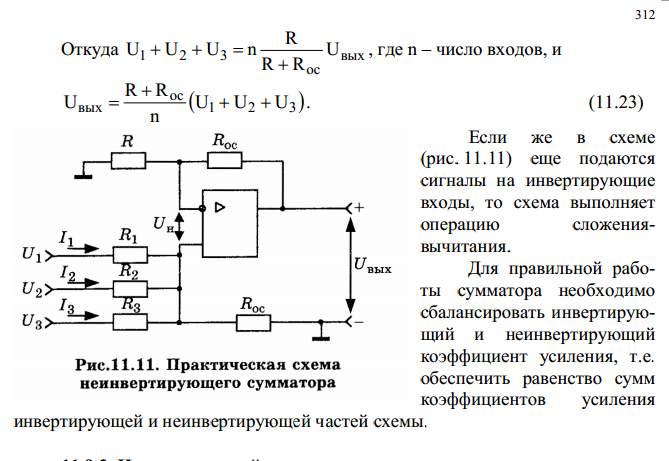

Схема неинвертирующего сумматора, который строится на базе неинвер-

тирующего усилителя, приведена на рис. 11.11. Так как при U0=0 напряжения

на

инвертирующем и неинвертиющем входах

равны, то![]()