- •Сущность автоматизации производства. Структура асу предприятия

- •Структура асу управления полиграфическими предприятиями и издательствами

- •Структура асу технологическими процессами

- •Автоматизированная система супервизерного управления

- •Пример двухуровневой системы переработки информации

- •Система гибкого автоматизированного производства

- •Структура обеспечения асу: организационное, информационное обеспечение

- •Структура обеспечения асу: алгоритмическое, программное обеспечение, технологическое

- •9. Основные характеристики эвм.

- •10. Однопрограммный режим работы эвм.

- •11. Мультипрограммный режим работы эвм.

- •13.Режим разделения времени,

- •14. Диалоговый режим работы

- •17. Структура системного блока.

- •19. Функции чипсета системной платы.

- •20. Определение пропускной способности шин. Привести пример.

- •23. Основные регистры процессоров. Технология ммх, sse.

- •34.Основные функции базовой системы ввода-вывода (bios).

- •35. Программа post

- •36. Загрузка операционной системы.

- •37. Функции утилиты Setup

- •38. Классификация и характеристики внешней памяти

- •39. Компакт-диски (cd). Стандарты компакт-дисков. Характеристики cd. Приводы cd.

- •41.Blue-ray технология

- •42. Флэш-память. Ленточные устройства памяти.

- •43. Винчестер. Конструкция винчестера. Характеристики винчестера. Интерфейс винчестера.

- •44. Организация raid систем.

- •45. Принципы записи информации на внешние носители.

- •46. Состав и общие параметры видеосистемы.

- •47. Назначение и функциональная схема графического адаптера.

- •49. Растровая и векторная системы вывода изображений.

- •50. Принцип работы электронно-лучевого монитора.

- •51. Принцип работы жидкокристаллического монитора.

- •52. Характеристики мониторов. Типы мониторов.

- •53. Звук в персональном компьютере. Оцифровка звуковых сигналов.

- •54. Конструкция и характеристики звуковой платы. Акустическая система.

- •55. Использование пк для обработки «цифрового» звука.

- •56.Компрессия звука. Аудиокодек

- •57. Оборудование автоматизированных систем редакционно-издательских процессов. Типы сканеров. Принципы работы сканеров

- •58. Оборудование автоматизированных систем редакционно-издательских процессов. Типы принтеров. Принципы работы принтеров

- •59. Устройство и принцип действия web-камер

- •60. Назначение, принцип действия и характеристики шин расширения pci и pci-X

- •61. Назначение и характеристики интерфейсов графического адаптера agp, pci_Express 16-X

- •62. Функции и характеристики шины pci-Express

- •63. Назначение и характеристики шины usb

- •64. Интерфейс ide-ata, sata

- •65. Многомашинные вычислительные системы

- •66. Многопроцессорные вычислительные системы

- •67. Многопроцессорная вс типа окмд

- •68. Многопроцессорная вс типа мкод

- •69.Классификация вычислительных систем

- •70. Симметричные мультипроцессорные системы и избыточные системы

- •71. Назначение модемов. Виды модемов.

- •72. Особенности работы и характеристики модемов adsl

- •73. Радиосистемы передачи данных

- •75. Беспроводные технологии связи Wi-Fi, WiMax.

- •76. Мобильные беспроводные технологии связи 3g, 4g.

- •77. Принципы работы и организация ip – телефонии.

23. Основные регистры процессоров. Технология ммх, sse.

Регистр – функц. узел, осуществл. приём, хр-е и передачу инф-ции. Регистры сост. из гр. триггеров. По типу приёма и выдачи инф-ции различ. 2 типа регистров:

с последов. приёмом и выдачей инфы – сдвиговые регистры.

с пар. приёмом и выдачей инфы – параллельные регистры.

Сдвиговые регистры – посл-но соединён. цепочка триггеров. Осн. режим раб. – сдвиг разрядов кода от 1 триггера к др. на кажд.импульс тактов. сигнала.

По назначению регистры различаются на:

аккумулятор – исп. для хран-ия промежут. рез-в арифметич. и логич. операций и инструкций ввода-вывода;

флаговые – хран. признаки рез-в арифметич. и логич. операций;

общ. назнач-я – хран. операнды арифметич.и логич. выражений, индексы и адреса;

индексные – хран. индексы исх. и целевых элементов массива;

указательные – хран. указатели на спец. области памяти (указатель текущ. операции, указатель базы, указатель стэка);

сегментные – хран. адреса и селекторы сегментов памяти;

управляющие – хран. инфу, управл. состоянием проц., а также адреса сист. таблиц.

Технология MMX разраб. для ускор-я мультимедиа и коммуникац.программ. Она включ. в себя нов. команды и типы данных, что позвол. создав. прилож-я нов. ур-ня. Технология основ. на парал. обработке данных. При этом сохр-ся полн. совместимость с сущ-ми ОС и ПО. ММХ-технологии поддерж. нов. арифметику, наз. арифметикой с насыщением. Наиб. эффект от использ-я ММХ-технологии м. б. достигнут в алгоритмах со сл. характеристиками:

мал. размер данных (8-битные граф-е пиксели, 16-битные зв. данные);

короткие, часто повторяющиеся циклы;

частые умножения и накопления.

Набор MMX-команд сост. из команд пересылки данных, упаковки/распаковки, сложения/вычитания, умножения, сдвига, сравнения и поразрядных логических. Команды упаковки и сложения/вычитания могут раб. в 2 режимах: обычном, когда переполн-е разрядн. сетки вызыв. "заворачивание" знач-я рез-та, и спец., когда оно прив. к огранич-ю рез-та до мин. или макс. допустимого значения. Режим ограничения в терминологии Intel называется Saturation (насыщение) - в нем особенно удобно выполнять смешивание цветов изображение или амплитуд звуковых сигналов, поскольку при обычном переполнении результат не имеет никакого смысла.

SSE-этонабор инструкций, разработанный Intel и впервые представленный в процессорах серии PentiumIII . Технология SSE позволяла преодолеть 2 осн. проблемы MMX — при использ. MMX невозможно было одновр-но использ. инструкции сопроцессора, т. к. его регистры были общими с регистрами MMX, и возможность MMX работать только с целыми числами.

SSE включ. в архит-ру процессора 8 128-битных регистров и набор инструкций, работающих со скалярными и упакованными типами данных.

Преим-во в производительности достиг. в том случае, когда необх.произвести 1 и ту же посл-сть действий над разн.данными. В таком случае блоком SSE осуществляется распараллеливание вычислительного процесса между данными.

24. Конвейерные суперскалярные процессоры.

Принципы конвейерной технологии. Разраб-ки архитектуры компов издавна прибег. к методам проект-я, известным под общ.назв-ем "совмещение операций", при одноврем. более 1 базов.операции. Этот общий метод включ. 2 понятия: параллелизм и конвейеризацию. Хотя у них много общего, эти термины отраж. 2 соверш. разл. подхода. При параллелизме совмещ-е операций достиг-ся путем воспроизв-я в неск. копиях аппаратной стр-ры. Выс-я произв-сть достиг-ся за счет одновр. раб. всех элементов структур, осуществл. решение разл.частей задачи.

Конвейерная архитектура была введ в центр.процессор с целью повыш-я быстродействия. Обычно для вып-я каждой команды требуется осуществ.некоторое количество однотипных операций, например: выборка команды из ОЗУ, дешифрация команды, адресация операнда в ОЗУ, выборка операнда из ОЗУ, выполнение команды, запись результата в ОЗУ. Каждую из этих операций сопоставляют одной ступени конвейера. Например, конвейер микропроцессора с архитектурой MIPS-I содержит четыре стадии:

получение и декодирование инструкции (Fetch)

адресация и выборка операнда из ОЗУ (Memoryaccess)

выполнение арифметических операций (ArithmeticOperation)

сохранение результата операции (Store)

Если предполож., что кажд. ступень конвейера тратит ед. времени на свою работу, то вып-е команды на конвейере длиной в n ступеней займёт n единиц времени.

В совр. процессорах пар-но м. работать несколько конвейеров, так что произв-ость проц. м. оценив. темпом выхода выполнен. инструкций со всех его конвейеров. Для достиж-я макс.произв-сти процессора — обеспеч-я полной загрузки конвейеров — программа должна сост-ся с учетом микроархитектурных особенностей процессора. Конвейеры процессоров Р6 с суперконвейерной архитектурой (superpipelined) имеют больш. число ступеней (10–12).

Процессоры архитектуры P6 состоят из 4 осн. подсистем:

Подсистема упорядоченной предварительной обработки — отвечает за выборку и декодирование инструкций в порядке, предусмотренном программой, и предсказывает переходы.

Ядро исполнения с изменением последовательности — отвечает за исполнение микроопераций в оптимальном порядке и организует взаимодействие исполнительных устройств.

Подсистема упорядоченного завершения— выдаёт результаты исполнения в порядке, предусмотренном программой.

Подсистема памяти— обеспечивает взаимодействие процессора с оперативной памятью.

25.Принципы взаимодействия центрального процессора с памятью.

Процессор м. представить в виде след. внутренних узлов:

– устройство управления, предназнач. для дешифр-я и исп-я команд;

– раб.регистры, необх. для адресации памяти и вып-я вычисл. операций;

– арифметико – логич. устр-во, вып. логич. и арифметич. операции;– упр-е вводом – выводом, ввод-вывод данных в процессор или из процессора;

Процессор раб. с командами. В команде предпис-ся какое действие долж. выполн. процессор и с какими данными. А люб. программа, кот. вып-ся проц. сост. из множ-ва разл. команд, выполн. кот. проц. вып. программу.

Команда для проц-в в общ. случае им. следующ. формат: Здесь 1 группа бит образует поле код операции. Код операции показыв., что проц-р должен делать. А поля, отвед. под операнды, предоставл. необх.данные для осуществл-я операции процессором.

Процессор рабо. с опер.памятью, так как в ней хран-ся данные, необх. процессору для работы и в опер. память процессор помещ. рез-ты своих вычисл-й перед окончат. сохр-ем в долговрем.памяти. Взаимодействие проц. с пам. происх. посредством шин адреса, данных и упр-я.На шину адреса помещ-ся адрес ячейки пам. с данными, необх. процессору.На шину данных помещ-ся данные из процессора, кот. необх. записать в память или данные из пам., кот.необх. процессору для вычислений.На шину упр-ия поступ.сигналы из проц., кот.е указыв. памяти или др.устр-вам какое устр-во процессор выбрал и какую операцию будет произв.: чт-е или запись пам. или др. устр-в.

Когда процессор считыв. данные из опер. пам., ему прих-ся какое-то время «ждать», поскольку тактов. частота опер. пам. значит-но ниже, чем проц.. Если проц. со встроен. в кристалл кэш-памятью раб. на частоте 2 ГГц, то прод-сть цикла проц. и интегр. кэш-памяти в этом случае достигнет 0,5 нс, в то время как прод-сть цикла опер. пам.будет в 6 раз больше, т. е. ок. 3 или 6 нс для памяти с удвоен. скоростью передачи данных. Поэтому процессор сразу ищет данные в кэш-памяти.

Работа процессора происх. по такому алгоритму. Программн. счётчик выдаёт адрес команды на шину адреса. Память помещ. команду, нах.по этому адресу на шину данных. Процессор ввод. команду в свой регистр команды. Там команда дешифруется, опр-я код операции, опр-ся длина команды в байтах. Программный счётчик адресует след. команду, нах. по адресу на длину команды от предыдущ.. Сама команда после её обработки регистром команды, вып-ся остальн. устр-ми процессора, назнач-е кот. указано выше. Когда вып-е команды заверш-ся содержимое программного счётчика помещается на шину адреса и цикл повторяется.

26. Определение производительности процессора.

Cледует учитыв., что произв-сть компа завис. не только от "железа", но и от умения программиста использ. его особ-сти в программе, кот. будет раб. на том или ином "железе". 1 и та же программа, написан. разными программистами, покажет разные показатели по произв-сти. Кроме того, конкр. задачи, кот. выполняются на компе, по-разному загруж. процессор, кэш, системную шину, память и периферию.

Основными техническими показателями процессора являются:

1. частота системной шины; 2. разрядность системной шины; 3. коэффициент умножения.

Частота системной шины показывает, какое количество бит данных может быть передано в процессор за одну секунду. Например, если частота шины 200 МГц это означает, что за 1 секунду может быть передано в процессор 200 Мбит. Разрядность системной шины показывает число каналов для передачи данных в процессор (чаще всего бывает 32 и 64). Например, если частота системной шины 200 МГц, а разрядность 32, то пропускная способность составит (200*32)/8=800 Мб/c. Коэффициент умножения показывает, во сколько раз процессор работает быстрее, чем шина, на которой он установлен. Например, при частоте шины 200 МГц и коэффициентом умножения 15 получаем тактовую частоту процессора 3000 МГц.

Теперь необходимо ввести такое понятие как сложность задачи. То есть любой задаче, которая выполняется на компьютере, может быть присвоен свой коэффициент сложности от 1 до 8. К самым сложным задачам относят преобразование файла из одного формата в другой, и расчет точки в трехмерном пространстве (современные игры-стратегии, работа с 3D-графикой). При этом сложность задачи соответствует коэффициенту умножения процессора. Например, процессор с тактовой частотой 1600 МГц и частотой системной шины 200 МГц, при поступлении в него задачи с 8 коэффициентом сложности в виде 200 Мбит, справится с ней за одну секунду.

27.Технологии повышения производительности и энергосбережения процессоров.

Для повыш. быстродействия процессоров, как центр., так и графич., разгон сводится к повыш. тактов. частоты. Для повыш. быстродействия пам.— к повыш. тактов. частоты и пониж. таймингов. Для повыш.частоты раб. процессоров и пам. исп-ся как встроен. ф-ции BIOS, так и программн. ср-ва. В больш. случаев рост тактов. частоты центр. и граф.процессоров, а также модулей пам. сопров-ся увелич. рассеиваем. мощности, что прив. к росту температуры разогнан. компонентов.

Методы увеличения производительности процессора.

1. Прим-е мат.. сопроцессора для раб. с действ. числами, у кот. есть 80-разрядные регистры.

2. Повышение тактовой частоты.

3. Повышение разрядности процессора.

4. Внутр. умнож-е частоты – внешн. операции процессор вып. с 1 частотой, а внутр. операции - с др., более высокой.

5. Кэширование памяти.

6. Конвейерная обработка данных.

Управление электропитанием – интегриров. подход к энергосбереж-ю в масштабах всей системы (на ур. аппаратн. средств и программн. обеспеч-я). Это означ., что комп. система, в полн. объеме поддерживающ. упр-ие электропитанием и энергосбережение, должна включ. как аппаратную, так и программн. поддержку для след. функций:

Повыш-е или пониж-е тактов.частоты влияет на энергопотребл-е почти в прямо пропорц. зав-сти, а от напряж-я завис-сть квадратичная. по этой причине увелич-е напряж-я всегда более сущ. сказ-ся на энергопотребл-и, чем повыш-е тактов. частоты.

Использ-е технологии TurboBoost — технология компании Intel для автоматич. увелич-я тактов. частоты проц. свыше номинальной, если при этом не превыш-ся огранич-я мощности, темп-ры и тока в с-ве расчетной мощности (TDP). Это прив. к увелич-ю произв-сти однопоточн. и многопоточн. приложений.

Частоту процессора м. понизить путем уменьш-я частоты сист. шины.Итогов. частота проц. явл.рез-том умнож-я частоты шины на множитель процессора. Замедл-е процессора вы можете осуществ., просто уменьшив множитель.

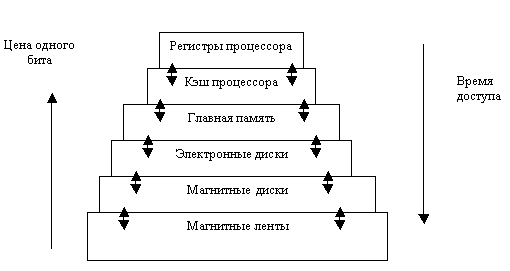

28. Иерархия памяти компьютера. Закон Мура.

В основе реализ-и иерархии памяти совр. компов лежат 2 принципа: принцип локальности обращ-ий и соотнош-е стоимость/производительность. Принцип локальности обращений: больш-во программ не выполняют обращ-ий ко всем своим командам и данным равновероятно, а оказывают предпочтение некот. части своего адресн. простр-ва.

Иерархия пам. совр. компов строится на неск. ур-нях, причем более выс. ур-нь меньше по объему, быстрее и имеет больш. стоимость в пересчете на байт, чем более низк. ур-нь. Ур-ни иерархии взаимосвязаны: все данные на 1 ур-не м. б. также найдены на более низк. ур-не, и все данные на этом более низк. ур-не м. б. найдены на следующ. нижележащ. ур-не и т. д., пока мы не достигнем основания иерархии.

Иерархия пам. обычно сост. из многих ур-ней, но в кажд. момент времени мы имеем дело только с 2 близлежащ. ур-нями. Мин. ед. инф-ции, кот. м. либо присутств., либо отсутствов. в 2уровневой иерархии, наз. блоком. Размер блока м. б. либо фиксированным, либо переменным. Если этот размер зафиксирован, то объем памяти является кратным размеру блока.

Успешн. или неуспешн. обращ-е к более выс. ур-ню наз. соответств. попаданием (hit) или промахом (miss). Попадание – обращ-е к объекту в памяти, кот. найден на более выс. ур-не, а промах означ., что он не найден на этом ур-не. Доля попаданий (hit rate) или коэффициент попаданий (hit ratio) - доля обращ-й, найден. на более выс. ур-не. Иногда она представл-ся %. Доля промахов (miss rate) - доля обращений, кот. не найдены на более выс. ур-не.

Закон Мура (1965 год): емкость каждой нов. микросхемы памяти удваив-ся по сравн-ю с ее предшественницей, а сама нов. микросхема появл-ся кажд. 18-24 мес.. Мур отметил, что производительность компов будет увеличив-ся экспоненциально по времени.

Этот закон описыв. не только рост емкости оператив. пам., он часто использ-ся для опр-я ст. роста быстродействия процессоров и емкости жестк. дисков. За 26 лет кол-во транзисторов процессора увелич. в 18 тыс. раз: от 2,3 тыс. в процессоре 4004 до 140 млн. в Pentium III Xeon. Предполагалось, что к 2007 году компания Intel выпустит процессоры с раб. частотой свыше 20 ГГц, соде. более 1 миллиарда транзисторов.

29.Построение и характеристики оперативной памяти. Микросхемы. Модули памяти.

Оперативная память (ОЗУ – опер. запоминающ. устр-во) – память, часть сис-мы пам. ЭВМ, в кот. процессор м. обрат-ся за 1 операцию. Предназнач. для времен. хран-я данных и команд, необх. процессору для выполн-я им операций. Опер. память передаёт процессору команды и данные непоср-но, либо через кэш-память. Кажд. ячейка опер. пам. им. свой индивид. адрес. Ячейка памяти – часть запоминающ. устр-ва ЭВМ для хр-я 1 машин. слова (числа) или его части (например, 1 байта). Общ. число ячеек пам. всех запоминающ. устр-в опр.т ёмкость пам. ЭВМ.

В совр. вычислит. устр-вах, операт. память выполн. по технологии пам. с произв. доступом (random access memory, RAM) – 1 из видов пам., позволяющ. в люб. момент времени получ. доступ к люб. ячейке по её адресу на чтение или запись. Предназнач. для записи, хр-я и считыв-я инф-ции в проц. её обр-ки. Всю память с произв. доступом (RAM) м. разделить на 2 типа: DRAM (динамическая RAM) и SRAM (статическая RAM).

Термин опер. память часто обознач. не только микросхемы, кот.составл. устр-ва пам. в сис-ме, но включ. и такие понятия, как логич.отображ-е и размещ-е. Логич. отображ-ие —сп-б представл-я адресов пам. на фактически установл. микросхемах. Размещение — это располож-е инф-ции (данных и команд) опр. типа по конкр. адресам памяти системы.

Микросхемы опер. пам. (RAM) иногда наз. энергозависимой памятью: после выключ-я компа данные, храним. в них, будут потеряны,

Физ-ски опер. память в сис-ме предст.т собой набор микросхем или модулей, содерж.микросхемы, кот. подключ-ся к сист. плате. Эти микросхемы или модули м. иметь разл. характ-ки и, чтобы функц.правильно, д. б. совместимы с сис-мой, в кот. устанавливаются.

Сущ. 2 типа модулей DIMM. Модули пам. DIMM об-но содерж. стандартн. микросхемы SDRAM(синхр. динамич. пам.с произв. доступом) или DDRSDRAM(синхр. динамич. память с произв. доступом и удвоен.скоростью передачи данных).

Сущ. 3 физич. типа модулей RIMM: 16/18-разрядная версия со 184 выводами, 32/36-разр-я версия, имеющ. 232 вывода, и 64/72-разр.версия, содерж. 326 выводов.

В сист. платах исп-ся неск-ко типов микросхем пам.. Больш-во из них одноразр-е, но емкость их различна. Как правило, емкость модулей памяти кратна 4, поскольку матрица, на основе которой создают микросхемы памяти, явл. квадратной. 4-кратное увелич-е емкости подразумевает увелич-е кол-тва транзисторов в 4 раза. Емкость совр. модулей DIMM составляет 256 Мбайт – 4 Гбайт.

30.Особенности организации микросхем памяти по технологии DDR.

DDR SDRAM (синхр. динамич. пам.с произв. доступом и удвоен. скоростью передачи данных) — тип комп. пам., используем.в вычислит. технике в кач-ве операт.ивной и видеопамяти. Пришла на смену памяти типа SDRAM.

При использ-ии DDR SDRAM достиг-ся удвоенная скорость работы, нежели в SDRAM, за счёт счит-я команд и данных не только по фронту, как в SDRAM, но и по спаду тактов. сигнала. За счёт этого удв-ся скорость передачи данных без увелич-я частоты тактов. сигнала шины памяти. Таким образом, при работе DDR на частоте 100 МГц мы получ. эффект. частоту 200 МГц (при ср-и с аналогом SDR SDRAM). Специфич. режимом работы модулей памяти явл. двухканальный.

Ширина шины памяти сост. 64 бита, т. е. по шине за 1 такт одновр-но перед-ся 8 байт. В рез-те получ. сл. ф-лу для расч. макс. скорости передачи для зад. типа пам.: тактовая частота шины памяти x 2 (передача данных 2 за такт) x 8 (число байтов передающихся за 1 такт). Внутр.я шина данных имеет ширину в 2 р. больше внешней. При передаче данных сначала перед-ся 1 половина шины данных по фронту тактов. сигнала, а затем 2 половина шины данных по спаду.

Модули DDR SDRAM вып. в форм-факторе DIMM. На кажд. модуле располож. неск-ко одинаков. чипов пам.и конфигурацион. чип SPD. Чипы м. располаг-ся на 1 или 2 сторонах модуля. Макс.умещающееся на DIMM кол-во — 36 (9x4).

Чипы, им. 4- или 8-ми битную шину данных. Чтобы обеспеч. более шир. полосу (например DIMM требует 64 бита и 72 бита для памяти с ECC), чипы связ-ся в ранги. Ранг пам. им. общ. шину адреса и дополняющ. др. друга линии данных. На 1 модуле м. размещ-ся несколько рангов. Но если нужно больше памяти, то добав. ранги можно и дальше, установкой неск.модулей на 1 плате и используя тот же принцип: все ранги сидят на 1 шине, только чип селекты разные - у каждого свой. Больш. кол-во рангов электич-ки нагруж. шину, точнее контроллер и чипы памяти, и замедл. их работу. Отсюда нач.прим. многоканальную архитектуру, кот. позвол. также независимо обращаться к неск.м модулям.

31.Регенерация оперативной памяти. Сравнение оперативной памяти и кэш-памяти.

Опер. пам. изготав-ся на основе конденсаторов небольш. ёмкости, кот. быстро теряют заряд, поэтому инф-цию прих-ся обновлять через опр. периоды врем. во избеж-е потерь данных. Этот процесс наз. регенерацией памяти. Он реализ-я спец. контроллером, установл. на мат. плате или на кристалле центр. процессора. На протяж. времени, назыв. шагом регенерации, в опер. пам. перезап-ся целая строка «ячеек», и через 8-64 мс обновл-ся все строки памяти. Адресная ячейка опер. пам. хранит 1 байт, а поскольку байт состоит из 8 битов, то в ней есть 8 битовых ячеек. Каждая битовая ячейка микросхемы опер. памяти хранит электрич. заряд.

Регенерация пам. происх. очень быстро. Кажд. сек. несколько раз обновл-ся мегабайты памяти, но стоит только на мгновение отключ.питание компа, как регенерация прекратится. Даже кратковрем. исчезнов-е напряж-я в сети приводит к стир-ю опер. памяти и «сбросу» компа.

Из нов. технологий регенерации м. выдел.ить тип регенерации PASR, примен. в чипах пам. SDRAM с низк. ур-нем энергопотребл-я. Регенерация «ячеек» вып-ся только в период ожид-я в тех банках памяти, в кот.им-ся данные. Пар-но с этой технологией реализ-ся метод TCSR, кот. предназнач.для регулировки скорости процесса регенерации в зав. от раб. темп-ры.

Сущ. тип памяти, соверш-но отличный от др., —статическая опер. память(кэш) . Она назв. так потому, что, в отличие от динамич. опер. памяти(DRAM), для сохр-я ее содержимого не треб-ся периодич. регенерации. Но это не единств. ее преим-во. SRAM им. более выс. быстродействие, чем динамич. опер. память, и м. работать на той же частоте, что и совр. процессоры, время доступа SRAM не более 2 нс.

Кэш-память раб. на тактов. частотах, близких, или даже равных, тактов. частотам процессора, обычно именно эта память непосредств. исп-ся процессором при чтении и записи. Во время чт-я данные в высокоскоростн. кэш-память предв-но запис-ся из опер. пам. с низк. быстродействием. Эфф-сть кэш-памяти выр. коэф-нтом совпадения,( коэфф-нтом успеха). Коэф-нт совпадения = отнош-ю кол-ва удачн.обращ-й в кэш к общ. кол-ву обращений.

32. Задачи, организация и характеристики кэш-памяти

Кэш-память (Static RAM — SRAM) –быстродействующ. буферн.память между процессором и осн. памятью (буфер данных, буфер адреса). Кэш служит для частичн. компенсации разницы в скорости проц. и осн. памяти - туда попадают наиб. часто используемые данные. Когда процессор 1 раз обращ-ся к ячейки памяти, ее содержимое пар-но копир-ся в кэш, и в случае повт. обращ-я в скором врем. м. б. с гораздо больш. скоростью выбр. из кэша.

Время доступа SRAM не более 2 нс; это означ., что такая память м. раб. синхронно с процессорами на частоте 500 МГц или выше.

Однако для хр-я кажд. бита в констр-и SRAM исп-ся кластер из 6 транзисторов. Использ-е транзисторов без каких-либо конденсаторов означ., что нет необх-сти в регенерации. Пока под-ся питание, SRAM будет помнить то, что сохранено. Больш. число транзисторов и кластеризов.их размещ-е не только увелич. габариты микросхем SRAM, но и значит. повыш. стоимость технологич. процесса по ср-ю с аналогич. пар-ми для микросхем DRAM.

Эф-сть кэш-памяти выр. коэффициентом совпадения, или коэффициентом успеха. Коэффициент совпадения = отношению кол-ва удачн. обращ-й в кэш к общ. кол-ву обращ-ий. Попадание — это событие, сост. в том, что необх. процессору данные предв-но считыв-ся в кэш из опер. пам., иначе говоря, в случае попад-я процессор м. считыв.данные из кэш-памяти. Неудачн. обращ-ем в кэш счит-ся такое, при кот. контроллер кэша не предусмотр. потреб-сти в данных, нах. по указан. абсолютн.адресу.

Замедление обусловл. периодом ожидания (wait state). Если процессор нах.я в сост. ожидания, то на протяжении всего цикла (такта) никакие операции не вып-ся. Процессор «ждет», пока необх. данные поступят из более медл. опер. пам.. Поэтому именно кэш-память позвол.сократить кол-во «простоев» и повыс. быстродействие компьютера в целом.

В совр. персональн. компах обычно предусмотр. 2 типа кэш-памяти: кэш-память 1 уровня (L1) и кэш-память 2 уровня (L2). Кэш-память 1 уровня также наз.встроенным, или внутренним, кэшем; он непосредств. встроен в процессор и факт-ски явл. частью микросхемы проц..

Кэш-память 2 ур-ня наз. вторичн., или внешн., кэшем; он устанавл-ся вне микросхемы процессора. Первонач. она устанавлив. на системной плате.

Кэш-память раб. синхронно с шиной процессора, что повыш. ее быстродействие и эффективность.

33. Назначение базовой системы ввода-вывода (BIOS)

ВIOS (Basic Input/Output System — базов. система ввода/вывода) — это программa, предназнач. для первонач. запуска компа, инициализации и настройки оборуд-я, подключ. к мат. плате, и обеспеч-я ф-ций ввода/вывода. BIOS запис-ся в микросхему пост. пам., кот. располож. на сист. плате.

Изнач. основн. назнач-ем BIOS было обслуж-е устр-в ввода/ вывода (клавиатуры, экрана и дисковых накопителей), поэтому ее и назв. «базов. система ввода/вывода». В совр. компах BIOS вып. неск-ко ф-ций:

• Запуск компьютера и процедура самотестирования (POST). Программа, располож. в микросхеме BIOS, загр-ся 1 после включ-я питания компра. Она и провер. установл. оборуд-е, настраив. устр-ва и готов. их к работе. Если во вр.самотестир-я будет обнаруж. неисправность оборуд-я, то процедура POST будет остановл. с выводом соответств. сообщения или зв. сигнала. Если же все проверки прошли успешно, самотестирование заверш-ся вызовом встроен. подпрограммы для загрузки операц. системы.

• Настройка параметров системы с помощью программы BIOS Setup. Во время процедуры POST оборуд-е настр-ся в соотв. с параметрами BIOS, хранящ. в спец. CMOS-памяти. Изменяя эти параметры, пользователи могут настраив. работу отд. устр-в и системы в целом по своему усмотрению. Редакт-ся они в спец.программе настройки, кот. также наз. BIOS Setup или CMOS Setup.

Изменяя параметры BIOS, мы можем добиться оптим. работы всех комп-в системы, однако к этому следует основ-но подготовиться, поскольку ошибочн. знач-я приводят к тому, что сис-ма будет раб. нестабильно или не будет раб. вообще.

• Поддержка функций ввода/вывода с помощью программных прерываний BIOS. В составе сист.BIOS есть встроен. ф-ции для раб.с клавиатурой, видеоадаптером, дисководами, жесткими дисками, портами ввода/вывода и др. Эти ф-ции широко исп-ся в операц. системах, подобных MS-DOS, и практически не исп-ся в совр. версиях Windows.