4 семестр / ППЭВС. 4 семестр. Лекция 6

.pdf

Лекция 6.

Прерывания. Основные сведения.

Прерывания – особым образом построенная операция приостановки основной программы и выполнения подпрограммы с дальнейшим возвратом в основную программу.

Прерывания могут быть программные, аппаратные и исключительные ситуации: ошибки, ловушки и аварийные завершения.

Иначе говоря, прерывания могут генерировать коды, записанные в самой программе, или коды, сгенерированные по запросам от внешних устройств или от внешних программ.

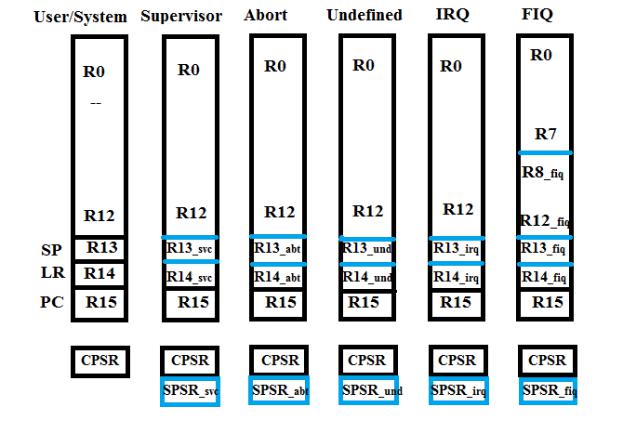

Если вернуться к рассмотрению режимов работы процессорной системы, то режимы User и System - это текущее исполнение программы, а остальные устанавливаются при получении кода соответствующего прерывания.

Поэтому для 5-ти режимов в блоке регистров необходимо производить

объединения регистров и подключение дополнительных стековых областей.

Врежимах работы без прерываний все регистры работают автономно.

Врежимах, возникающих по причине появления прерывания, для SP и LR образуются стеки, а также добавляется стек для статуса. В режиме FIQ, где необходимо быстро обслужить запрос, выделяется специальный стек из регистров R8 – R12.

Первые действия процессора при поступлении сигнала о любом прерывании:

1.Сохранение точки выхода в основную программу: каждый раз, при поступлении кода прерывания, состояние PC, указывающее на адрес следующей команды, копируется в LR. Глубина стека,

образованного для LR, определяет количество возможных вложений;

2.Сохранение текущего статуса из основной программы: состояние

CPSR копируется в стек с указателем в SPSR;

3. Установка нового статуса, соответствующего типу прерывания -

Changes bits 4—0 of CPSR, sets I and F;

4.В зависимости от нового статуса запись вектора в программный счетчик - Vector address PC.

Таблица векторов прерываний.

Адрес |

Причина |

Приоритет |

Режим |

0х000 |

Reset |

1 |

Supervisor |

0х004 |

Unimplemented instruction |

6 |

Undefined |

0х008 |

Software interrupt |

- |

Supervisor |

0х00C |

Instruction access violation |

5 |

Abort |

0x010 |

Data access violation |

2 |

Abort |

0x018 |

IRQ |

4 |

IRQ |

0x01C |

FIQ |

3 |

FIQ |

5.Из таблицы векторов в программный счетчик записывается адрес выхода на подпрограмму - Start address PC.

6.Снимаются маски с принятия внешних запросов – сбрасываются I и F.

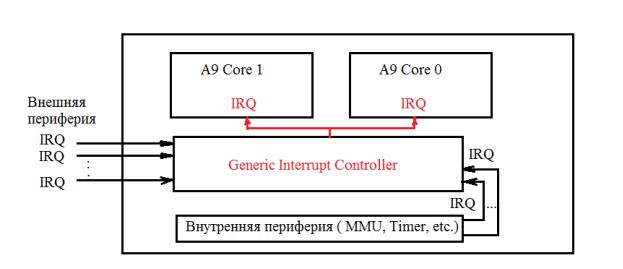

Аппаратные прерывания в процессорных системах линейки ARM (начиная с ARM7) обрабатываются с помощью контроллера прерываний GIC

– Generic Interrupt Controller.

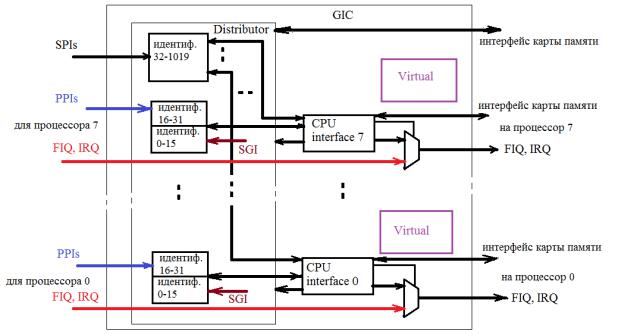

Контроллер входит в структуру объединенного ядра процессора (например, CortexA9), принимая запросы как от внешних, так и от внутренних источников, способных генерировать запросы на аппаратные прерывания. Для CortexA9 GIC способен обработать запросы от 255 источников. Все источники прерываний имеют свои идентификационные номера. Интерфейс CPU способен распознать 1020 источников. Группы по ID образуются в распределителе. Группа запросов под обслуживание любым процессором имеет ID от 32 по 1019. Группы индивидуальных запросов имеют ID от 0 до 31. При этом, программно-генерируемые и внешние источники объединяются в банки для каждого из процессоров. SGI имеют ID – от 0 до 15, PPI имеют ID от 16 до 31. Количество обслуживаемых процессоров в объединенном ядре возможно от 1 до 8-ми. Контроллер имеет два основных блока: распределитель и интерфейсный блок. Интерфейсный блок определяет степень приоритета поступившего запроса, сравнивая его с приоритетом обрабатываемого прерывания. Производит анализ маски приоритета и установки вытеснения прерывания. Далее, при положительном результате анализа, запрос передается на процессор.

Типы сигналов запросов на прерывания, поступающие на контроллер.

Прерывания от внешних источников могут быть:

-индивидуальными для каждого процессора (PPI – Private Peripheral

Interrupt);

-общие, т.е. поступающие на обработку любому свободному процессору

(SPI – Shared Peripheral Interrupt).

Эти типы запросов могут определяться как по уровню поступающего сигнала (Level-sensitive), так и по его изменению, с помощью регистра краевого захвата (Edge-triggered).

Прерывания от внутренних источников, это программно генерируемые прерывания (SGI – Software-generated Interrupt). Запрос на прерывание этого типа всегда определяется с помощью краевого захвата.

Есть также запросы, обслуживаемые виртуальной машиной. Они не поступают на распределитель.

Различают следующие состояния сигнала прерывания, поступающего от контроллера на процессор:

Неактивный - прерывание не активно, или подвешено;

Подвешенный – запрос опознан и принят, но поставлен на ожидание;

Активный – запрос, поступивший на контроллер, передан процессору и опознан, но обслуживание его не завершено;

Активный и подвешенный – процессор обслуживает запрос, а контроллер на это время подвешивает следующий запрос от этого же источника.

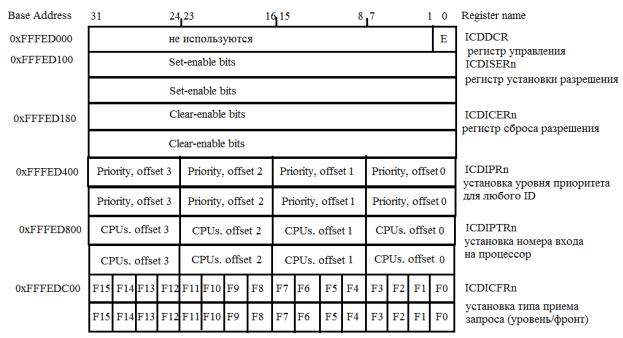

Регистры распределителя

Распределитель принимает запросы, определяет их приоритеты и направляет в интерфейсный блок. Функции распределителя:

-программирование возможности пересылки любого прерывания на CPUинтерфейс (ICDDCR);

-программирование возможности или невозможности приема данного

прерывания (ICDISERn, ICDICERn);

-установка уровня приоритета данного прерывания (ICDIPRn);

-установка номера входа на процессор для данного прерывания (ICDIPTRn);

-определение типа приема запроса: по уровню или по фронту, с помощью краевого захвата (ICDICFRn).

Кроме того, распределитель:

-определяет принадлежность прерывания к группе уровня защищенности. (Группа 0 – защищенные прерывания, на вход процессора допускаются как IRQ, так и FIQ запросы. Группа 1 – незащищенные прерывания – только

IRQ);

-осуществляет пересылку программно-генерируемых запросов, SGI, на один или несколько процессорных входов;

-определяет состояние данного прерывания;

-запускает механизм программной установки или сброса подвешенного запроса.

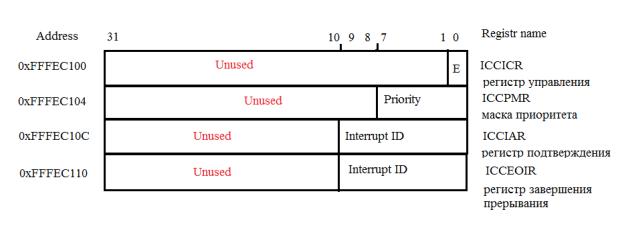

Регистры CPU-интерфейса.

CPU-интерфейс формирует:

-возможность посылки запроса;

-подтверждение прерывания;

-индикацию завершения обработки прерывания процессором;

-определение порядка вытеснения прерывания для процессора;

-распределение степени приоритета подвешенных прерываний для процессора.

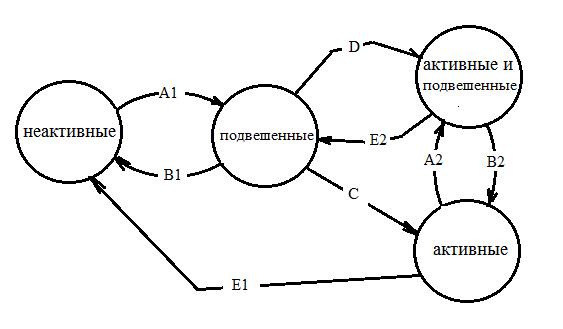

Мы упоминали, что запросы на прерывание могут находиться в одном из 4-х режимов. Переходы из одного режима в другой управляются с помощью конечного автомата.

При рассмотрении переходов будем обращаться только к запросам от внешних источников.

1.Случаи переходов A. Подвешенное состояние. На этапе нахождения в распределителе запрос ставится в очередь, если периферия подтверждает запрос (A1). На этапе нахождения в CPU-интерфейсе запрос, оказывающийся ниже приоритетом поступившего следом запроса от того же источника, ставится в очередь и отмечается при этом в регистре очереди на ожидание (A2).

2.Случаи переходов B. Удаление подвешенного состояния. Запрос может быть снят с очереди в случае снятия подтверждения периферией (B1), или в случае подтверждения необходимого приоритета, сохранении «1» в регистре краевого захвата и установки бита сброса с очереди. В этом случае запрос переходит на обслуживание, т.е. становится активным (B2).

3.Случай перехода С. При наличии необходимого приоритета в регистре CPU-интерфейса.

4.Случай перехода D. Повторный запрос от того же источника. Прерывание разрешено, происходит проверка приоритета. На время анализа приоритетов запрос ожидает. Если за время анализа запрос будет снят, произойдет вариант B1. Если приоритет этого запроса окажется выше обрабатываемого от того же источника, вариант B2.

5.Случаи перехода E. Обработка закончена, прочтение регистра окончания обработки дает E1. Запрос от другого источника с более высоким приоритетом выталкивает запрос – E2.

При рассмотрении вариантов ID мы не учитывали номеров с 1020 по 1023, которые имеют специальное назначение. Например, ID 1023 всегда воспринимается, как ложный запрос.