- •1)Обобщенная структурная схема эвм.

- •2)Основные булевы функции от двух переменных.

- •3)Rs- триггер.

- •1)Классификая эвм

- •2)Минимизация булевых функций.

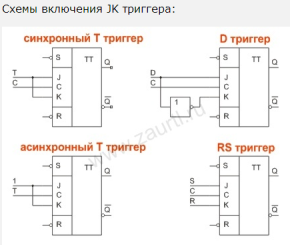

- •3)Jk –триггер

- •1)Принцип программного управления.

- •2)Выполнение операции алгебраического сложения в д кодах (система 2421).

- •1)Представление чисел. Формы представления чисел.

- •Вещественные числа (числа с плавающей точкой)

- •2)Rs- триггер.

- •3)Суммирующие и вычитающие счетчики.

- •1)Способы задания булевой функции

- •2) Элементы эвм.

- •3)Мультиплексор. Демультиплексоры.

- •1)Представление чисел. Формы представления чисел.

- •2)Счетчики. Классификация.

- •3)Безадресные зу.

- •1)Выполнение операции алгебраического сложения в д кодах (система 2421).

- •2)Организация системы прерываний.

- •3) Последовательные и параллельные регистры.

- •1)Запоминающие устройства (зу). Классификация.

- •2)Запоминающие устройства (зу). Классификация. То же самое, что и первый вопрос(!)

- •3)Последовательные и параллельные регистры.

- •1)Озу. Статическая и динамическая память.

- •2, Организация мультипрограммной работы эвм.

- •3) Регистр на rs-триггерах с последовательным занесением справа и параллельной выдачей.

- •1, Процессоры эвм. Классификация.

- •2, Локальные сети.

- •Назначение и классификация процессоров

- •Назначение и классификация процессоров

- •Алгебраическое сложение в дополнительном коде

- •1)Уу схемно-логического типа.

- •2)Сумматоры.

- •3)Озу. Статическая и динамическая память.

- •1)Зу с произвольным доступом.

- •2)Дешифраторы.

- •3)Микропрограммное уу.

- •Память динамического типа ( dram)

- •Память статического типа (sram))

- •2) Мультиплексор. Демультиплексор.

- •Сегментная защита памяти

- •2) Обобщенная структурная схема алу

- •3)Однотактный двухступенчатый rs- триггер в базисе или-не с запрещающими связями

- •1) Обобщенная структурная схема устройства управления (уу).

- •2) Зу с последовательным доступом.

- •3) Однотактный двуступенчатый d- триггер в базисе или-не с запрещающими связями.

- •1) Микропрограммное уу.

- •2) Зу с циклическим доступом.

- •3) Однотактный двуступенчатый d- триггер в базисе и-не с инвертором.

- •1)Организация мультипрограммной работы эвм.

- •2)Обобщенная структурная схема алу

- •3) Двухступенчатый jk-триггер с запрещающими связями.

- •1)Обобщенная структурная схема алу

- •2.Сумматоры.

- •3) Двухступенчатый jk-триггер с запрещающими связями.

- •1)Архитектура вычислительных комплексов и систем

- •2)Однотактный двухступенчатый rs- триггер в базисе или-не с запрещающими связями

- •Параллельные регистры

- •Сдвигающие регистры

- •2. Зу с произвольным и с последовательным доступами

1)Способы задания булевой функции

Задать Булеву функцию – это указать, при каких комбинациях переменных она равна 0, а при каких равна 1. F = F(A,B,C,…), где A,B,C,… - аргументы функции ϵ {0,1}; F – результат или сама функция ϵ {0,1}.

Существуют следующие способы задания Булевых функций:

1. Словесный (описательный) способ – функция задается в виде текста. Пример: F(A,B,C)=1, если аргументы в данном наборе имеют нечетное количество единиц (или если два любых аргумента функции равны 0).

2. Табличный способ задания Булевой функции – строится таблица истинности, в которой указываются номера наборов, соответствующее состояние аргументов и значение самой функции.

3. Алгебраический способ задания Булевых функций

Исходным для такого способа является табличное задание Булевых функций. Аналогичная форма необходима для перехода к структурной схеме, для минимизации Булевой функции с целью последующего размещения цифрового устройства на кристалле. Существуют два варианта задания функции алгебраическим способом:

Нормальная дизъюнктивная форма или задание Булевых функций по единицам.

Алгоритм задания следующий: из таблицы выбираются номера наборов, где функция равна 1, и строится сумма элементарных произведений этих наборов, при этом если переменная равна 0, то она берется с инверсией (элементарное произведение - произведение всех переменных для данного набора).

Нормальная конъюнктивная форма (или задание Булевых функций по нулям).

Из таблицы выбираются наборы, где функция равна 0 и строиться произведение элементарных сумм для этих наборов. Если переменная равна 1, то она берется с инверсией. (Элементарная сумма – сумма всех переменных для данного набора).

4. Числовой способ задания Булевых функций - является наиболее компактным для задания Булевых функций, но крайне неудобен для их минимизации. Также существует в двух вариантах (по единицам и по нулям).

По единицам: в этом случае под знаком суммы в скобках перечисляются те номера наборов, где функция равна единице

По нулям: под знаком произведения в скобках перечисляются номера наборов, где функция равна нулю

2) Элементы эвм.

Логический элемент «И» |

|

|

На входы А и В логического элемента последовательно подаются четыре пары сигналов различных значений, на выходе получается последовательность из четырех сигналов, значения которых определяются в соответствии с таблицей истинности операции логического умножения. |

|

|

Логический элемент «ИЛИ» |

|

|

На входы А и В логического элемента последовательно подаются четыре пары сигналов различных значений, на выходе получается последовательность из четырех сигналов, значения которых определяются в соответствии с таблицей истинности операции логического сложения |

|

|

Логический элемент «НЕ» |

|

|

На вход А логического элемента последовательно подаются два сигнала, на выходе получается последовательность из двух сигналов, значения которых определяются в соответствии с таблицей истинности логической инверсии. |

|

|

Основные функциональные элементы ЭВМ: дешифратор, шифратор, триггерные схемы различных типов, счетчик.

Дешифратор. Дешифратором называется комбинационная схема, имеющая n входов и 2n выходов и преобразующая двоичный код на своих входах в унитарный код на выходах. Унитарным называется двоичный код, содержащий одну и только одну единицу, например 00100000. Условно-графическое обозначение дешифратора на три входа приведено на рис.:

Рис. 1.1. Условно-графическое обозначение трехвходового дешифратора

Шифратор. Шифратор – схема, имеющая 2n входов и n выходов, функции которой во многом противоположны функции дешифратора. Эта комбинационная схема в соответствии с унитарным кодом на своих входах формирует позиционный код на выходе

![]()

Рис. 1.2. Условно-графическое обозначение шифратора на 4 входа

Триггер. Триггер – электронная схема, обладающая двумя устойчивыми состояниями. Переход из одного устойчивого состояния в другое происходит скачкообразно под воздействием управляющих сигналов. При этом также скачкообразно изменяется уровень напряжения на выходе триггера.

Триггеры служат основой для построения регистров, счетчиков и других элементов, обладающих функцией хранения.

Главной частью любого триггера является запоминающая ячейка (ЗЯ). Схема запоминающей ячейки на элементах "И-НЕ" представлена на рис. 1.3.

Рис. 1.3. Запоминающая ячейка на элементах "И-НЕ"

Асинхронный Т триггер – счетный Т триггер, каждые2 сигнала на входе Т формируют 1 сигнал на выходе.

Синхронный Т триггер – счетный триггер, каждые 2 сигнала на входе С формируют 1 сигнал на выходе, если на входе Т присутствует логическая 1

Синхронный Д триггер – реализует функцию временной задержки. Асинхронный RS триггер – элементарный цифровой автомат с двумя устойчивыми состояниями т думя входами R и S.

Счётчик числа импульсов — устройство, на выходах которого получается двоичный (двоично-десятичный) код, определяемый числом поступивших импульсов. Счётчики могут строиться на двухступенчатых D-триггерах, T-триггерах и JK-триггерах.