- •1)Обобщенная структурная схема эвм.

- •2)Основные булевы функции от двух переменных.

- •3)Rs- триггер.

- •1)Классификая эвм

- •2)Минимизация булевых функций.

- •3)Jk –триггер

- •1)Принцип программного управления.

- •2)Выполнение операции алгебраического сложения в д кодах (система 2421).

- •1)Представление чисел. Формы представления чисел.

- •Вещественные числа (числа с плавающей точкой)

- •2)Rs- триггер.

- •3)Суммирующие и вычитающие счетчики.

- •1)Способы задания булевой функции

- •2) Элементы эвм.

- •3)Мультиплексор. Демультиплексоры.

- •1)Представление чисел. Формы представления чисел.

- •2)Счетчики. Классификация.

- •3)Безадресные зу.

- •1)Выполнение операции алгебраического сложения в д кодах (система 2421).

- •2)Организация системы прерываний.

- •3) Последовательные и параллельные регистры.

- •1)Запоминающие устройства (зу). Классификация.

- •2)Запоминающие устройства (зу). Классификация. То же самое, что и первый вопрос(!)

- •3)Последовательные и параллельные регистры.

- •1)Озу. Статическая и динамическая память.

- •2, Организация мультипрограммной работы эвм.

- •3) Регистр на rs-триггерах с последовательным занесением справа и параллельной выдачей.

- •1, Процессоры эвм. Классификация.

- •2, Локальные сети.

- •Назначение и классификация процессоров

- •Назначение и классификация процессоров

- •Алгебраическое сложение в дополнительном коде

- •1)Уу схемно-логического типа.

- •2)Сумматоры.

- •3)Озу. Статическая и динамическая память.

- •1)Зу с произвольным доступом.

- •2)Дешифраторы.

- •3)Микропрограммное уу.

- •Память динамического типа ( dram)

- •Память статического типа (sram))

- •2) Мультиплексор. Демультиплексор.

- •Сегментная защита памяти

- •2) Обобщенная структурная схема алу

- •3)Однотактный двухступенчатый rs- триггер в базисе или-не с запрещающими связями

- •1) Обобщенная структурная схема устройства управления (уу).

- •2) Зу с последовательным доступом.

- •3) Однотактный двуступенчатый d- триггер в базисе или-не с запрещающими связями.

- •1) Микропрограммное уу.

- •2) Зу с циклическим доступом.

- •3) Однотактный двуступенчатый d- триггер в базисе и-не с инвертором.

- •1)Организация мультипрограммной работы эвм.

- •2)Обобщенная структурная схема алу

- •3) Двухступенчатый jk-триггер с запрещающими связями.

- •1)Обобщенная структурная схема алу

- •2.Сумматоры.

- •3) Двухступенчатый jk-триггер с запрещающими связями.

- •1)Архитектура вычислительных комплексов и систем

- •2)Однотактный двухступенчатый rs- триггер в базисе или-не с запрещающими связями

- •Параллельные регистры

- •Сдвигающие регистры

- •2. Зу с произвольным и с последовательным доступами

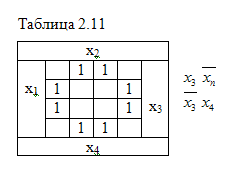

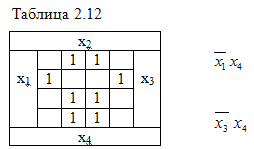

2)Минимизация булевых функций.

При проектировании цифровых автоматов широко используется методы минимизации булевых функций, позволяющие получать рекомендации для построения экономических схем цифровых автоматов. Общая задача минимизации может быть сформирована следующим образом: найти аналитическое выражение заданной булевой функции в форме, содержащей минимально возможное число букв.

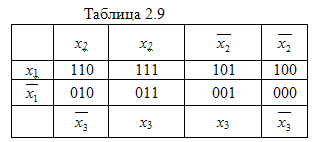

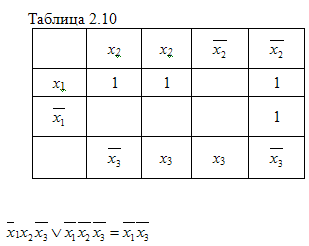

Существуют множество методов, позволяющих минимизировать заданную булеву функцию. Мы рассмотрим метод диаграмм Вейча. Этот метод позволяет быстро получать минимальную дизъюнктивную нормальную форму (МДНФ) булевой функции f небольшого числа переменных. В основе лежит задание булевых функций диаграммами некоторого специального вида, получившими название диаграмм Вейча-Карно. Для булевой функции двух переменных диаграмма Вейча-Карно имеет вид (таблица 2.6). Каждая клетка диаграммы соответствует набору переменных булевой функции в ее таблице истинности (таблица 2.7).

![]()

![]()

Для булевой функции трех переменных диаграмма Вейча имеет следующий вид (таблица 2.8).

Для

приведенных диаграмм характерно

следующее:

Для

приведенных диаграмм характерно

следующее:

1) Каждой клетке диаграммы соответствует свой набор;

2) Соседние наборы расположены рядом в строке либо в столбце.

Соседними наборами называются наборы, отличающиеся одной компонентой. Компоненты, соответствующие таким наборам, склеиваются. Например, для функции, заданной таблицей 2.10, компоненты, соответствующие паре единиц в левой части таблицы, склеиваются, и порождает элементарное произведение из двух букв:

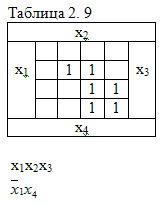

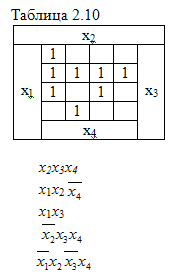

О паре единиц в правой части диаграммы можно сказать то же самое. Следует помнить, что столбцы, расположенные по краям, тоже считаются соседними. Пример. Булевы функции f1, f2, f3, f4, f5, f6 заданны диаграммами Вейча (таблицы 2.9, 2.10, 2. 11, 2. 12, 2. 13, 2. 14). Необходимо найти их МДНФ. Минимальные покрытия единиц показаны в таблицах. Там же выписаны конъюнкции, соответствующие выделенным блокам единиц.

Таблица

2.

Для

по таблице 9

по таблице 9 14

МДНФ имеет следующий вид:

14

МДНФ имеет следующий вид:

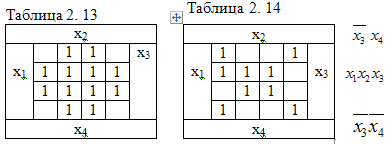

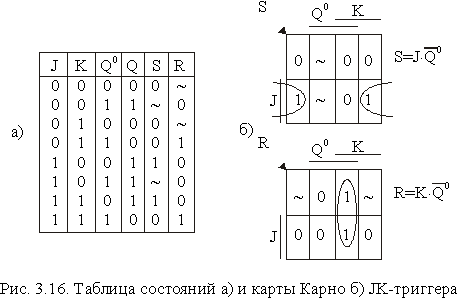

3)Jk –триггер

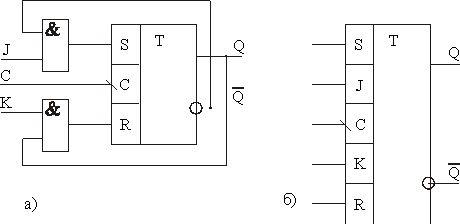

Среди триггеров особое место занимают JK-триггеры, имеющие более широкие функциональные возможности. Упрощенная таблица (таблица управления) состояний JK-триг-гера содержит четыре строки (рис. 3.15, а). Из таблицы состояний видно, что для первых трех строк (наборов переменных) входы J и K играют роль входов S и R RS - триггера. Однако, для четвертого набора переменных, когда J=K=1 состояние триггера сильно отличается от состояния RS-триггера. Для RS-триггера - это запрещенная комбинация входных переменных, а в JK-триггере меняется (инвертируется) предыдущее состояние. JK-триггер можно синтезировать (построить) на базе двухступенчатого RS-триггера, для чего следует представить функциональную схему JK-триггера как совокупность КУ и синхронного RS-триггера (рис. 3.15, б)

Для

получения

логических выражений (характеристических

уравнений) функций R и S комбинационного

устройства необходимо построить

совмещенную таблицу состояний JK и RS -

триггеров (рис. 3.16, а). Из полученных

выражений для S и R (рис. 3.16, б) следует,

что для построения JK-триггера из

двухступенчатого RS-триггера потребуется

два элемента конъюнкции (на два входа

каждый). Схема, полученная путем синтеза

JK-триггера, приведена на рис. 3.17, а.

Обозначение JK-триггера на функциональных

схемах приведено на рис. 3.17, б.

Для

получения

логических выражений (характеристических

уравнений) функций R и S комбинационного

устройства необходимо построить

совмещенную таблицу состояний JK и RS -

триггеров (рис. 3.16, а). Из полученных

выражений для S и R (рис. 3.16, б) следует,

что для построения JK-триггера из

двухступенчатого RS-триггера потребуется

два элемента конъюнкции (на два входа

каждый). Схема, полученная путем синтеза

JK-триггера, приведена на рис. 3.17, а.

Обозначение JK-триггера на функциональных

схемах приведено на рис. 3.17, б.

Рис. 3.17. Синтезируемая схема а) и графическое обозначение б) JK - триггера

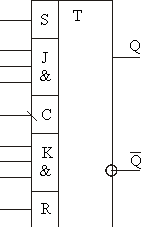

Выпускаемые промышленностью ИМС JK-триггеры могут иметь несколько входов (до трех) J и такое же количество входов K, объединенных схемами конъюнкций (рис. 3.18).

Рис. 3.18. Схемное обозначение ИМС JK – триггера, выпускаемого промышленностью

Как следует из рис. 3.18, выпускаемые промышленностью JK-триггеры в виде интегральных микросхем также имеют асинхронные входы установки “0” и “1”(R и S входы, соответственно)

Билет №3