- •1)Обобщенная структурная схема эвм.

- •2)Основные булевы функции от двух переменных.

- •3)Rs- триггер.

- •1)Классификая эвм

- •2)Минимизация булевых функций.

- •3)Jk –триггер

- •1)Принцип программного управления.

- •2)Выполнение операции алгебраического сложения в д кодах (система 2421).

- •1)Представление чисел. Формы представления чисел.

- •Вещественные числа (числа с плавающей точкой)

- •2)Rs- триггер.

- •3)Суммирующие и вычитающие счетчики.

- •1)Способы задания булевой функции

- •2) Элементы эвм.

- •3)Мультиплексор. Демультиплексоры.

- •1)Представление чисел. Формы представления чисел.

- •2)Счетчики. Классификация.

- •3)Безадресные зу.

- •1)Выполнение операции алгебраического сложения в д кодах (система 2421).

- •2)Организация системы прерываний.

- •3) Последовательные и параллельные регистры.

- •1)Запоминающие устройства (зу). Классификация.

- •2)Запоминающие устройства (зу). Классификация. То же самое, что и первый вопрос(!)

- •3)Последовательные и параллельные регистры.

- •1)Озу. Статическая и динамическая память.

- •2, Организация мультипрограммной работы эвм.

- •3) Регистр на rs-триггерах с последовательным занесением справа и параллельной выдачей.

- •1, Процессоры эвм. Классификация.

- •2, Локальные сети.

- •Назначение и классификация процессоров

- •Назначение и классификация процессоров

- •Алгебраическое сложение в дополнительном коде

- •1)Уу схемно-логического типа.

- •2)Сумматоры.

- •3)Озу. Статическая и динамическая память.

- •1)Зу с произвольным доступом.

- •2)Дешифраторы.

- •3)Микропрограммное уу.

- •Память динамического типа ( dram)

- •Память статического типа (sram))

- •2) Мультиплексор. Демультиплексор.

- •Сегментная защита памяти

- •2) Обобщенная структурная схема алу

- •3)Однотактный двухступенчатый rs- триггер в базисе или-не с запрещающими связями

- •1) Обобщенная структурная схема устройства управления (уу).

- •2) Зу с последовательным доступом.

- •3) Однотактный двуступенчатый d- триггер в базисе или-не с запрещающими связями.

- •1) Микропрограммное уу.

- •2) Зу с циклическим доступом.

- •3) Однотактный двуступенчатый d- триггер в базисе и-не с инвертором.

- •1)Организация мультипрограммной работы эвм.

- •2)Обобщенная структурная схема алу

- •3) Двухступенчатый jk-триггер с запрещающими связями.

- •1)Обобщенная структурная схема алу

- •2.Сумматоры.

- •3) Двухступенчатый jk-триггер с запрещающими связями.

- •1)Архитектура вычислительных комплексов и систем

- •2)Однотактный двухступенчатый rs- триггер в базисе или-не с запрещающими связями

- •Параллельные регистры

- •Сдвигающие регистры

- •2. Зу с произвольным и с последовательным доступами

1)Уу схемно-логического типа.

Любое цифровое устройство состоит из двух блоков: операционного и управляющего.

В операционном блоке каждая операция разделяется на микрооперации, соответствующие одному элементарному преобразованию в ЦВМ под воздействием определенных функциональных управляющих сигналов – микрокоманд. Длительность микрокоманды определяется временем выполнения микроопераций (очистка регистров, передача информации, прием информации, сдвиги и т.д.). Микрокоманда в общем случае состоит из нескольких микроопераций. Время выполнения одной микрокоманды (за исключением обращения к ОЗУ без КЭШа) называется рабочим тактом процессора. Последовательность микрокоманд, обеспечивающая выполнение одной операции (команды из системы команд ЭВМ) называется микропрограммой этой операции.

Выработка управляющих сигналов (УС) для выполнения микропрограммы осуществляется устройством управления (УУ). Таким образом, УУ служит для автоматического управления процессом вычислений, обеспечивая координацию работы всех устройств ЦВМ с помощью синхронизирующих и управляющих сигналов.

УУ (по способу построения БУО (блок управления операцией) делятся на:

-УУ со схемным формированием УС (УУ с «жесткой» логикой);

-УУ с программируемой логикой (микропрограм-е УУ).

В БУО с «жесткой» логикой последовательность управляющих сигналов вырабатывается посредством логических схем.

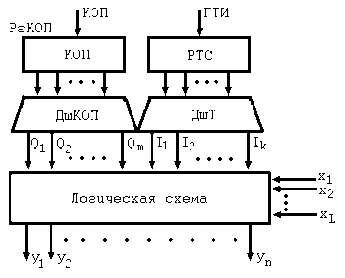

рис. 2.35. Обобщенная структурная схема УУ с «жесткой» логикой

ГТИ – генератор тактовых импульсов;

РТС – распределитель тактовых сигналов;

Q1,Q2…Qm – m-команд системы машинных команд ЭВМ;

I1,I2…Ik – количество числа тактов, необходимых для выполнения самой длинной операции;

x1,x2…xL – сигналы логических условий;

y1,y2…yn – управляющие сигналы.

Для выполнения команд «разной» (по времени) длины используются дополнительные счетчики тактов.

БУО с «жесткой» логикой строится на основе интерпретации микропрограмм для выполнения операций. Для чего на языке микроопераций описывается микропрограмма выполнения какой-либо команды из системы машинных команд ЭВМ. На основе микропрограмм выполнения машинных операций строится управляющий автомат (Мили или Мура).

2)Сумматоры.

Сумматором называют схему, осуществляющую арифметическое сложение (суммирование) двух чисел. Сумматор является одним из основных узлов АЛУ, в значительной степени определяющим скорость его работы. Различают сумматоры комбинационные и накапливающие. Комбинационный сумматор представляет собой комбинационную схему, на входы которой одновременно подаются слагаемые X и Y, а на выходе с задержкой, свойственной комбинационным цепям, в том же машинном такте формируется значение их сумм S. Накапливающий сумматор представляет собой последовательную схему, построенную на триггерах, имеющих счетный T вход и установочные RS или JK входы. В отличие от комбинационных сумматоров на накапливающий сумматор слагаемые X и Y подаются последовательно (поочередно) в разные моменты времени. Путем поочередной подачи накапливающий сумматор может суммировать любое количество поступающих на его вход чисел.

Сумматор – функциональный узел ЭВМ, предназначенный для сложения трех двоичных чисел (слагаемых и переноса из предыдущего разряда) и формирования на выходе сигналов суммы и переносов.

Классификация:

1. по числу входов: полусумматоры; одноразрядные сумматоры; многоразнядные сумматоры: последовательные; параллельные;

2. по способу организации межразрядных переносов:

с последовательным переносом; с параллельным переносом; с групповой структурой;

3. по логической структуре: комбинационные сумматоры;

накапливающие сумматоры;

4. по способу тактирования: асинхронные; синхронные;

5. в зависимости от системы счисления: двоичные; двоично-десятичные; прочие.

Базовые схемы:

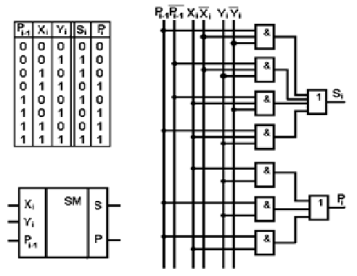

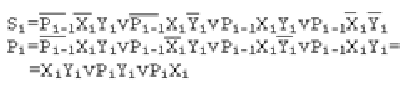

1. Одноразрядный двоичный комбинационный сумматор:

Обладает высоким быстродействием, однако сигналы Si и Pi имеют место только во время действия входных сигналов (отсутствует хранение).

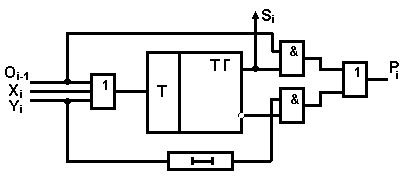

2. Одноразрядный накапливающий двоичный сумматор:

Строится на основе счетных триггеров. По сравнению с комбинационным, быстродействие ниже (последовательное поступление входных сигналов).

3.

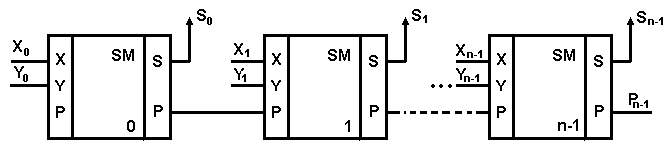

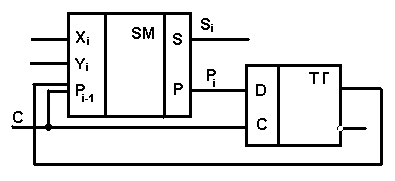

Многоразрядный последовательный

сумматор:

4. многоразрядный параллельный сумматор с последовательным переносом: