- •Содержание

- •1 Микропроцессорный комплект кр580

- •1.1 Мп вм80а. Структура. Основные режимы функционирования

- •1.2 Функционирование мп

- •1.3 Особые режимы функционирования

- •1.4 Непрограммируемые интерфейсные бис

- •1.5 Системный контроллер вк28 Системные контроллеры кр580вк28 и кр580вк38

- •1.6 Интерфейс и классификация интерфейсов

- •1.7 Параллельный адаптер вв55

- •1.8 Последовательный адаптер вв51а Синхронный режим

- •Асинхронный режим

- •1.9 Кпдп вт57. Назначение. Структура

- •Функционирование

- •1.10 Кпп вн59. Назначение. Структура

- •1.11 Контроллер клавиатуры и индикации вв 79

- •1.12 Контроллер видеотерминала кр580вг75

- •1.13 Особенности мп к1821вм8085а

- •2 Микрокрнтроллер мк51

- •2.1. Структурная схема мк51

- •2.1.1. Арифметическо-логическое устройство

- •2.1.2. Резидентная память

- •2.1.3. Устройство управления и синхронизации

- •2.2. Порты ввода/вывода информации

- •Доступ к внешней памяти

- •2.3. Таймер/счетчик

- •2.4. Последовательный интерфейс

- •2.5. Система прерываний

1.8 Последовательный адаптер вв51а Синхронный режим

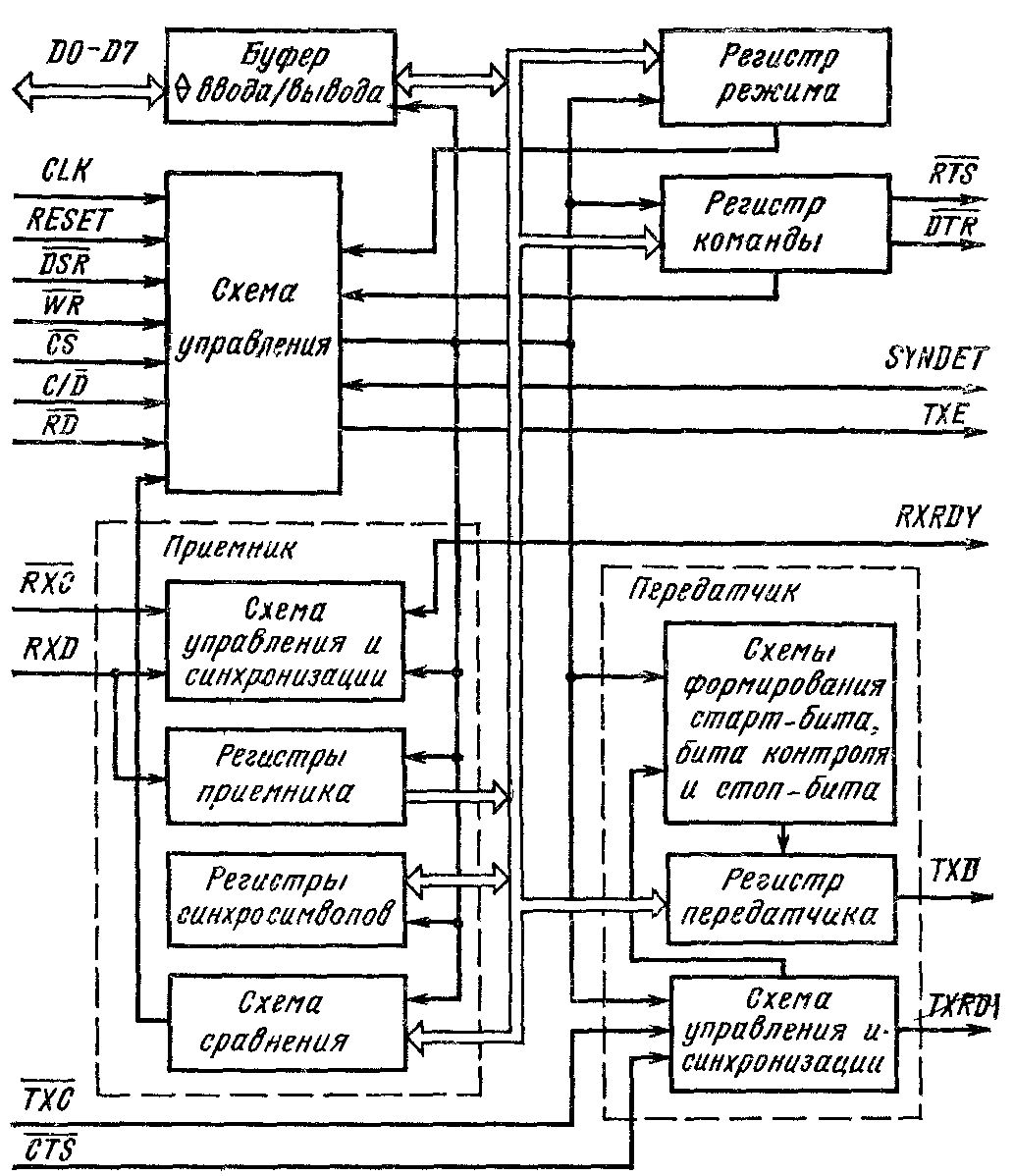

Микросхема КР580ВВ51А представляет собой однокристальное программируемое устройство для синхронно-асинхронных приемо-передающих каналов последовательной связи. Она служит для преобразования параллельного кода, полученного из микропроцессорной системы, в последовательный поток символов со служебными битами: старт, стоп, контроль, и выдает этот поток в канал связи с различной скоростью. Данная микросхема также может выполнять обратное преобразование последовательного потока символов со служебными битами в параллельное 8-разрядное слово, которое поступает в канал данных системы. Имеется пять режимов работы микросхемы КР580ВВ51А: асинхронная передача, асинхронный прием, синхронная передача, синхронный прием с внутренней синхронизацией, синхронный прием с внешней синхронизацией. В каждом режиме может быть проведен контроль на четность или нечетность, а длина передаваемых символов изменена в пределах 5...8 бит.

Режим работы микросхемы КР580ВВ51А задается предварительно вводимой инструкцией режима. Следует учесть, что перед началом работы с микросхемой необходимо выполнить определенную последовательность команд: 1) установка исходного состояния; 2) запись инструкции режима; 3) запись синхросимвола 1; 4) запись синхросимвола 2; 5) запись инструкции команды. При этом команда «Запись синхросимвола 2» или команды «Запись синхросимвола 1» и «Запись синхросимвола 2» могут отсутствовать, что определяется инструкцией режима.

Структурная

схема КР580ВВ51А представлена на рис.

1.15. Микросхема состоит из приемника,

передатчика, регистра режима, регистра

команды, схемы управления и буфера

ввода/вывода. Восьмиразрядные регистры

режима и команды предназначены для

хранения соответственно инструкции

режима и инструкции команды, поступающих

с магистрали D0 - D7 через буфер ввода/вывода.

Схема управления на основе анализа

входных сигналов

,

RESET,

![]() ,

определяет направление передачи

информации, ее вид и формирует необходимые

управляющие сигналы. Приемник получает

последовательность символов, поступающих

на вход RXD, выделяет данные, преобразует

их в параллельный код и записывает в

буфер ввода/вывода. (см. табл. 1.6)

,

определяет направление передачи

информации, ее вид и формирует необходимые

управляющие сигналы. Приемник получает

последовательность символов, поступающих

на вход RXD, выделяет данные, преобразует

их в параллельный код и записывает в

буфер ввода/вывода. (см. табл. 1.6)

Таблица 1.6

Входной сигнал |

Направление и вид информации |

|||

|

|

|

RESET |

|

0 |

0 |

1 |

0 |

Приемопередатчик->ЦПУ (данные) |

0 |

1 |

0 |

0 |

ЦПУ-»-приемопередатчик (данные) |

1 |

0 |

1 |

0 |

Приемопередатчик->ЦПУ (состояние) |

1 |

1 |

0 |

0 |

ЦПУ-приемопередатчик (управление) |

X |

X |

X |

1 |

Информация сохраняется; шина DO - D7 устанавливается в состояние «Выключено» |

Примечание. 1 - сигнал высокого уровня; 0 - сигнал низкого уровня; X - состояние входа безразлично.

Рисунок 1.15 -Структурная схема КР580ВВ51А

В

режиме синхронного приема с внутренней

синхронизацией работа приемника

начинается с поиска синхросимволов.

Принимаемая информация непрерывно

сравнивается с содержимым регистров

синхросимволов, и при их совпадении

приемник переходит в режим синхронизации.

На выводе SYNDET «Вид синхронизации»,

работающем как выход, устанавливается

напряжение высокого уровня. В режиме

синхронного приема с внешней синхронизацией

на вывод SYNDET, работающий как вход,

подается напряжение синхронизации,

которое разрешает прием информации по

входу приемника с частотой

синхроимпульсов, поступающих на вход

![]() «Синхронизация приемника». При этом

длительность сигналов, поступающих

на вход SYNDET, должна быть больше или равна

периоду частоты синхронизации

.

Передатчик принимает входную информацию,

поступающую параллельным кодом через

буфер ввода/вывода со входов D0 - D7,

преобразует ее в последовательный код,

добавляет служебную информацию

(старт-биты, стоп-биты, синхросимволы,

биты четности) в зависимости от

запрограммированного режима работы и

выдает их на выход передатчика TXD.

Синхронизация выходных данных

осуществляется сигналом, подаваемым

на вход

«Синхронизация приемника». При этом

длительность сигналов, поступающих

на вход SYNDET, должна быть больше или равна

периоду частоты синхронизации

.

Передатчик принимает входную информацию,

поступающую параллельным кодом через

буфер ввода/вывода со входов D0 - D7,

преобразует ее в последовательный код,

добавляет служебную информацию

(старт-биты, стоп-биты, синхросимволы,

биты четности) в зависимости от

запрограммированного режима работы и

выдает их на выход передатчика TXD.

Синхронизация выходных данных

осуществляется сигналом, подаваемым

на вход

![]() «Синхронизация передатчика». Сигнал

TXRDY «Готовность передатчика»

информирует МП о готовности микросхемы

КР580ВВ51А принять новые данные или команды

управления. Буфер ввода/вывода

содержит восемь двунаправленных

формирователей, имеющих на выходе

состояние «Выключено», и обеспечивает

связь микросхемы КР580ВВ51А с шиной данных

микропроцессора. Назначение выводов

КР580ВВ51А приведено а табл. 1.7.

«Синхронизация передатчика». Сигнал

TXRDY «Готовность передатчика»

информирует МП о готовности микросхемы

КР580ВВ51А принять новые данные или команды

управления. Буфер ввода/вывода

содержит восемь двунаправленных

формирователей, имеющих на выходе

состояние «Выключено», и обеспечивает

связь микросхемы КР580ВВ51А с шиной данных

микропроцессора. Назначение выводов

КР580ВВ51А приведено а табл. 1.7.

Таблица 1.7

Номер вывода |

Обозначение |

Назначение |

27, 28, 1, 2, 5 - 8 |

D0 - D7 |

Шина данных |

3 |

RXD |

Вход приемника |

4 |

GND |

Общий |

9 |

|

Синхронизация передатчика |

10 |

|

Запись |

11 |

|

Выбор микросхемы |

12 |

|

Управление/данные |

13 |

|

Чтение |

14 |

RXRDY |

Готовность приемника |

15 |

TXRDY |

Готовность передатчика |

16 |

SYNDET |

Вид синхронизации |

17 |

|

Готовность приемника терминала |

18 |

ТХЕ |

Конец передачи |

19 |

TXD |

Выход передатчика |

20 |

CLK |

Тактовый сигнал |

21 |

RESET |

Установка |

22 |

|

Готовность передатчика терминала |

23 |

|

Запрос приемника терминала |

24 |

|

Запрос передатчика терминала |

25 |

|

Синхронизация приемника |

26 |

Ucc |

+ 5В |

Синхронный режим характеризуется непрерывным потоком передаваемой/принимаемой информации. Для установления синхронизации между передатчиком/приемником микросхемы КР580ВВ51А и приемником/передатчиком внешнего устройства и выделения из последовательного потока символов полезной информации в поток информации вводятся кодирующие слова (синхросимволы). Информационная (5 - 8 бит) и временная длины синхросимвола и слова данных равны.

Если между словами данных имеются временные промежутки, то они заполняются синхросимволами. Синхросимволов может быть один или два (устанавливается программно). Если запрограммирован контроль данных по четности (нечетности), то после каждого слова данных вставляется бит контроля.

Сигналы

на внешних входах микросхемы асинхронны

по отношению к сигналу С.

Однако

соотношение частот общей синхронизации

микросхемы (fc)

и частот синхронизации передачи/приема

(![]() ,

,

![]() )

должно быть:

≤fc

/30;

≤fc

/30. При

этом обеспечивается скорость

передачи/приема информации v

= Тх (Rx) = 0÷64

К бод. Скорость численно равна частоте

синхронизации передачи/приема и

определяется в указанном выше

диапазоне возможностями внешнего

устройства.

)

должно быть:

≤fc

/30;

≤fc

/30. При

этом обеспечивается скорость

передачи/приема информации v

= Тх (Rx) = 0÷64

К бод. Скорость численно равна частоте

синхронизации передачи/приема и

определяется в указанном выше

диапазоне возможностями внешнего

устройства.