- •Содержание

- •1 Микропроцессорный комплект кр580

- •1.1 Мп вм80а. Структура. Основные режимы функционирования

- •1.2 Функционирование мп

- •1.3 Особые режимы функционирования

- •1.4 Непрограммируемые интерфейсные бис

- •1.5 Системный контроллер вк28 Системные контроллеры кр580вк28 и кр580вк38

- •1.6 Интерфейс и классификация интерфейсов

- •1.7 Параллельный адаптер вв55

- •1.8 Последовательный адаптер вв51а Синхронный режим

- •Асинхронный режим

- •1.9 Кпдп вт57. Назначение. Структура

- •Функционирование

- •1.10 Кпп вн59. Назначение. Структура

- •1.11 Контроллер клавиатуры и индикации вв 79

- •1.12 Контроллер видеотерминала кр580вг75

- •1.13 Особенности мп к1821вм8085а

- •2 Микрокрнтроллер мк51

- •2.1. Структурная схема мк51

- •2.1.1. Арифметическо-логическое устройство

- •2.1.2. Резидентная память

- •2.1.3. Устройство управления и синхронизации

- •2.2. Порты ввода/вывода информации

- •Доступ к внешней памяти

- •2.3. Таймер/счетчик

- •2.4. Последовательный интерфейс

- •2.5. Система прерываний

1.6 Интерфейс и классификация интерфейсов

Интерфейсы предназначены для организации взаимодействия между микросхемами, организующими функциональные модули при построении вычислительной системы. Интерфейсы регламентируют правило взаимодействия между всеми функциональными модулями микропроцессорной системы, устанавливают взаимодействие и определяют протоколы и порядок обмена информацией.

Конфигурации интерфейсов разработаны исходя из следующих требований:

получение нужного быстродействия и организации стандартного обмена информацией между блоками вычислительной системы независимо от их быстродействия;

простота наращивания структуры многопроцессорного комплекса и возможность доступа для диагностики;

широкая область применения.

Электрические соединения между выводами микросхем выполняются электрическими связями или линиями. Эти линии сгруппированы по определенному функциональному назначению образуют шину адреса, шину данных и шину управления. Совокупность шин образует магистраль. В зависимости от функционального назначения интерфейсы классифицируются по следующим принципам:

по способу создания функциональных модулей;

по способу передачи данных - параллельный, последовательный и последовательно-параллельный ;

по режиму передачи данных - односторонние, 2-х сторонние, одновременная или поочередная передача (дуплекс или полудуплекс).

по принципу обмена информацией - синхронный и асинхронный.

1.7 Параллельный адаптер вв55

Любое устройство должно быть тем или иным образом связано с внешним миром. В микропроцессорной технике эту роль выполняют периферийные адаптеры. С их помощью центральный процессор получает данные, требующие той или иной обработки, управляет различными устройствами.

Программируемый периферийный адаптер (ППА) КР580ВВ55 представляет собой три канала ввода/вывода A, B и C по 8 бит каждый. Существует три режима работы микросхемы. В режиме 0 три упомянутых канала могут быть независимо друг от друга запрограммированы на ввод или вывод информации. Режим 1 позволяет передавать информацию по каналам A и B, используя отдельные биты канала C для управления обменом данными. В режиме 2 канал A приобретает свойство двунаправленной шины, управляемой опять же отдельными битами канала C. Кроме того, возможны установка и сброс отдельных битов канала C. Микросхема выпускается в 40-выводном DIP-корпусе.

Основные особенности микросхемы:

3 канала ввода/вывода, 8 бит каждый;

3 режима работы (1 - статический ввод/вывод, 2 - тактируемый ввод/вывод, 3 - двунаправленный ввод/вывод);

раздельное программирование каждого канала на ввод или вывод.

Структурная схема программируемого периферийного адаптера представлена на рис. 1.14.

Рисунок 1.14 - Структурная схема программируемого периферийного адаптера КР580ВВ55

ППА структурно разбит на две группы (A и B). Группа A включает в себя канал A и старшую тетраду канала C. Группа B состоит из канала B и младшей тетрады канала C. Доступ к каналам ввода/вывода и регистру управления осуществляется с помощью логики чтения-записи в соответствии с табл. 1.4.

Таблица 1.4 - Доступ к каналам ввода/вывода и регистру управляющего слова

A1 |

A0 |

|

|

|

|

0 |

0 |

0 |

1 |

0 |

Шина данных <- канал A |

0 |

1 |

0 |

1 |

0 |

Шина данных <- канал B |

1 |

0 |

0 |

1 |

0 |

Шина данных <- канал C |

1 |

1 |

0 |

1 |

0 |

Данные не определены |

0 |

0 |

1 |

0 |

0 |

Шина данных -> канал A |

0 |

1 |

1 |

0 |

0 |

Шина данных -> канал B |

1 |

0 |

1 |

0 |

0 |

Шина данных -> канал C |

1 |

1 |

1 |

0 |

0 |

Шина данных -> регистр управления |

X |

Х |

Х |

Х |

1 |

Шина данных в высокоомном состоянии |

Назначение этих и остальных выводов микросхемы приведено в табл. 1.5.

Таблица 1.5 - Назначение выводов

D0…D7 |

Двунаправленная шина данных. Предназначена для передачи и приема данных процессором, а также передачи управляющих команд и слова состояния |

|

Chip Select. Выбор микросхемы. Низкий уровень инициирует обмен между процессором и ППА |

|

Read. Чтение. Низкий уровень на этом входе позволяет ППА передать данные или слово состояния процессору |

|

Write. Запись. Низкий уровень на этом входе позволяет ППА принять данные или управляющую команду |

RESET |

Reset. Сброс. Высокий уровень на этом входе сбрасывает все внутренние регистры, включая регистры управления, переключает все каналы (A, B, C) в режим 0, одновременно переводя их в режим ввода (только при = 0 и = 0) |

A0, A1 |

Адресные входы. Выбор канала. Позволяют выбрать один из каналов (A, B, C) или регистры управляющего слова и состояния (в зависимости от сигналов на входах и ) |

PA0…PA7 |

Канал A |

PB0…PB7 |

Канал B |

PC0…PC7 |

Канал C |

Первоначальное включение или подача сигнала высокого уровня на вход сброс RESET микросхемы переключает все каналы (A, B, C) в режим 0, одновременно переводя их в режим ввода. Сброс выполняется только при условии = 0 и = 0.

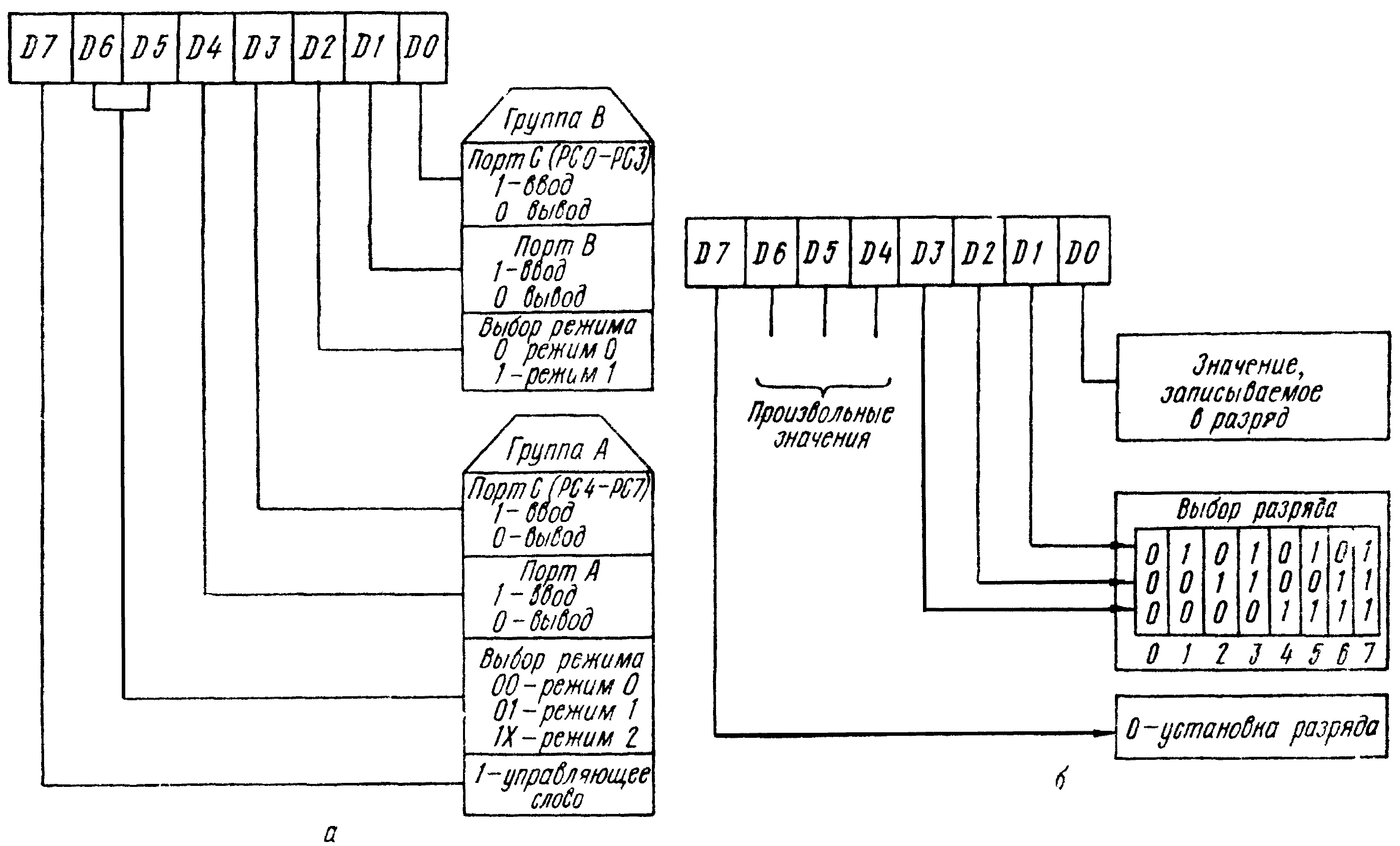

Задание режима и направление пересылки определяется управляющим словом. Структура управляющего слова изображена на рис. 1.14а.

Рисунок 1.14а - Структура управляющего слова

В зависимости от информации в старшем разряде управляющие слова могут использоваться для следующих целей: настройки ППА на допустимый режим (D7 = 1) (рис. 1.14а,а) или установки разрядов порта С (D7 = 0) (рис. 1.14а,б). Любой из восьми битов порта С может быть сброшен в «0 или установлен в «1» по команде OUT. При этом из аккумулятора микропроцессора в регистр управляющего слова пересылается в управляющее слово с признаком D7 = 0. Определенные триггеры порта могут быть использованы разработчиком системы в качестве триггера запроса на прерывание INT или триггера разрешения на прерывание INTE. Программный доступ к ним дает возможность разрешать или запрещать обслуживание запросов на прерывание, поступающих от внешних устройств.