- •Содержание

- •1 Микропроцессорный комплект кр580

- •1.1 Мп вм80а. Структура. Основные режимы функционирования

- •1.2 Функционирование мп

- •1.3 Особые режимы функционирования

- •1.4 Непрограммируемые интерфейсные бис

- •1.5 Системный контроллер вк28 Системные контроллеры кр580вк28 и кр580вк38

- •1.6 Интерфейс и классификация интерфейсов

- •1.7 Параллельный адаптер вв55

- •1.8 Последовательный адаптер вв51а Синхронный режим

- •Асинхронный режим

- •1.9 Кпдп вт57. Назначение. Структура

- •Функционирование

- •1.10 Кпп вн59. Назначение. Структура

- •1.11 Контроллер клавиатуры и индикации вв 79

- •1.12 Контроллер видеотерминала кр580вг75

- •1.13 Особенности мп к1821вм8085а

- •2 Микрокрнтроллер мк51

- •2.1. Структурная схема мк51

- •2.1.1. Арифметическо-логическое устройство

- •2.1.2. Резидентная память

- •2.1.3. Устройство управления и синхронизации

- •2.2. Порты ввода/вывода информации

- •Доступ к внешней памяти

- •2.3. Таймер/счетчик

- •2.4. Последовательный интерфейс

- •2.5. Система прерываний

1.5 Системный контроллер вк28 Системные контроллеры кр580вк28 и кр580вк38

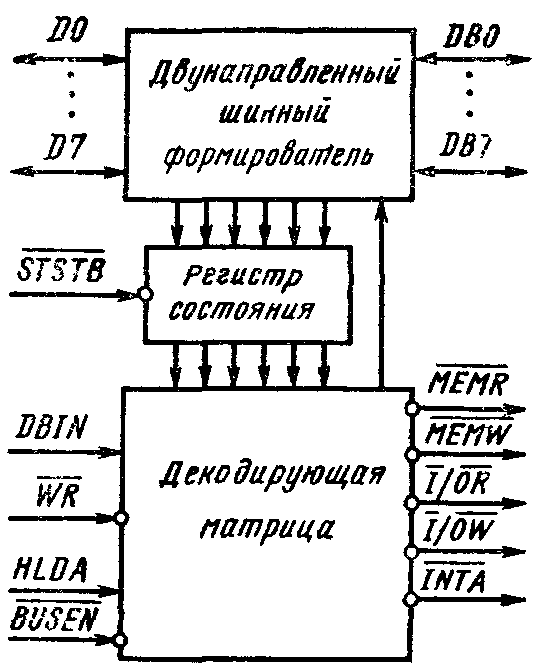

Микросхемы КР580ВК28 и КР580ВК38 выполняют функции системного контроллера и шинного формирователя, осуществляют формирование управляющих сигналов обращения к ОЗУ или к устройствам ввода/вывода (УВВ) и обеспечивают прием и передачу 8-разрядной информации между шиной данных микропроцессора и системной шиной.

Отличие

микросхемы КР580ВК28 от микросхемы

КР580ВК38 состоит в формировании сигналов

![]() ,

,

![]() .

Микросхема КР580ВК28 формирует эти сигналы

относительно сигнала

.

Микросхема КР580ВК28 формирует эти сигналы

относительно сигнала

![]() «Запись», а микросхема КР580ВК38 -

относительно сигнала

«Запись», а микросхема КР580ВК38 -

относительно сигнала

![]() «Строб состояния», что позволяет при

применении в микропроцессорной

системе микросхемы КР580ВК38 использовать

ЗУ и УВВ с более широким диапазоном

быстродействия. Структурная схема

КР580ВК28 и КР580ВК38 представлена на рис.

1.13. Двунаправленный шинный формирователь

осуществляет буферирование 8-разряд

ной шины данных и автоматический контроль

направления передачи данных. Подключение

системного контроллера к шине данных

микропроцессора осуществляется с

помощью двунаправленных выводов D0 - D7,

к системной шине - с помощью двунаправленных

выводов DB0 - DB7. При необходимости с

помощью сигнала

«Строб состояния», что позволяет при

применении в микропроцессорной

системе микросхемы КР580ВК38 использовать

ЗУ и УВВ с более широким диапазоном

быстродействия. Структурная схема

КР580ВК28 и КР580ВК38 представлена на рис.

1.13. Двунаправленный шинный формирователь

осуществляет буферирование 8-разряд

ной шины данных и автоматический контроль

направления передачи данных. Подключение

системного контроллера к шине данных

микропроцессора осуществляется с

помощью двунаправленных выводов D0 - D7,

к системной шине - с помощью двунаправленных

выводов DB0 - DB7. При необходимости с

помощью сигнала

![]() «Управление системной шиной» выводы

DB0 - DB7 системного контроллера могут быть

переведены в состояние «Выключено».

«Управление системной шиной» выводы

DB0 - DB7 системного контроллера могут быть

переведены в состояние «Выключено».

Риcунок 1.13 - Структурная схема КР580ВК28 и КР580ВК38

Таблица 1.3

Номер вывода |

Обозначение |

Назначение |

6, 8, 10, 12, 15 17, 19, 21 |

D0-D7 |

Шина данных |

5, 7, 9, 11, 13, 16, 18, 20 |

DB0-DB7 |

Системная шина |

1 |

|

Строб состояния |

2 |

HLDA |

Подтверждение захвата |

3 |

|

Запись |

4 |

DBIN |

Прием |

11 |

GND |

Общий |

22 |

|

Управление системной шиной |

23 |

|

Подтверждение прерывания |

24 |

MFMR |

Чтение памяти |

25 |

I/OR |

Чтение УВВ |

26 |

|

Запись в память |

27 |

|

Запись в УВВ |

28 |

Ucc |

+5 В |

Регистр состояния выполнен на шести D-триггерах и предназначен для хранения информации о состоянии микропроцессора, поступающей по шине данных D0 - D7 Запись в регистр состояния осуществляется по сигналу , поступающему в начале каждого машинного цикла.

Декодирующая матрица в зависимости от режима работы микропроцессора, зафиксированного в регистре состояния, и входных управляющих сигналов HLDA, , DBIN формирует сигнал «Подтверждение прерывания» или сигналы чтения/записи при обращении к ОЗУ или УВВ. Назначение выводов микросхем КР580ВК28 и КР580ВК38 приведено в табл. 1.3.