- •Содержание

- •1 Микропроцессорный комплект кр580

- •1.1 Мп вм80а. Структура. Основные режимы функционирования

- •1.2 Функционирование мп

- •1.3 Особые режимы функционирования

- •1.4 Непрограммируемые интерфейсные бис

- •1.5 Системный контроллер вк28 Системные контроллеры кр580вк28 и кр580вк38

- •1.6 Интерфейс и классификация интерфейсов

- •1.7 Параллельный адаптер вв55

- •1.8 Последовательный адаптер вв51а Синхронный режим

- •Асинхронный режим

- •1.9 Кпдп вт57. Назначение. Структура

- •Функционирование

- •1.10 Кпп вн59. Назначение. Структура

- •1.11 Контроллер клавиатуры и индикации вв 79

- •1.12 Контроллер видеотерминала кр580вг75

- •1.13 Особенности мп к1821вм8085а

- •2 Микрокрнтроллер мк51

- •2.1. Структурная схема мк51

- •2.1.1. Арифметическо-логическое устройство

- •2.1.2. Резидентная память

- •2.1.3. Устройство управления и синхронизации

- •2.2. Порты ввода/вывода информации

- •Доступ к внешней памяти

- •2.3. Таймер/счетчик

- •2.4. Последовательный интерфейс

- •2.5. Система прерываний

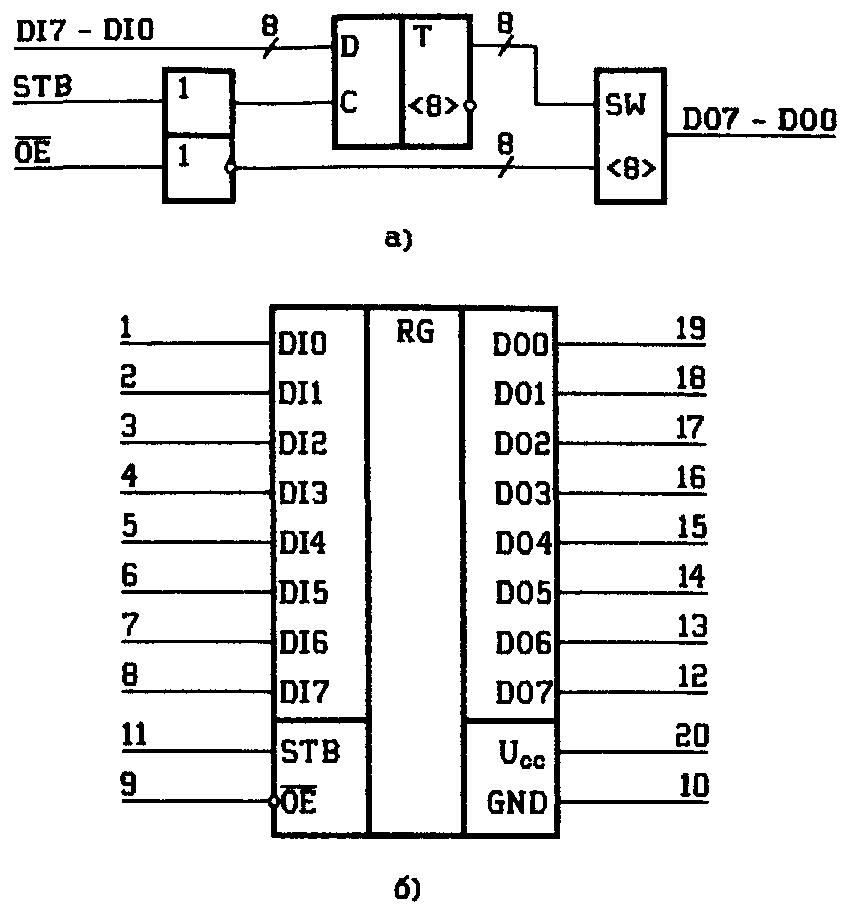

1.4 Непрограммируемые интерфейсные бис

Восьмиразрядные

буферные регистры (БР) КР580ИР82, КР580ИР83

используются для организации

запоминающих буферов, адресных защелок,

портов ввода - вывода, мультиплексоров

и т. п. Буферные регистры состоят из

восьми информационных триггеров (Т) с

выходными схемами (SW) с тремя состояниями,

общими сигналами записи информации STB

и управления выходными схемами

![]() .

В буферном регистре ИР82 (рис. 1.7) к выходным

схемам подключены прямые выходы

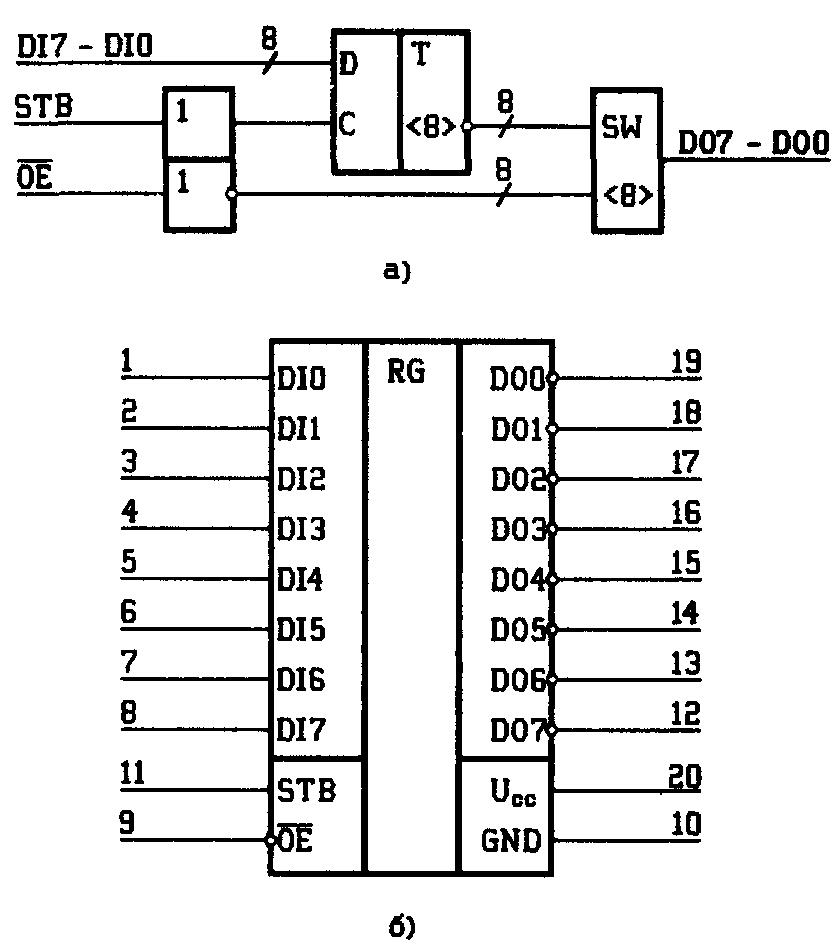

информационных триггеров, в БР ИР83 (рис.

1.8) - инверсные.

.

В буферном регистре ИР82 (рис. 1.7) к выходным

схемам подключены прямые выходы

информационных триггеров, в БР ИР83 (рис.

1.8) - инверсные.

Назначение выводов DI7 - DI0 - линии входных данных; D07 - D00 - линии выходных данных; STB - стробирующий сигнал; - разрешение выдачи данных.

При сигнале высокого уровня на входе STB состояние входных линий DI7 - DI0 передается на выходные линии D07 - D00. Запоминание (защелкивание) в информационных триггерах осуществляется при переходе сигнала STB от высокого уровня к низкому (по срезу сигнала STB). Сигнал управляет выходными буферами: при = 0 буфер отпирается, при = 1 он устанавливается в Z-состояние. Сигнал не влияет ни на состояния информационных триггеров, ни на функцию записи.

Рисунок 1.7 - Функциональная схема БР ИР82 (а) и его условное графическое обозначение (б)

Рисунок 1.8 - Функциональная схема БР ИР83 (а) и его условное графическое обозначение (б)

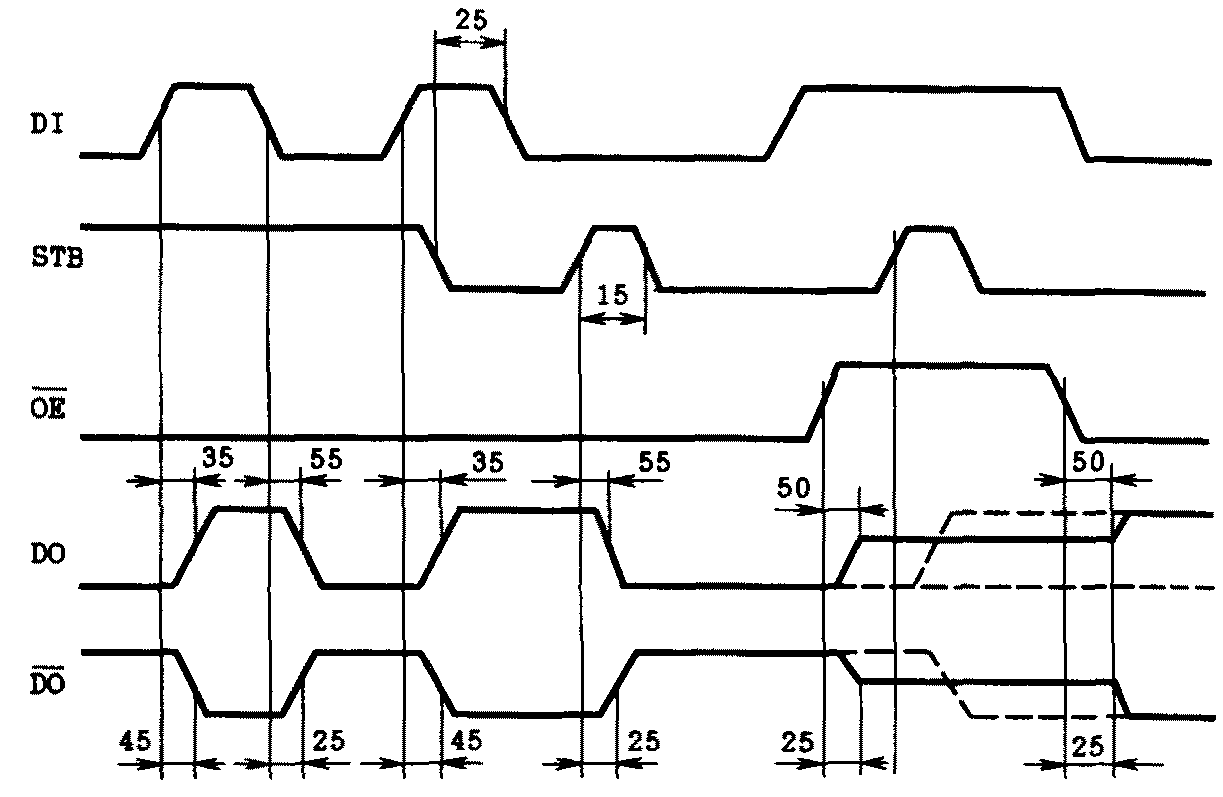

Малый входной ток и достаточно большой выходной позволяют использовать эти элементы в качестве развязывающих буферов-защелок либо шинных формирователей. В качестве шинных формирователей БР используют, подключая STB через резистор сопротивлением 1 кОм к шине питания ( + 5 В), а вход - к общей шине, что делает БР «прозрачным». Временная диаграмма работы БР ИР82/83 приведена на рис. 1.9

Рисунок 1.9 - Временные диаграммы работы БР ИР82/83

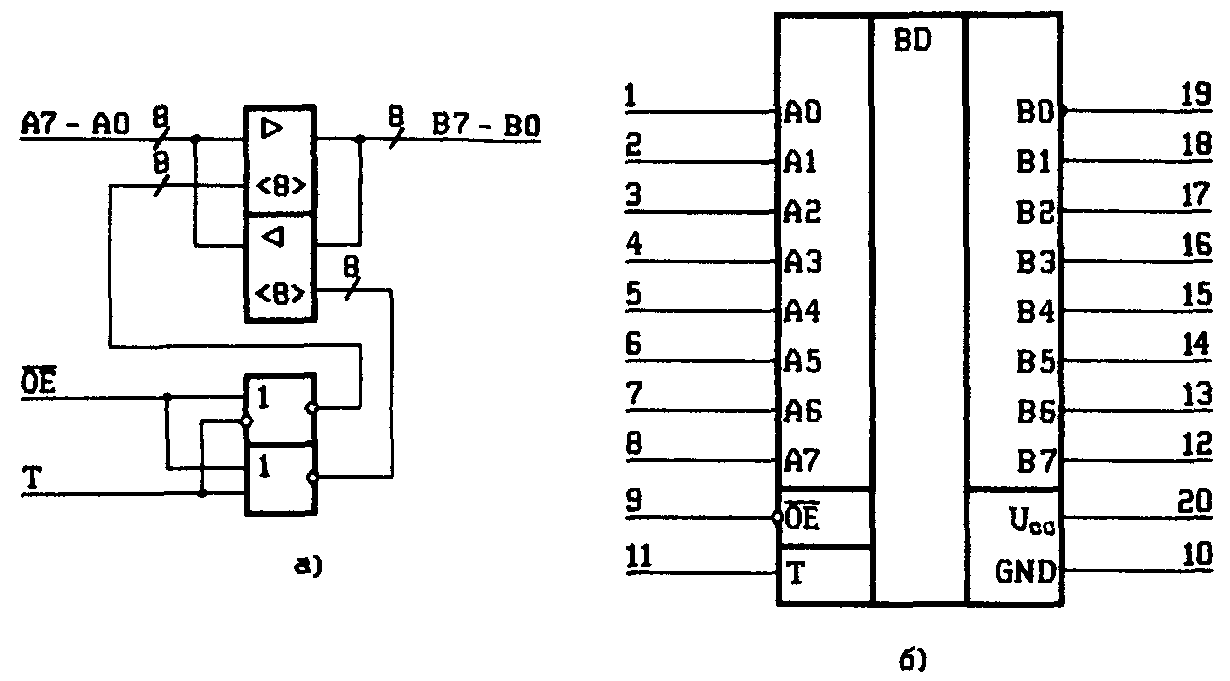

Восьмиразрядные шинные формирователи (ШФ) КР580ВА86, КР580ВА87 применяют как буферные устройства шины данных в микропроцессорных системах. Большая выходная мощность и простота управления позволяют использовать их для построения двунаправленных согласующих буферов межмодульной связи либо как простые усилительные каскады. Полная конструктивная совместимость с БР ИР82/83 допускает взаимозаменяемость при однонаправленной передаче.

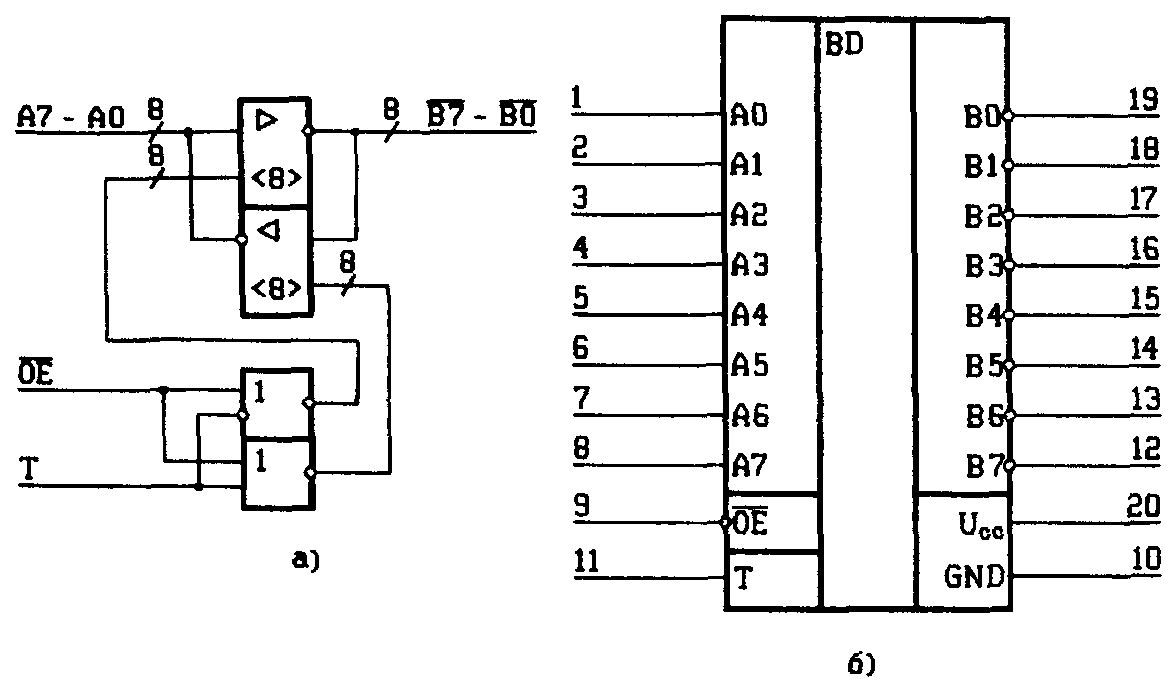

Формирователь состоит из восьми одинаковых функциональных блоков с общими сигналами управления Т и . Функциональные блоки состоят из двух усилителей-формирователей с z-состояниями на выходах, схема включения которых обеспечивает разнонаправленную передачу. Формирователь ВА86 (рис. 1.10) не инвертирует данные, а ВА87 (рис. 1.11) инвертирует.

Назначение выводов ШФ:

А7 - А0 - вход/выход линий данных. В зависимости от состояния входа Т они могут быть входными, если на Т - сигнал высокого уровня, и выходными, если на Т - сигнал низкого уровня.

В7 - В0 - вход/выход линий данных. Они являются входными, если на Т - сигнал низкого уровня, и выходными, если на Т - сигнал высокого уровня.

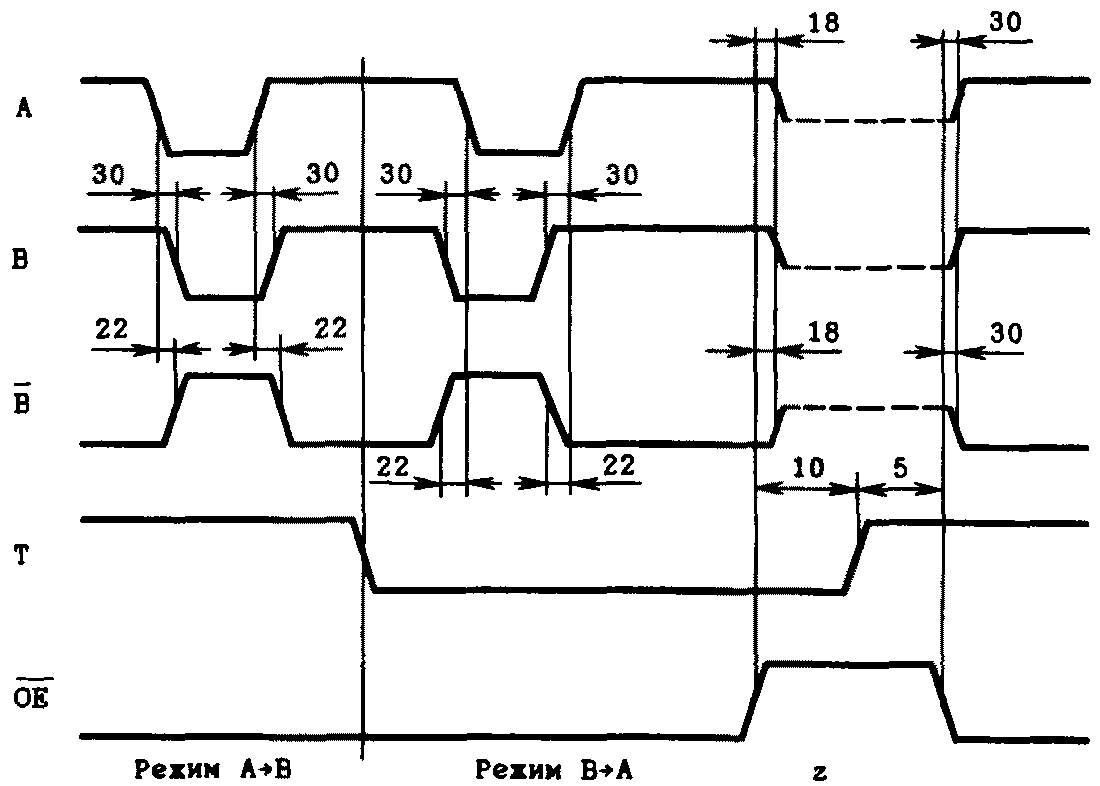

Т - входной сигнал управления направлением передачи. При Т = 0 осуществляется передача от В к А (режим В→А), при Т = 1 - от А к В. Сигнал Т выбирает верхний или нижний усилитель-формирователь, разрешая соответствующую передачу.

- входной сигнал разрешения передачи. При = 0 снимается z-состояние с выхода усилителя-формирователя, выбранного по входу. Т. Переход в z-состояние и наоборот не дает отрицательных выбросов на выходах ИС.

Рисунок 1.10 - Функциональная схема ШФ ВА86 (а) и его условное графическое обозначение (б)

Рисунок 1.11 - Функциональная схема ШФ ВА87 (а) и его условное графическое обозначение (6)

Рисунок 1.12 - Временные диаграммы работы ШФ ВА86/87

Основные достоинства ШФ: большой выходной ток при малом входном токе и отсутствие шума на выходе при переключениях. Временная диаграмма работы ШФ приведена на рис. 1.12.