- •Содержание

- •1 Микропроцессорный комплект кр580

- •1.1 Мп вм80а. Структура. Основные режимы функционирования

- •1.2 Функционирование мп

- •1.3 Особые режимы функционирования

- •1.4 Непрограммируемые интерфейсные бис

- •1.5 Системный контроллер вк28 Системные контроллеры кр580вк28 и кр580вк38

- •1.6 Интерфейс и классификация интерфейсов

- •1.7 Параллельный адаптер вв55

- •1.8 Последовательный адаптер вв51а Синхронный режим

- •Асинхронный режим

- •1.9 Кпдп вт57. Назначение. Структура

- •Функционирование

- •1.10 Кпп вн59. Назначение. Структура

- •1.11 Контроллер клавиатуры и индикации вв 79

- •1.12 Контроллер видеотерминала кр580вг75

- •1.13 Особенности мп к1821вм8085а

- •2 Микрокрнтроллер мк51

- •2.1. Структурная схема мк51

- •2.1.1. Арифметическо-логическое устройство

- •2.1.2. Резидентная память

- •2.1.3. Устройство управления и синхронизации

- •2.2. Порты ввода/вывода информации

- •Доступ к внешней памяти

- •2.3. Таймер/счетчик

- •2.4. Последовательный интерфейс

- •2.5. Система прерываний

1.3 Особые режимы функционирования

Если

в такте

![]() любого из циклов микропроцессора (за

исключением

,

,

)

на вход READY подается сигнал низкого

уровня, микропроцессор переходит в

состояние «ожидание». Если на вход HOLD

подается сигнал высокого уровня,

микропроцессор переходит в состояние

«захват». Если проверяемый в такте

внутренний триггер (HLTA) микропроцессора

установлен в «1» в результате выполнения

команды HLT, микропроцессор переходит в

состояние останова, наступаемое

после прохождения цикла

.

Если на входе INT, который проверяется в

последнем цикле выполняемой команды,

- сигнал высокого уровня (запрос на

прерывания от внешнего устройства)

микропроцессор переходит к обслуживанию

подпрограмм обработки прерываний,

наступаемому после прохождения цикла

или

.

любого из циклов микропроцессора (за

исключением

,

,

)

на вход READY подается сигнал низкого

уровня, микропроцессор переходит в

состояние «ожидание». Если на вход HOLD

подается сигнал высокого уровня,

микропроцессор переходит в состояние

«захват». Если проверяемый в такте

внутренний триггер (HLTA) микропроцессора

установлен в «1» в результате выполнения

команды HLT, микропроцессор переходит в

состояние останова, наступаемое

после прохождения цикла

.

Если на входе INT, который проверяется в

последнем цикле выполняемой команды,

- сигнал высокого уровня (запрос на

прерывания от внешнего устройства)

микропроцессор переходит к обслуживанию

подпрограмм обработки прерываний,

наступаемому после прохождения цикла

или

.

Следует подчеркнуть, что переход в состояние «ожидание» происходит в машинном цикле между состояниями и . Переход в состояние «захват» должен выполняться в промежутках между машинными циклами. Переход к обслуживанию прерывания происходит по окончанию выполнения текущей команды, т. е. между командами.

Состояние

«ожидание»

предназначено для согласования работы

микропроцессора с медленно действующими

памятью или внешними устройствами,

которые не успевают выставить данные

на входы микропроцессора D0 - D7 во

время действия сигнала DBIN в циклах

чтения или принять их во время действия

сигнала

в циклах записи. При этом внешний модуль

участвует в формировании сигнала

высокого уровня на входе READY микропроцессора,

который после такта

переходит в состояние ожидания

![]() (рис. 1.4). По каждому F2 в этом состоянии

происходит опрос сигнала на входе READY.

Если на нем появляется сигнал высокого

уровня, то по переднему фронту F1

микропроцессор выходит из состояния

ожидания и переходит в такт

во время которого он по сигналу DBIN

принимает данные от внешнего модуля.

Следует отметить, что в состоянии

ожидания микропроцессор на выходе

WAIT выставляет сигнал высокого уровня,

а на остальных выходах сигналы не

изменяются. Если микропроцессор

перешел в состояние ожидания во время

выполнения цикла записи (чтения), то

сигнал низкого (высокого) уровня на

выходе

(DBIN) поддерживается в этом состоянии.

(рис. 1.4). По каждому F2 в этом состоянии

происходит опрос сигнала на входе READY.

Если на нем появляется сигнал высокого

уровня, то по переднему фронту F1

микропроцессор выходит из состояния

ожидания и переходит в такт

во время которого он по сигналу DBIN

принимает данные от внешнего модуля.

Следует отметить, что в состоянии

ожидания микропроцессор на выходе

WAIT выставляет сигнал высокого уровня,

а на остальных выходах сигналы не

изменяются. Если микропроцессор

перешел в состояние ожидания во время

выполнения цикла записи (чтения), то

сигнал низкого (высокого) уровня на

выходе

(DBIN) поддерживается в этом состоянии.

Состояние «захват». По сигналу высокого уровня, поступающего от внешних устройств или пульта оператора на вход HOLD, микропроцессор переходит в состояние «захват». Состояние «захват» предназначено для того, чтобы внешнее устройство могло считывать или записывать информацию непосредственно в память системы, минуя микропроцессор, благодаря чему существенно повышается скорость обмена, который происходит по инициативе внешнего устройства. Такой обмен называется контроллерным. Контроллер, управляющий обменом информации между внешним устройством и памятью системы, реализует режим прямого доступа. Состояние «захват» похоже на состояние «ожидание». Сигналы на выводах микропроцессора также не изменяются, однако выводы шин данных и адреса микропроцессора в состоянии «захват» переходят в высокоимпедансное состояние, предоставляя их внешнему устройству для обмена.

Рисунок 1.4 - Диаграмма состояния «ожидания»

Переход микропроцессора в состояние «захват» осуществляется по-разному в зависимости от типа машинного цикла.

Если запрос на захват появился во время выполнения операции ввода или чтения, то по переднему фронту F1 в третьем такте на выходе HLDA появляется высокий уровень, подтверждающий состояние «захват». Выводы D0 - D7 микропроцессора в третьем такте переходят в высокоимпедансное состояние, а выводы А0 - А15 - в такте, следующем за третьим. Если выполнялся цикл извлечения команды, который состоит из четырех или пяти тактов, то микропроцессор завершает выполнение этого цикла с «отключенными» выводами D0 - D7, А0 - А15

Если выполнялась операция записи или вывода, сигнал на выходе HLDA появляется в такте, следующем за третьим. Это дает возможность микропроцессору завершить процесс записи данных перед переходом в состояние «захват». Выводы D0 - D7 и А0 - А15 также переходят в высокоимпедансное состояние в такте, следующем за третьим. При появлении низкого потенциала на входе HOLD микропроцессор по переднему фронту F1 выходит из состояния «захват» и переходит к первому такту следующего цикла.

Состояние «останов» похоже на состояние «ожидание», только оно происходит в результате выполнения команды HLT, т. е. переход в это состояние происходит программно. Из состояния «останов» можно перейти в состояние «захват» и обратно. Микропроцессор может также обслужить запрос на прерывание от внешнего устройства, однако выйти из состояния «останов», можно, только осуществив начальную установку путем отключения и включения питания или подачей сигнала с пульта управления (рис. 1.5).

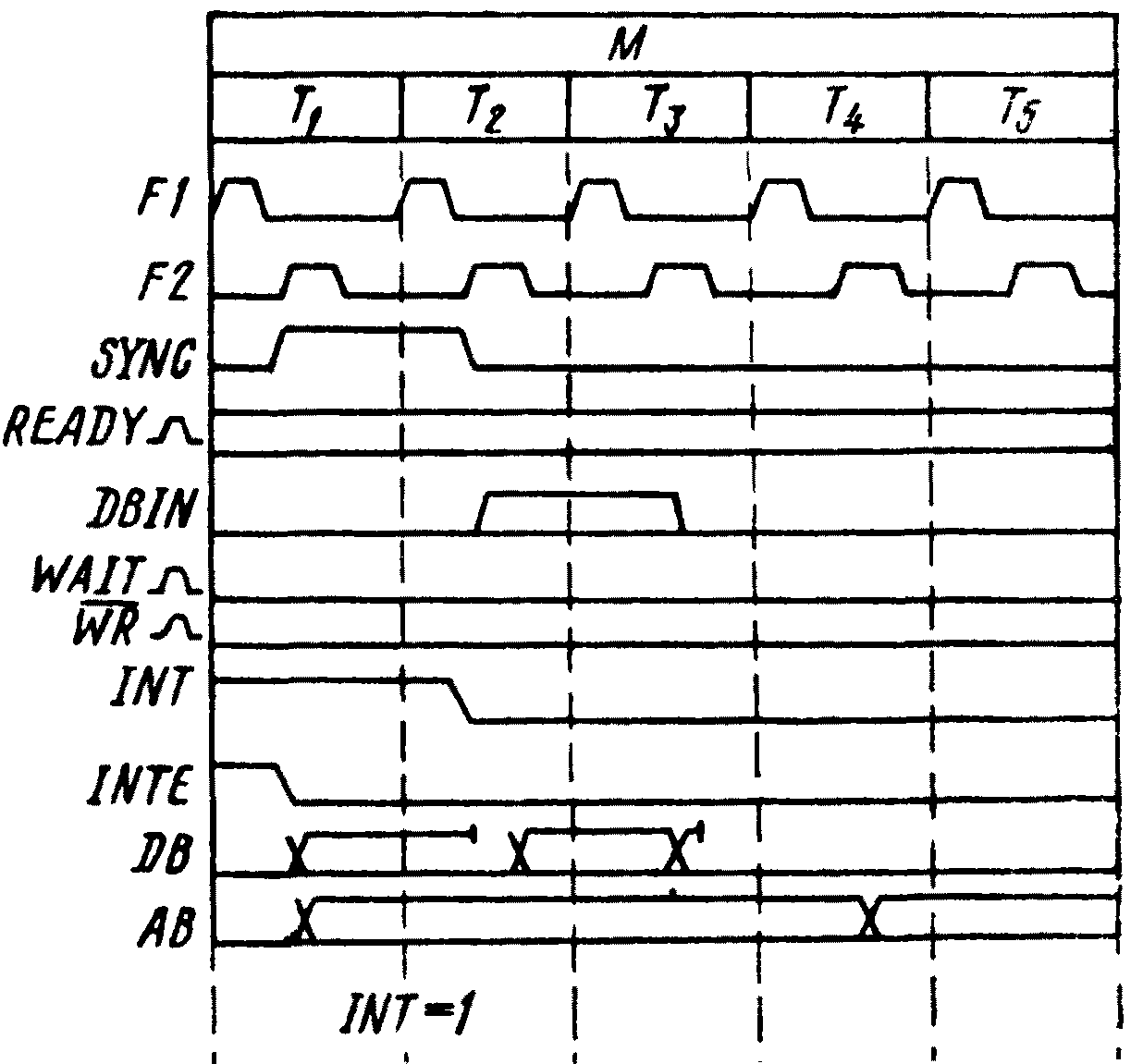

Прерывания. Режим прерывания может наступить при подаче на вход INT сигнала высокого уровня. Как уже отмечалось, сигнал на этом входе проверяется в последнем цикле выполнения команды по F2. Однако запрос на прерывание может быть обслужен, если триггер прерывания микропроцессора (выход INTE) установлен в «1». Обычно этот триггер по сигналу RESET сбрасывается в "0" и запрещает прерывание. Разрешить прерывание можно программным путем по команде EI. Микропроцессор сообщает другим модулям о переходе к прерыванию словом состояния с единицами в разрядах D0, D1, D5. После перехода в режим прерывания микропроцессор выполняет команду вызова подпрограммы прерывания, поступающую по шине данных от внешних устройств (рис. 1.6). При этом счетчик команд не увеличивается на единицу, команда вызова подпрограммы должна сохранить его состояние в стеке, а после выполнения прерывания восстановить его содержимое. Для перехода к подпрограммам обработки прерывания могут использоваться команды RST или CALL.

Рисунок 1.5 - Диаграмма состояния «останов»

Рисунок 1.6 - Диаграмма прерываний

Например, при передаче на шину данных объектного кода RST101 (11110111) происходит переход по адресу 0028Н (0000000000101000). Выход из прерывания происходит по команде RET. Из всех особых состояний микропроцессора наиболее приоритетным является состояние «ожидания». Если на вход READY подается сигнал низкого уровня, то микропроцессор несмотря на наличие каких-либо других сигналов, например запроса на захват или прерывание, перейдет в состояние ожидания. Когда на вход READY подан сигнал высокого уровня, в случае если подан запрос на прерывание, запрос на захват не будет обслужен. В режиме обслуживания запроса на прерывание невозможен переход в состояние «захват» и наоборот. В состоянии «захват» запрос на прерывание обслуживаться не будет. Запросы на прерывание и захват могут быть, обслужены в состоянии «останов». В этом состоянии запрос на захват не будет удовлетворяться, если подан запрос на прерывание. После получения подтверждения прерывания микропроцессор может перейти в состояние «захват».