- •Содержание

- •1 Микропроцессорный комплект кр580

- •1.1 Мп вм80а. Структура. Основные режимы функционирования

- •1.2 Функционирование мп

- •1.3 Особые режимы функционирования

- •1.4 Непрограммируемые интерфейсные бис

- •1.5 Системный контроллер вк28 Системные контроллеры кр580вк28 и кр580вк38

- •1.6 Интерфейс и классификация интерфейсов

- •1.7 Параллельный адаптер вв55

- •1.8 Последовательный адаптер вв51а Синхронный режим

- •Асинхронный режим

- •1.9 Кпдп вт57. Назначение. Структура

- •Функционирование

- •1.10 Кпп вн59. Назначение. Структура

- •1.11 Контроллер клавиатуры и индикации вв 79

- •1.12 Контроллер видеотерминала кр580вг75

- •1.13 Особенности мп к1821вм8085а

- •2 Микрокрнтроллер мк51

- •2.1. Структурная схема мк51

- •2.1.1. Арифметическо-логическое устройство

- •2.1.2. Резидентная память

- •2.1.3. Устройство управления и синхронизации

- •2.2. Порты ввода/вывода информации

- •Доступ к внешней памяти

- •2.3. Таймер/счетчик

- •2.4. Последовательный интерфейс

- •2.5. Система прерываний

1.13 Особенности мп к1821вм8085а

На БИС МП 8085А реализуют процессоры с 8-разрядной системной шиной, совместимые с процессорами на БИС КР580.

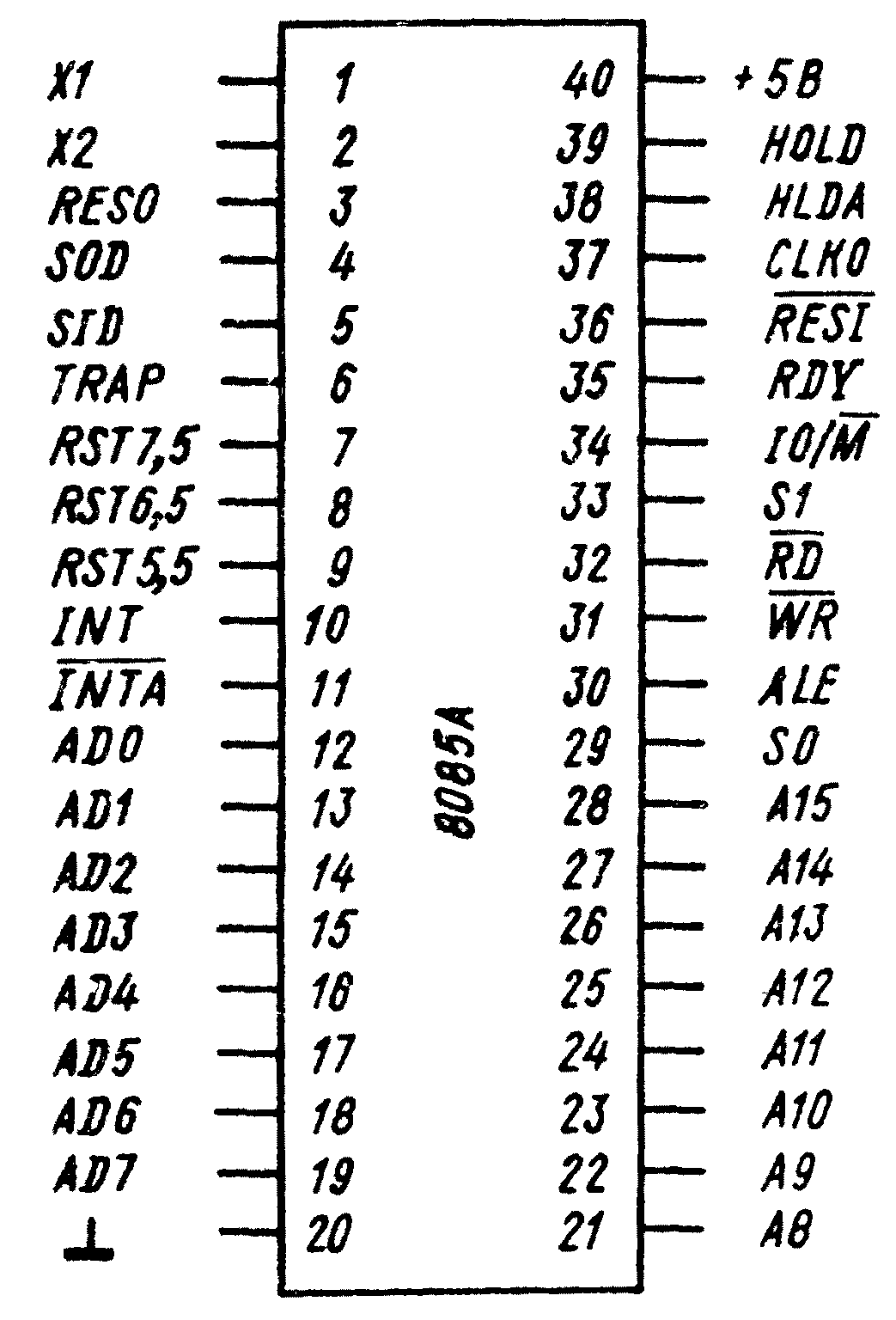

Микропроцессор 8085А (рис. 1.23) полностью программно совместим с микропроцессором КР580ВМ80А, но питается от единого источника +5 В. МП 80С85А выполнен по КМОП-технологии. Микропроцессор обрабатывает те же типы и форматы данных, адресует пространство ЗУ объемом 64К байт, ВУ объемом 256 байт и имеет СОЗУ, аналогичное СОЗУ МП КР580ВМ80А, располагает теми же способами адресации и системой команд, расширенной двумя специальными командами.

Рисунок 1.23 - Расположение выводов БИС микропроцессора 8085А

Структура

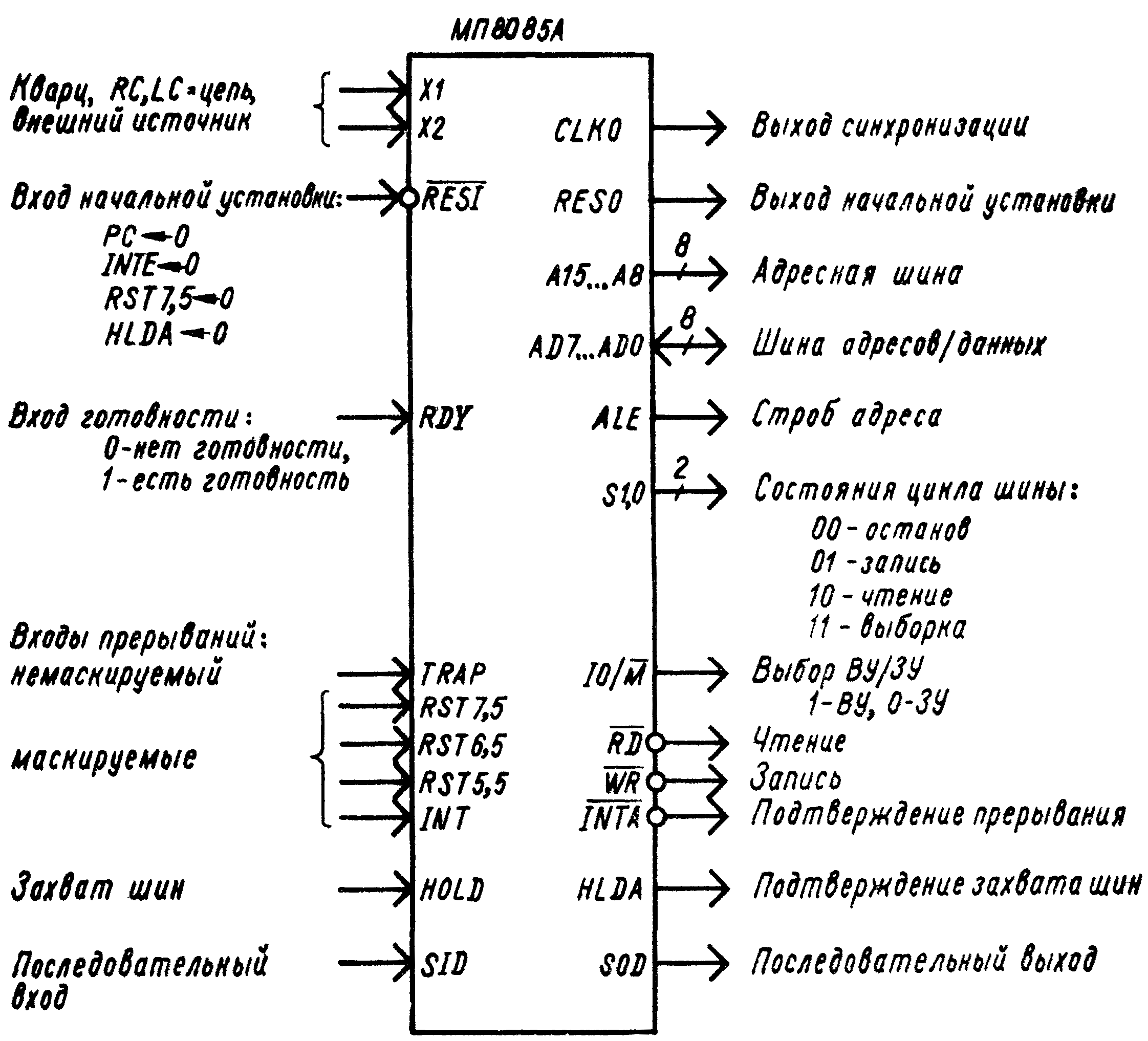

МП 8085А организована аналогично структуре

МП КР580ВМ80А, назначение выводов показано

на рис. 1.24, временные диаграммы - на рис.

1.25. В отличие от МП КР580 ВМ80А МП 8085А имеет

встроенный системный генератор,

выполняющий функции, аналогичные ИС

КР580ГФ24. Он обеспечивает синхронизацию

микропроцессора и временную привязку

сигналов со входов начальной установки

![]() и готовности RDY. Частота генератора

определяется внешним кварцевым

резонатором, RC-цепочкой, LC-контуром или

внешним источником, подключаемыми ко

входам X1, Х2. На выходы CLКО и RESО выдаются

сигналы синхронизации и начальной

установки устройств ввода/вывода,

располагаемых на системной шине.

Внутренний системный контроллер

формирует общие для ЗУ и ВУ сигналы

чтения/записи на трехстабильные выходы

и готовности RDY. Частота генератора

определяется внешним кварцевым

резонатором, RC-цепочкой, LC-контуром или

внешним источником, подключаемыми ко

входам X1, Х2. На выходы CLКО и RESО выдаются

сигналы синхронизации и начальной

установки устройств ввода/вывода,

располагаемых на системной шине.

Внутренний системный контроллер

формирует общие для ЗУ и ВУ сигналы

чтения/записи на трехстабильные выходы

![]() ,

,

а для разделения доступа к ЗУ или ВУ

используется выход IO/

,

,

а для разделения доступа к ЗУ или ВУ

используется выход IO/![]() .

Адресная шина полусовмещенная - на

выводы А15...А8 выставляется адрес ЗУ

А15...А8 или адрес ВУ A7...A0 на весь интервал

обращения к ЗУ/ВУ, а на выводы AD7...AD0 - в

режима разделения времени вначале адрес

ЗУ/ВУ А7...А0, а затем данные. Адрес на шине

AD7...AD0 сопровождается адресным стробом

на выходе ALE, по которому он фиксируется

во внешнем регистре. Состояние процессора

выдается на выходы ST1, ST0, где ST0

определяет цикл записи, a ST1 - цикл чтения.

.

Адресная шина полусовмещенная - на

выводы А15...А8 выставляется адрес ЗУ

А15...А8 или адрес ВУ A7...A0 на весь интервал

обращения к ЗУ/ВУ, а на выводы AD7...AD0 - в

режима разделения времени вначале адрес

ЗУ/ВУ А7...А0, а затем данные. Адрес на шине

AD7...AD0 сопровождается адресным стробом

на выходе ALE, по которому он фиксируется

во внешнем регистре. Состояние процессора

выдается на выходы ST1, ST0, где ST0

определяет цикл записи, a ST1 - цикл чтения.

Рисунок 1.24 - Назначение выводов БИС 8085А

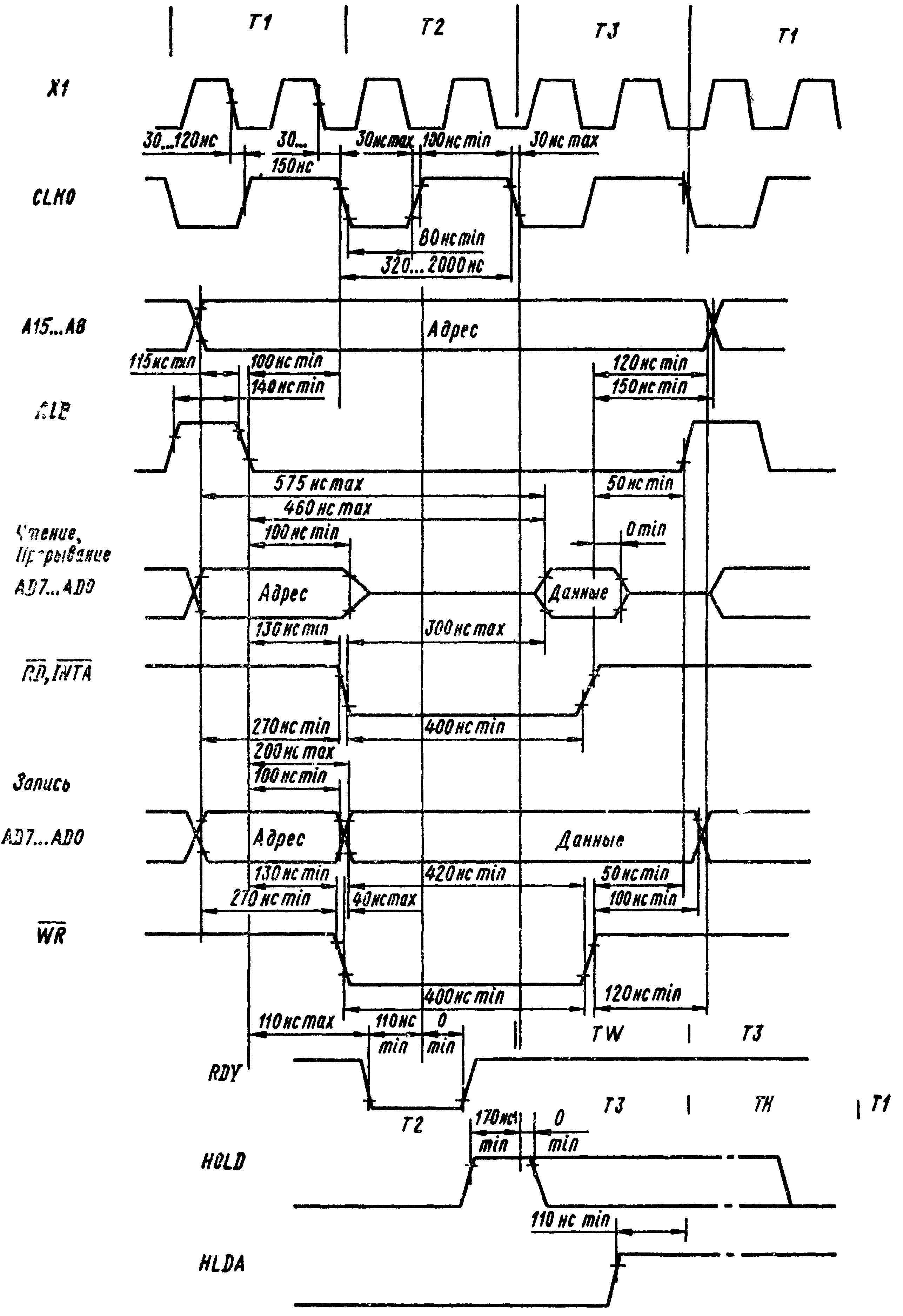

Рисунок 1.25 - Временные диаграммы работы БИС 8085А

Процессор

имеет средства обслуживания прерываний

с пяти входов. Вход INT аналогичен

входу INT МП КР580 и предназначен для

обслуживания маскируемых векторных

прерываний по командам RSTV или CALL ADR

V (с использованием контроллера КР580ВН59).

На выходе

![]() при этом автоматически формируется

один для RST либо три для CALL сигнала

подтверждения прерываний. По командам

RST V осуществляется обращение к памяти

по адресам в зависимости от кода V (0000,

0008, 0010, 0018, 0020, 0028, 0030, 003816). По входам TRAP,

RST 5.5, RST 6.5, RST 7.5 обращение осуществляется

по фиксированным адресам ЗУ 0024, 002С,

0034, 00ЗС соответственно. Входы RST 5.5,

RST 6.5, RST 7.5 являются программно-маскируемыми,

вход TRAP немаскируемый и используется

для обслуживания аварийных ситуаций,

таких как сбой питания и др. Входы INT,

RST 5.5, RST6.5 - потенциальные (1 - запрос

прерывания), RST 7.5 - импульсный (переход

из 0 в 1 - запрос прерывания), TRAP - импульсный

и потенциальный. Приоритеты входов

расположены в последовательности,

указанной на рис. 1.24 (TRAP - высший приоритет).

Для управления прерываниями процессор

имеет две дополнительные команды чтения

RIM и установки SIM маски прерываний (табл.

1.12). Эти же команды используются для

управления передачей информации через

последовательные порты ввода SID и вывода

SOD, входящие в состав микропроцессора.

Форматы слов состояния и управления

прерываниями и последовательным

вводом/выводом показаны на рис. 1.26.

Разряды 3...0 используются для чтения/установки

масок прерываний. Маска общего разрешения

прерываний IF по входам INT, RST автоматически

сбрасывается после приема запросов

прерывания и устанавливается/сбрасывается

по командам EI, DI соответственно.

Индивидуальные маски по входам RST 7.5,

RST 6.5, RST 5.5 устанавливаются командой SIM

при MSE = 1. Разряды 7...4 команды RIM используются

для чтения состояния входов последовательного

ввода SID и прерываний RST 7.5, RST 6.5, RST 5.5.

Разряд 4 команды SIM - для сброса запроса

прерывания по входу RST 7.5 (после того он

опять способен принимать запросы

прерывания). Разряды 6, 7 команды SIM

используются для управления выводом

данных через последовательный выход

SOD. Изменение состояния порта SOD возможно

при SOE = 1.

при этом автоматически формируется

один для RST либо три для CALL сигнала

подтверждения прерываний. По командам

RST V осуществляется обращение к памяти

по адресам в зависимости от кода V (0000,

0008, 0010, 0018, 0020, 0028, 0030, 003816). По входам TRAP,

RST 5.5, RST 6.5, RST 7.5 обращение осуществляется

по фиксированным адресам ЗУ 0024, 002С,

0034, 00ЗС соответственно. Входы RST 5.5,

RST 6.5, RST 7.5 являются программно-маскируемыми,

вход TRAP немаскируемый и используется

для обслуживания аварийных ситуаций,

таких как сбой питания и др. Входы INT,

RST 5.5, RST6.5 - потенциальные (1 - запрос

прерывания), RST 7.5 - импульсный (переход

из 0 в 1 - запрос прерывания), TRAP - импульсный

и потенциальный. Приоритеты входов

расположены в последовательности,

указанной на рис. 1.24 (TRAP - высший приоритет).

Для управления прерываниями процессор

имеет две дополнительные команды чтения

RIM и установки SIM маски прерываний (табл.

1.12). Эти же команды используются для

управления передачей информации через

последовательные порты ввода SID и вывода

SOD, входящие в состав микропроцессора.

Форматы слов состояния и управления

прерываниями и последовательным

вводом/выводом показаны на рис. 1.26.

Разряды 3...0 используются для чтения/установки

масок прерываний. Маска общего разрешения

прерываний IF по входам INT, RST автоматически

сбрасывается после приема запросов

прерывания и устанавливается/сбрасывается

по командам EI, DI соответственно.

Индивидуальные маски по входам RST 7.5,

RST 6.5, RST 5.5 устанавливаются командой SIM

при MSE = 1. Разряды 7...4 команды RIM используются

для чтения состояния входов последовательного

ввода SID и прерываний RST 7.5, RST 6.5, RST 5.5.

Разряд 4 команды SIM - для сброса запроса

прерывания по входу RST 7.5 (после того он

опять способен принимать запросы

прерывания). Разряды 6, 7 команды SIM

используются для управления выводом

данных через последовательный выход

SOD. Изменение состояния порта SOD возможно

при SOE = 1.

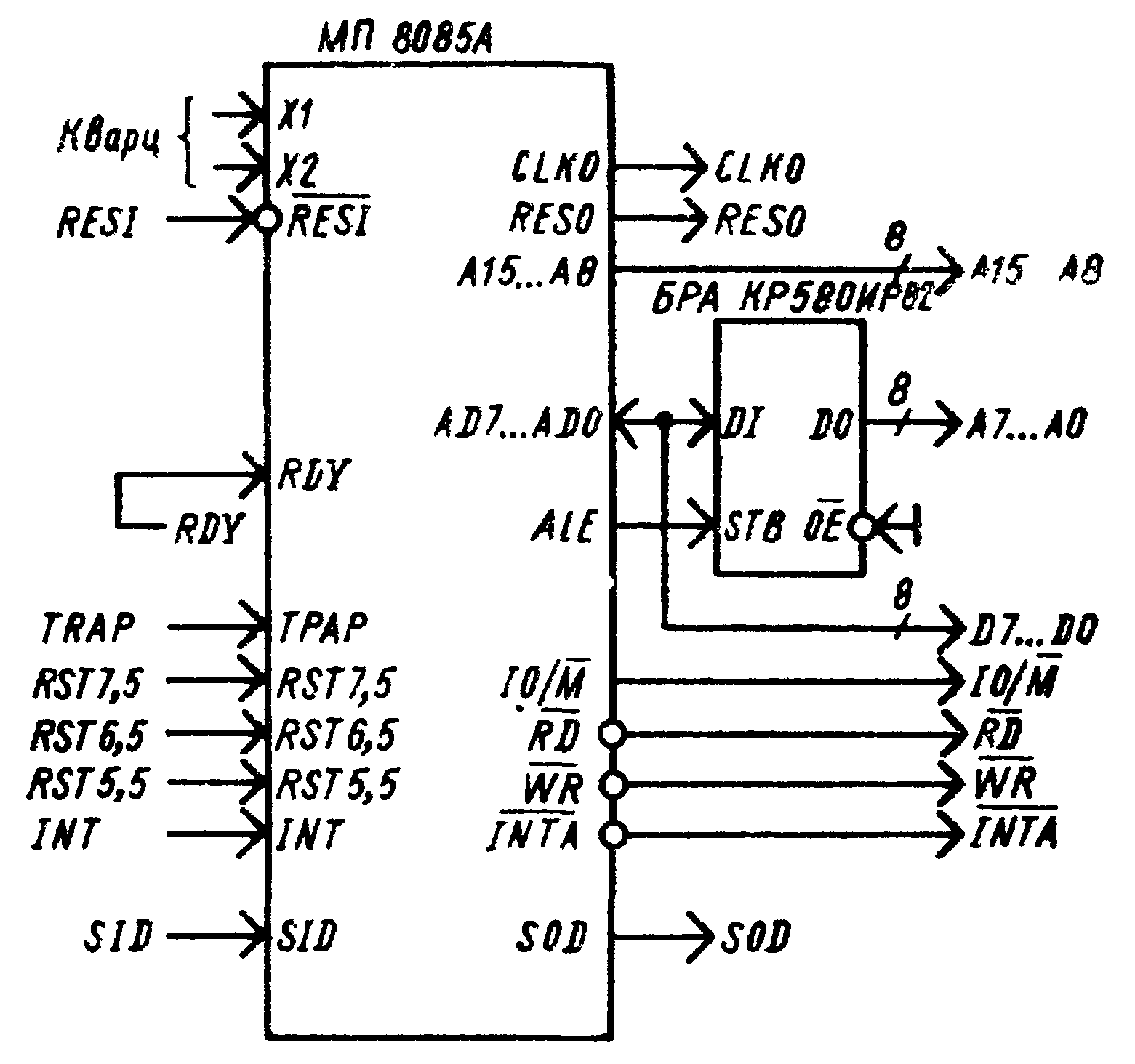

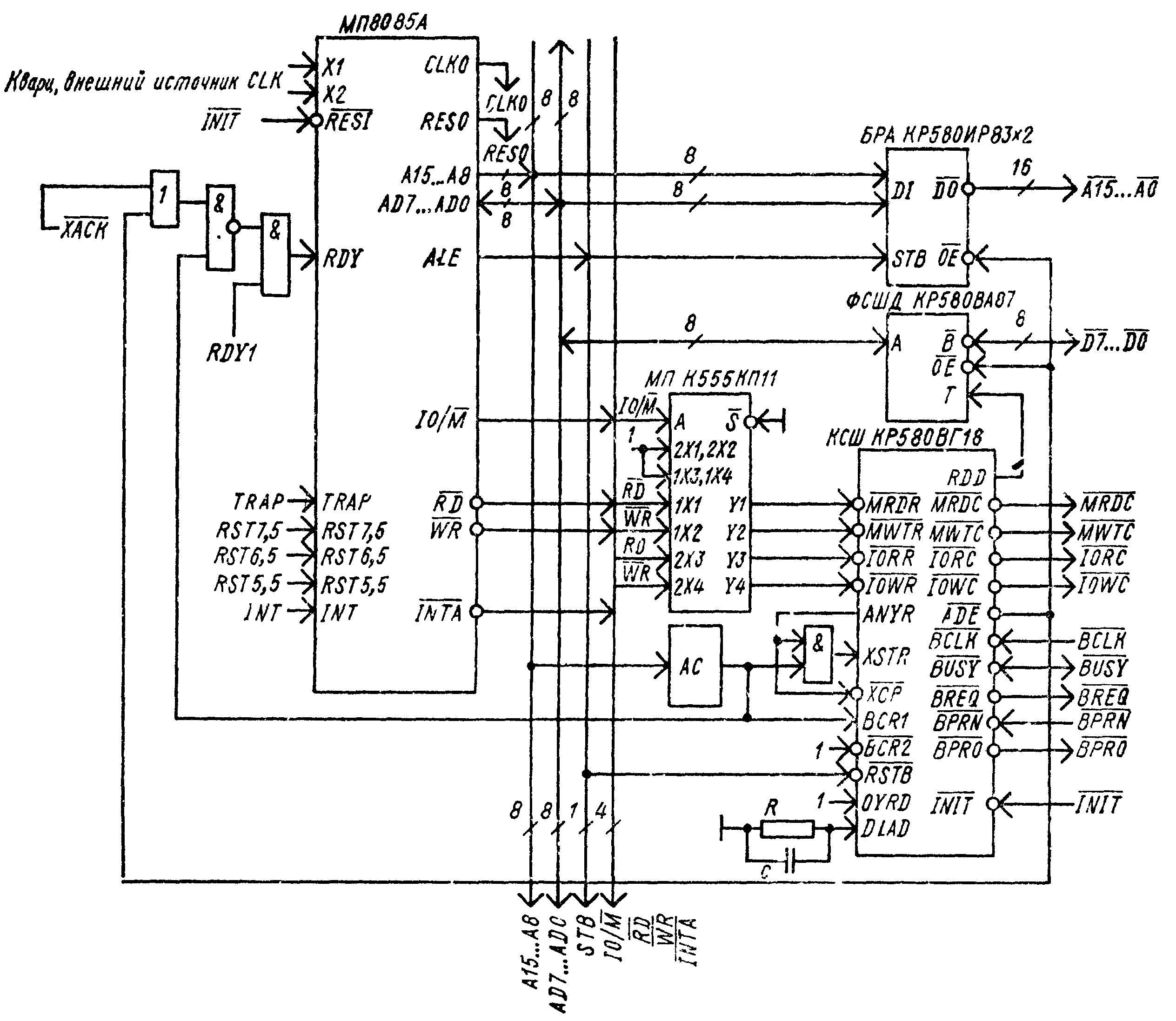

На МП 8085А реализуют процессоры с полусовмещенной системной шиной, раздельной однопользовательской или многопользовательской шинами. Структура процессора с совмещенной системной шиной показана на рис. 1.27. Системная шина небуферизована и ориентирована на работу с БИС ЗУ/интерфейсов ВУ МПК MCS-85: 8155/8156 и 8355/8755А. Нагрузочная способность шин - вентиль ТТЛ, а временные диаграммы их работы указаны на рис. 1.25. Для адресации ВУ можно использовать адресную шину А15...А8, т. к. на нее выставляется адрес ВУ в течение всего цикла выполнения команд ввода/вывода. Это позволяет адресовать БИС интерфейсов и контроллеров МПК КР580 без разделения шин.

Структура процессора с раздельной небуферизованной шиной показана на рис. 1.28. Для выделения адреса с шины AD7...AD0 используется буферный регистр адреса (БРА) на ИС КР580ИР82. Системная шина состоит из 16-разрядной адресной шины А15...А0 и 8-разряадой шины данных D7...D0. Для управления ЗУ/ВУ используется четыре линии IO/М, RD, неWR, неINTA с разделением доступа к ЗУ или ВУ сигналами на линии IO/М.

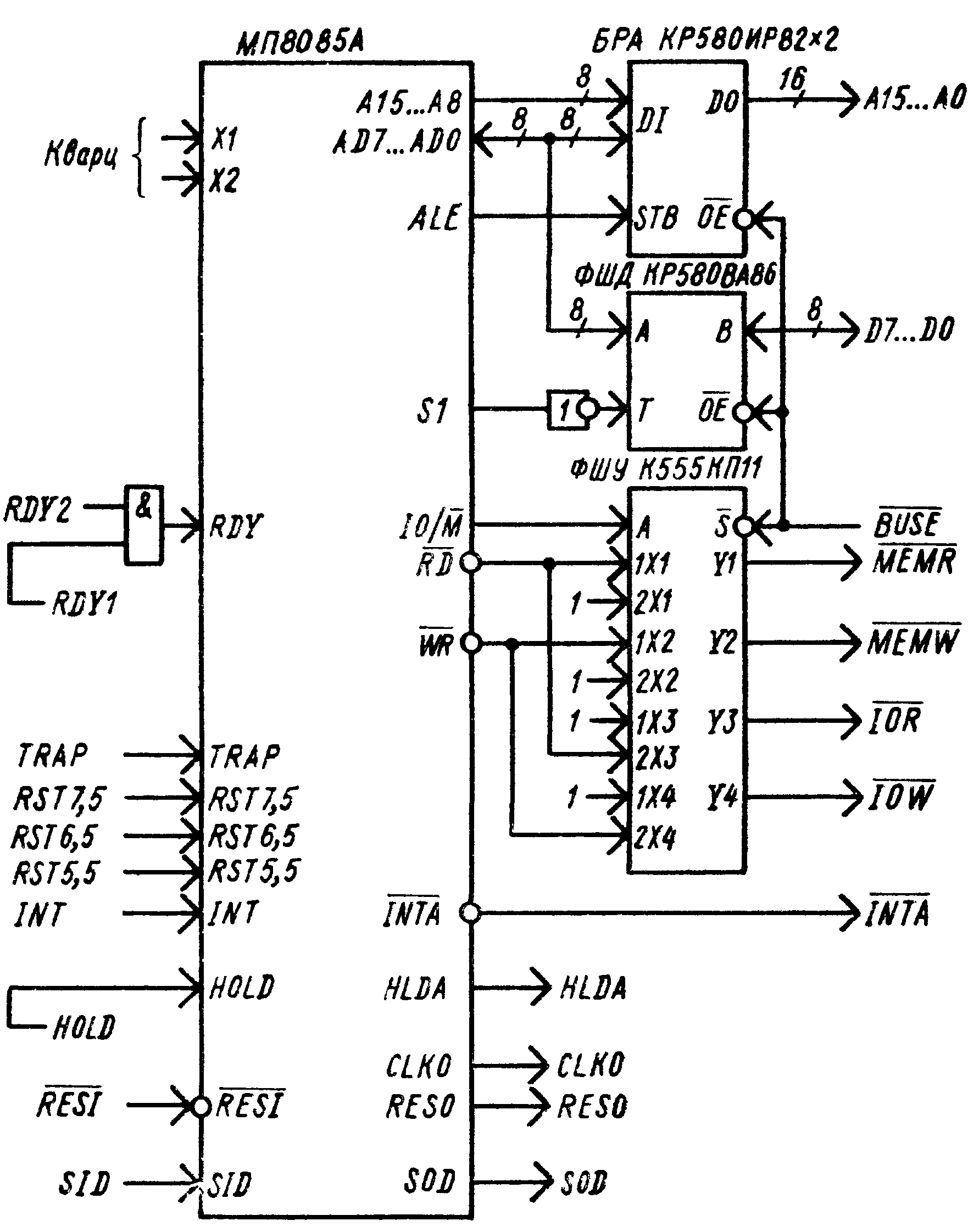

Структура процессора с однопользовательской раздельной системной шиной, совместимой с системной шиной процессора на БИС КР580, показана на рис. 1.29. Буферный регистр адреса выполнен на ИС КР580ИР82, а формирователь шины данных на ИС КР580ВА86, что обеспечивает ее нагрузочную способность 30 мА. Управляющие сигналы формирует ИС мультиплексора с трехстабильными выходами К555КП11.

Таблица 1.12 - Команды чтения и установки маски прерываний МП типа 8085А

Мнемокод |

Алгоритм |

Формат |

Число тактов |

7……0 |

|||

RIM |

A ← IM |

00100000 |

4 |

SIM |

IM ← A |

00110000 |

4 |

Рисунок 1.26 - Форматы слова состояния прерываний / последовательного входа (а) и слова управления прерываниями / последовательным выходом (б) МП 8085А

Рисунок 1.27 - Структура процессора на БИС 8085А с совмещенной небуферизованной системной шиной

Рисунок 1.28 - Структура процессора на БИС 8085А с раздельной небуфезированной системной шиной

Рисунок 1.29 - Структура процессора на БИС 8085А с однопользовательской системной шиной, совместимой с шиной процессора на БИС КР580

Рисунок 1.30 - Структура процессора на БИС 8085А с многопользовательской системной и однопользовательской локальной шинами

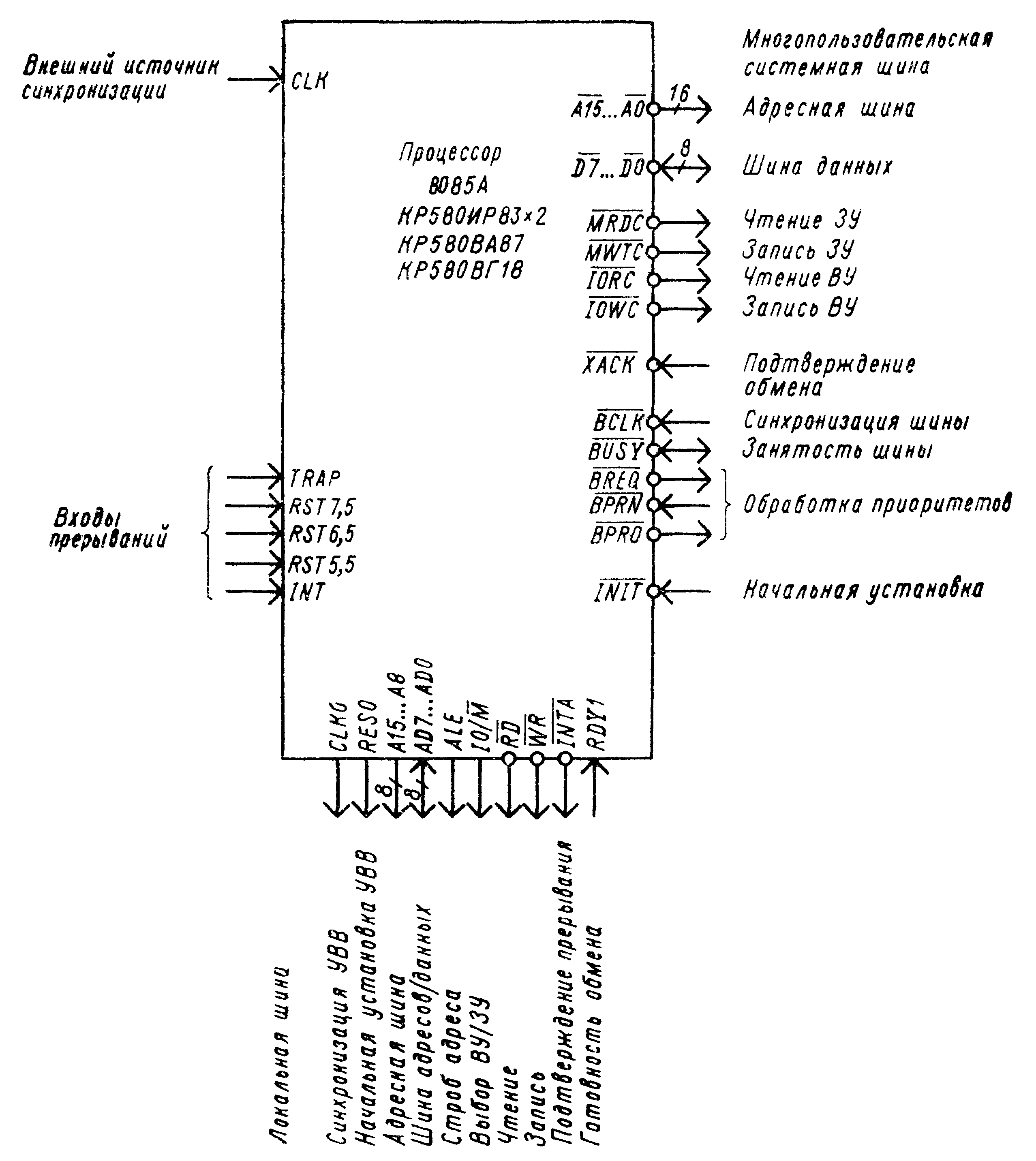

Процессор на БИС 8085А с многопользовательской системной шиной, как правило, содержит локальную шину для подключения локальных ЗУ/ВУ, реализуемых на соответствующих БИС МПК, MCS-85. Структура процессора показана на рис. 1.30, а состав его шин - на рис. 1.31. Интерфейс системной шины реализован как и в схеме процессора на ИС KP580. Для формирования сигналов управления чтением/записью и управления доступом к шине используется контроллер шины КР580ВГ18. Системная шина аналогична многопользовательской системной шине процессора на БИС КР580, что обеспечивает их аппаратную совместимость. Локальная шина - однопользовательская, совмещенная, небуферизованная, совместимая с ИС ЗУ/ИВУ МПК MCS-85.

Рисунок 1.31 - Состав шин процессора на БИС 8085А