- •А.Н. Лыков автоматизация технологических процессов и производств

- •Оглавление

- •Введение

- •1. Эффективность автоматизации. Надежность

- •1.1. Необходимость автоматизации

- •1.2. Факторы, влияющие на эффективность автоматизации

- •1.3. Показатели социально-экономической эффективности

- •Окупаемость:

- •Усиление желания внедрять автоматизацию (человеческий фактор):

- •План-график автоматизации:

- •1.4. «Подводные камни» при автоматизации

- •Еще раз о человеческом факторе

- •Секрет высокой надежности – отношение к делу производственного персонала:

- •1.6. Проблемы с надежностью в России

- •Наработка на отказ различных счпу

- •Качество микросхем

- •Контрольные вопросы

- •2. Автоматизация в машиностроении, системы чпу

- •2.1. Системы автоматизации в машиностроении

- •2.2. История развития счпу (до 1990 года)

- •2.3. Классификация существующих счпу

- •2.4. Промышленные роботы

- •2.4.1. Промышленные роботы (история начального развития)

- •2.4.2. Необходимость роботов

- •2.4.3. Сферы применения роботов

- •2.4.4. Примеры применения роботов

- •2.5. Словарь терминов и определений в счпу

- •Контрольные вопросы

- •3. Информация в системах автоматизации

- •3.1. Точность информации

- •3.2. Дискретизация по уровню и по времени непрерывного сигнала

- •3.3. Аппаратные информационные уровни

- •3.4. Преобразователи информации

- •3.5. Уровни управления в системах автоматизации

- •3.6. Тенденции в построении производственных систем

- •3.7. Фазы информационных преобразований для станка с счпу

- •3.8. Стандартизация и унификация средств автоматизации

- •Контрольные вопросы

- •4. Кодирование информации

- •4.1. Буквенные коды

- •4.2. Буквенно-цифровые коды

- •4.3. Цифровые коды

- •Код Грея в датчиках положения

- •Контрольные вопросы

- •5. Интегральные преобразователи информации

- •5.1. Интегральные догические микросхемы

- •5.2. Цифроаналоговые преобразователи (цап)

- •5.3. Аналого-цифровые преобразователи (ацп)

- •5.4. Цифроаналоговый процессор км1813ве1

- •Контрольные вопросы

- •6. ПреобразоваТели информации

- •6.1. Преобразователь «частота – напряжение»

- •6.2. Преобразователь «частота – код»

- •6.3. Преобразователь «код – частота»

- •6.4. Преобразователь «унитарный код – фаза»

- •6.5. Преобразователь «фаза – код»

- •6.6. Преобразователь «фаза – напряжение»

- •6.7. Узлы гальванической развязки в системах автоматизации

- •Контрольные вопросы

- •7. Управляющие программы счпу

- •7.1. Структура управляющих программ для станков с чпу

- •7.2. Значения символов адресов

- •7.3. Формат кадра учпу

- •7.4. Повышение языкового уровня управляющих программ

- •Контрольные вопросы

- •8. Сап станков и роботов

- •8.1. Подготовка управляющей программы (уп)

- •8.2. Системы автоматизированного программирования уп

- •8.3. Системы cad/cam

- •8.3.1. Система AutoCad

- •8.3.2. Система bCad

- •8.3.2.1. Плоское черчение

- •8.3.2.2. Объемное моделирование

- •8.3.2.3. Генерация чертежей

- •8.3.2.4. Статистика и расчет

- •8.3.2.5. Получение реалистических изображений

- •8.3.2.6. Пользовательский интерфейс

- •8.3.2.7. Совместимость

- •8.3.2.8. Перспективы

- •8.3.3. Система ГеМма-3d при производстве технологической оснастки на оборудовании с чпу

- •8.3.4. Продукты adem cad/cam

- •8.3.4.2. Модуль adem nс

- •8.3.5. Графика-81

- •8.3.6. Базис 3.5

- •8.3.6.1. Аппаратное обеспечение

- •8.3.6.2. Интерфейс пользователя

- •8.3.6.3. Построение изображения

- •8.3.6.4. Ввод текстовой информации

- •8.3.6.5. Инженерные расчеты

- •8.3.6.6. Связь с другими приложениями

- •8.3.7.1. Твердотельное моделирование

- •8.3.7.2. Сборки

- •8.3.7.3. Полезные «мелочи»

- •Контрольные вопросы

- •9. Интерполяция. Аппаратные стойки чпу

- •9.1. Траектории движения

- •9.2. Основные задачи при интерполяции

- •9.3. Математическое решение уравнений движения

- •9.4. Реализация интегрирования в счпу

- •9.5. Счпу «Контур-2пт»*

- •9.6. Счпу «н22»**

- •9.7. Счпу «н33»*

- •9.8. Блок задания скорости (бзс) аппаратной стойки чпу

- •Контрольные вопросы

- •10. Системы связи счпу со станком

- •10.1. Позиционные кодовые счпу

- •10.2. Позиционная счетно-импульсная счпу

- •10.3. Контурные счпу

- •10.4. Частичная инвариантность по управлению

- •10.5. Первые поколения контурных счпу

- •10.6. Фазовый индикаторный и разностный режимы работы устройства связи с электроприводом

- •10.7. Расчетные соотношения для фазовых систем

- •10.8. Микропроцессорные стойки чпу

- •Контрольные вопросы

- •11. Микропроцессорные счпу и тенденции развития

- •11.1. Архитектура и возможности микропроцессорных систем управления типа сnс до 1990 года (однопроцессорные мпс км85, 2р-32м, 2с42-45, многопроцессорные мпс Нейрон и3, мс2101, 3с150, s8600)

- •11.2. Новые системы чпу

- •11.2.1. Архитектура открытой системы чпу

- •11.2.2. Открытое ядро чпу

- •11.2.3. Системы чпу с web-доступом

- •11.2.4. Система понятий стандарта iso 14649

- •11.2.5. Чпу, воспринимающие стандарт step-nc

- •11.2.6. Среда разработки управляющих программ для систем чпу AdvancEd

- •11.3. Примеры интеллектуальных счпу последнего поколения

- •12.2. Лвс: доступ к каналу, способы кодирования, типы сообщений, сетевые системы

- •Контрольные вопросы

- •13. Автоматизированные системы контроля и учета энергоресурсов (аскуэ)

- •13.1. Требования к автоматизированным системам контроля и учета энергоресурсов

- •13.2. Уровни аскуэ

- •13.3. Коммерческие и технические аскуэ

- •13.4. Первичные измерительные приборы

- •13.5. Первые российские аскуэ

- •13.6. Современные аскуэ

- •13.7. Аскуэ бытовых потребителей

- •13.8. Энергосбережение и аскуэ

- •Контрольные вопросы

- •14. Автоматизация котельных

- •14.1. Описание и классификация котельных установок

- •14.2. Котельная как объект регулирования

- •14.3. Регулирование нагрузки котла

- •14.4. Регулирование уровня воды в барабане котла

- •14.5. Регулирование температуры перегретого пара

- •14.6. Управление вентилятором

- •14.7. Управление дымососом

- •14.8. Система управления шиберами

- •14.9. Автоматика безопасности котельной

- •14.10. Определение параметров объекта регулирования, регуляторов и настройка аср Расчет параметров объекта управления

- •Регуляторы с им постоянной скорости

- •Технически оптимальная настройка регуляторов

- •15. Автоматизация турбомеханизмов и энергосбережение

- •15.1. Характеристика турбомеханизмов

- •15.2. Расчет мощности на валу турбомеханизма

- •15.3. Регулирование производительности турбомеханизмов

- •15.4. Особенности регулирования скорости турбомеханизмов

- •15.5. Расчет экономической эффективности применения частотно-регулируемого электропривода

- •Список ЛитературЫ

- •Приложение ктс «Ресурс»

- •Ктс «Альфа Смарт», «Альфа Центр»

- •Птк «эком»

- •Технические характеристики аскуэ «Континиум»

- •Регистраторы аварийных событий

- •Список сокращений

- •Автоматизация технологических процессов и производств

5.2. Цифроаналоговые преобразователи (цап)

Требуются ЦАП и АЦП с различными характеристиками:

число разрядов от 8 до 20;

время преобразований от 0,01 мкс до 1 с.

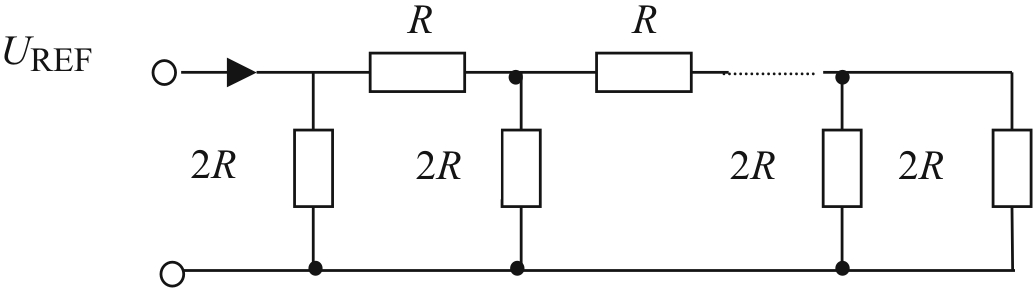

Интегральные ЦАП исполняются, как правило, по весовому принципу (рис. 5.5). ЦАП содержит резисторную матрицу R-2R и токовые ключи ТК. На вход ОУ поступает сумма токов тех разрядов двоичного числа, где есть единица. Токи определяются только резисторной матрицей. Если учесть то, что потенциал на входе ОУ равен нулю (при Kу → ), то весовая матрица получает вид, представленный на рис. 5.6. Сопротивление матрицы равно R.

Рис. 5.5. ЦАП, реализованный по весовому принципу на резисторной матрице R-2R

Рис. 5.6. Результирующее сопртивление резисторной матрицы

Откуда

![]() ,

где

,

где

![]() – опорное напряжение (обычно

– опорное напряжение (обычно

![]() ,

чтобы иметь вес младшего разряда 10 мВ).

,

чтобы иметь вес младшего разряда 10 мВ).

Сопротивления для выходного операционного усилителя тоже входят в состав прецизионных поликремниевых резисторов микросхемы.

Время преобразования не более 5 мкс.

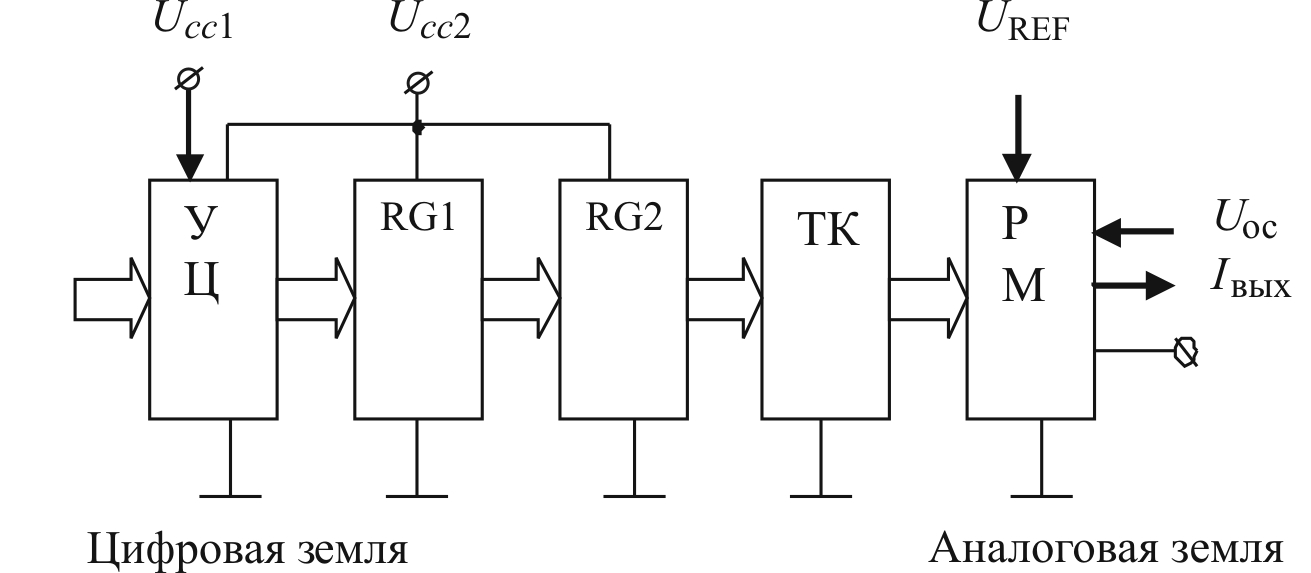

Микросхема К572ПА2 (рис. 5.7) позволяет преобразовывать 12 разрядов, содержит более 1000 элементов. В состав микросхемы входят:

УЦ – согласователь уровня ТТЛ с КМОП уровнем.

RG1, RG2 – регистры памяти для записи и хранения цифровой информации.

ТК – токовые ключи.

РМ – резисторная матрица, разрешающая способность H = 2,5 мВ при ,

,

,

,

,

.

.

Время преобразования – не более 15 мкс.

Рис. 5.7. Структура микросхемы ЦАП К572ПА2

Микросхема К594ПА1: 12-разрядная со встроенным источником тока на основе ОУ для повышения стабильности, tуст = 3,5 мкс.

Микросхема К1108ПА1: 12-разрядная, tуст = 0,4 мкс.

Микросхема К1118ПА: 8-разрядная, tуст = 40 нс.

Микросхема К1118ПА2: 10-разрядная, tуст = 80 нс.

5.3. Аналого-цифровые преобразователи (ацп)

Принципы исполнения АЦП:

последовательного счета;

последовательных приближений;

параллельного считывания;

интегрирующие.

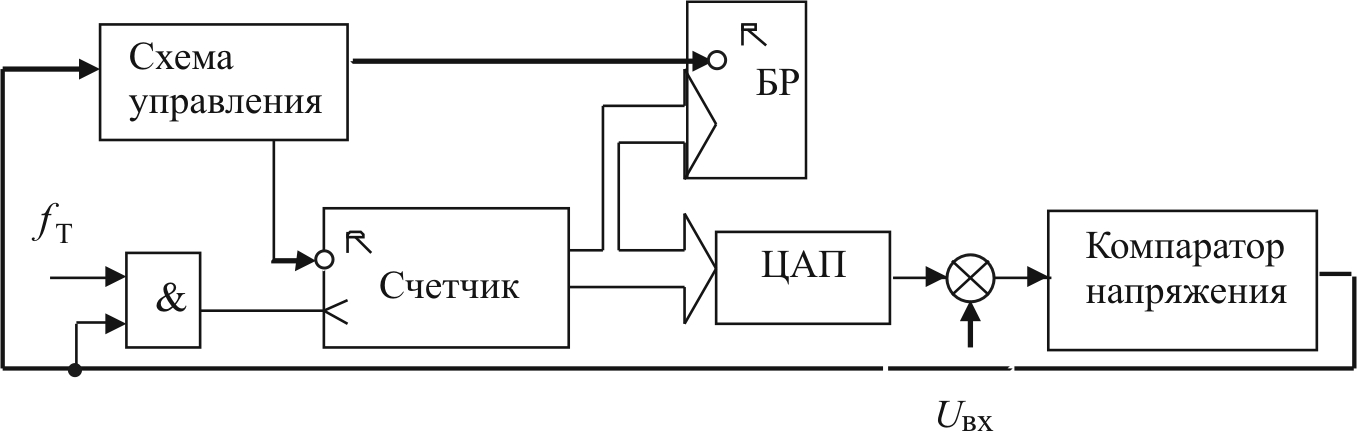

Принцип работы АЦП с последовательным счетом представлен на рис. 5.8.

Рис. 5.8. Структура АЦП с последовательным счетом

Заполнение счетчика тактовой частоты до тех пор, пока выходное напряжение ЦАП, полученное при преобразовании кода счетчика, не сравняется с входным напряжением. Данный принцип применялся, когда не было интегральных АЦП.

В интегральных АЦП применяются три последних принципа.

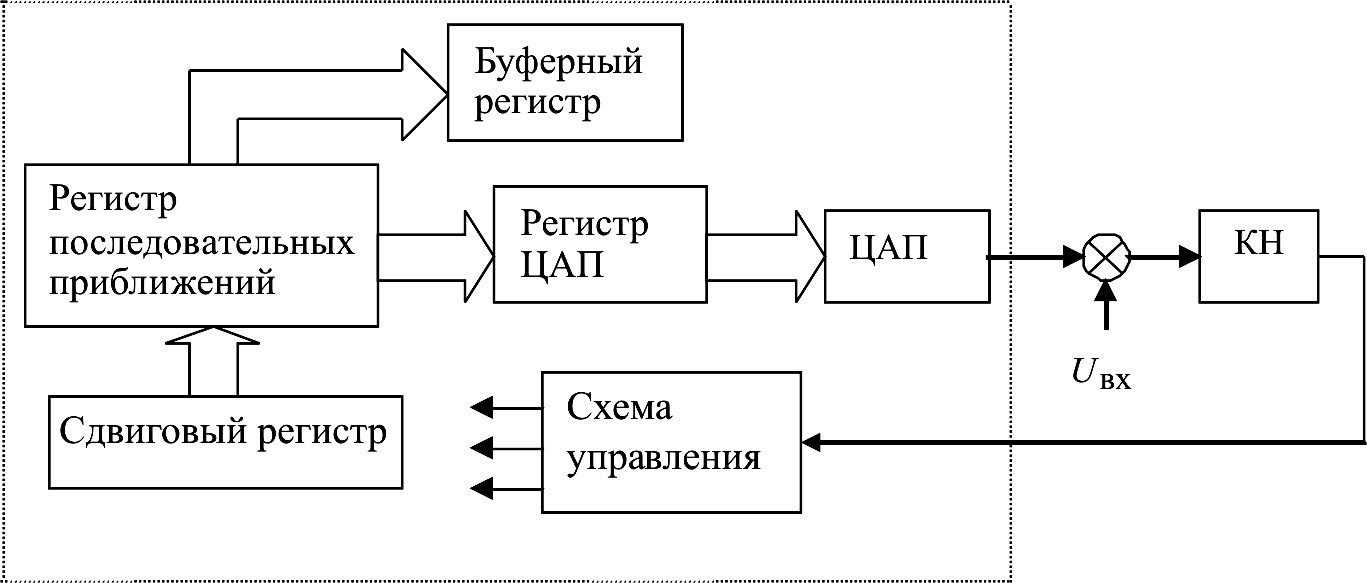

Структура АЦП, выполненного по методу последовательных приближений, дана на рис. 5.9.

По этому методу сдвиговый регистр поочередно добавляет единицу в разряды регистра последовательных приближений, начиная со старшего. Если компаратор напряжения при этом отмечает, что напряжение ЦАП больше Uвх, то эта очередная единица в регистрах не фиксируется (иначе – фиксируется). Таким образом происходит «взвешивание» всех разрядов двоичного кода.

Рис. 5.9. Структура АЦП по методу последовательных приближений

Для получения 12-разрядного кода при , примененного для ЦАП, каждому разряду кода соответствует аналоговый сигнал (табл. 5.2).

Таблица 5.2

Последовательность преобразования АЦП

Такт

|

Вес ЦАП в этом такте |

Код в регистре последовательных приближений |

Выход ЦАП |

Результат накапливаемый |

1 2 3 4 5 6 7 8 9 10 11 12 |

5,12 2,56 1,28 0,64 0,32 0,16 0,08 0,04 0,02 0,01 0,005 0,0025 |

100000000000 110000000000 111000000000 110100000000 110010000000 110011000000 110010100000 110010010000 110010011000 110010010100 110010010110 110010010101 |

5,12 7,68 8,96 8,32 8,00 8,16 8,08 8,04 8,06 8,05 8,055 8,0525 |

100000000000 110000000000 110000000000 110000000000 110010000000 110010000000 110010000000 110010010000 110010010000 110010010100 110010010100 110010010100 |

В этой таблице

показаны все 12 тактов последовательного

взвешивания для

![]() .

.

Буферный регистр обычно имеет три стабильных состояния выходов, может выдавать информацию побайтно или 16-разрядным словом, в параллельном коде или последовательном по сигналам на считывание.

Внешний компаратор напряжения применяют для того, чтобы повысить точность.

Примеры АЦП последовательных приближений.

К572ПВ1 – 12-разрядный,

.

.К572ПВ3 – 8-разрядный внутренний компаратор,

.

.К1108ПВ1 – 10-разрядный, внутренние компаратор и источник опорного напряжения,

,

Uвх

= 0…3 В.

,

Uвх

= 0…3 В.К1108ПВ2 – 12-разрядный, Uвх = 0…5 В,

.

.К1113ПВ1 – 10-разрядный,

.

.К574ПВ4 – 8-разрядный, 8 входов (есть мультиплексор на входе), ОЗУ 8×8, считывание ОЗУ внешним устройством (микропроцессором).

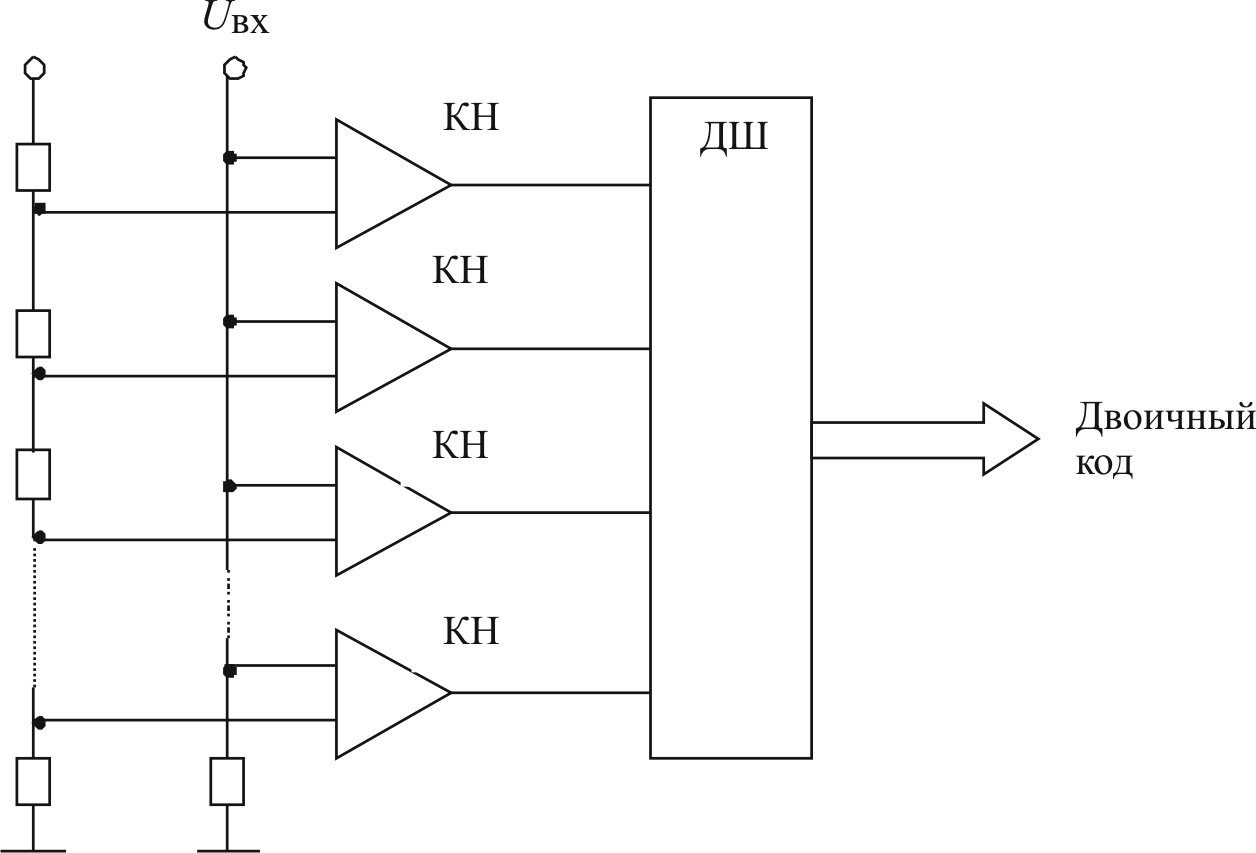

АЦП параллельного считывания

Это наиболее быстродействующие преобразователи, так как сравнение с делителем напряжения, имеющим 2n ступеней, где n – разрядность АЦП, происходит каждый такт. Структура подобного АЦП приведена на рис. 5.10.

С компараторов следует позиционный код, когда верхние компараторы будут все в «1», нижние – в «0». Позиционный код преобразуется в двоичный код.

Примеры АЦП параллельного считывания:

К1107ПВ1 – 6-разрядный, Uвх = 0…2 В,

.

.К1107ПВ2 – 8-разрядный (уже 256 компараторов), .

К1107ПВ3 (ЭСЛ структура) – 6-разрядный,

.

.К1107ПВ4 – 8-разрядный,

.

.К1126ПВ1 – двухканальный АЦП – 3-разрядные (для электронного щитка автомобиля).

Рис. 5.10. Структура АЦП параллельного считывания

Интегрирующие АЦП

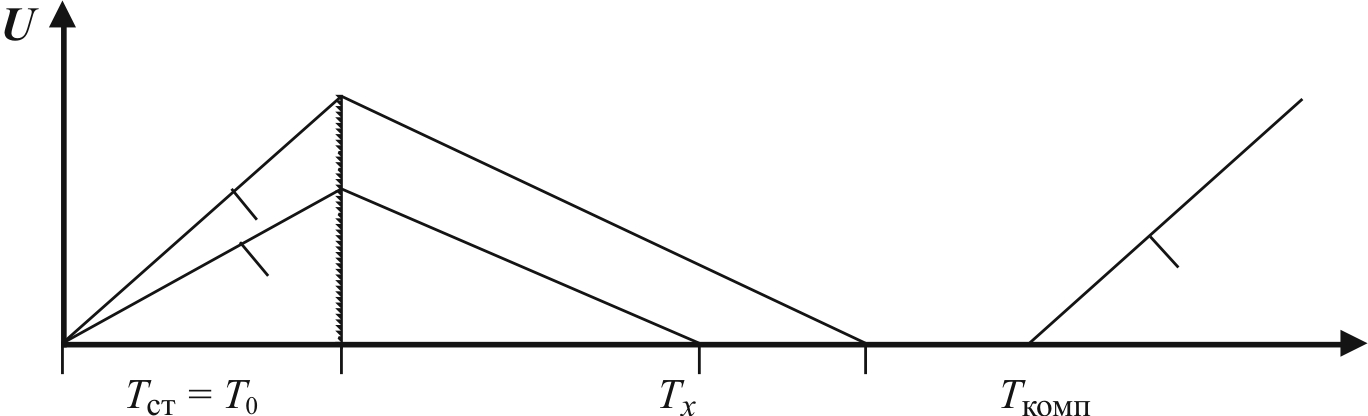

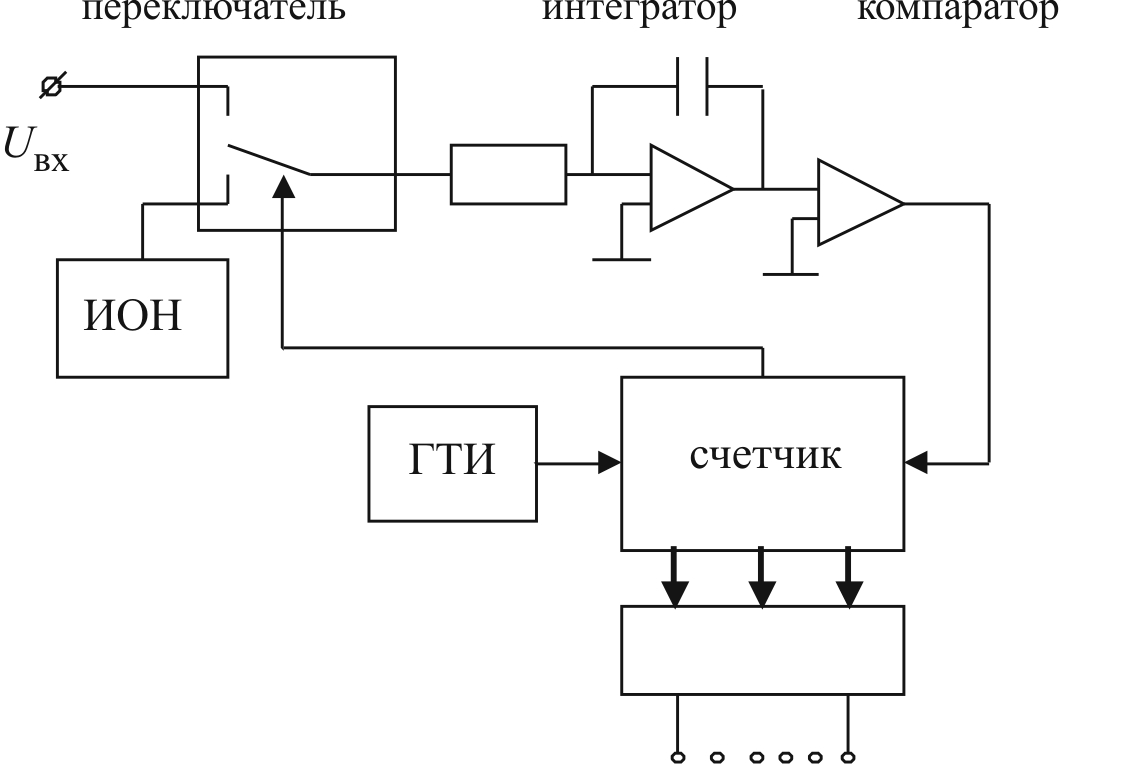

Наименьшее быстродействие, но простота, выход сразу на индикацию. Осуществляется двойное интегрирование с автоматической коррекцией нуля и определением полярности сигнала. Структурная схема интегрирующего АЦП приведена на рис. 5.12, временная диаграмма работы – на рис. 5.11.

На 1-м этапе интегратор заряжается от Uвх со стабильной длительностью. На 2-м отрезке интегратор разряжается от стабильного источника UREF, ведется подсчет времени разряда Tх. На третьем отрезке производится компенсация дрейфа нуля интегратора. Все временные отрезки отмеряются путем подсчета тактовых импульсов счетчиком.

Рис. 5.11. Временная диаграмма работы интегрирующего АЦП

Рис. 5.12. Структура интегрирующего АЦП: ИОН – источник опорного напряжения; ГТИ – генератор тактовых импульсов

Учитывая равенство заряда и разряда:

![]() .

Принимая Ux = const

за период интегрирования, получаем

.

Принимая Ux = const

за период интегрирования, получаем

![]() ,

т.е.

,

т.е.

![]()

Пример интегрирующего АЦП:

К572ПВ2 – выходной код, специальный для непосредственного управления 7-сегментным десятичным индикатором на 3,5 декады (до 4999).

Здесь не требуются ЦАП с высокоточными резисторными матрицами, нет высоких требований к стабильности интегратора, тактовой частоты (увеличение fT приводит к уменьшению Tст, но тогда меньше будет и время разряда). Схема позволяет хорошо подавить сетевые помехи (входной сигнал измеряется как среднее за Tст).

К572ПВ1, К572ПВ2 – tзар = 4103 периодов fT;

tразр mах = 8103 периодов fT;

tавтокомп ≈ 4103 периодов fT или 16103 fT;

fT кратна 50 Гц (50, 100, 200 кГц);

При fT = 200 кГц цикл работы t∑ = 16103/ fT = 80 мс.

При δ < 0,1 % высокая помехозащищенность и дешевизна.