- •Введение

- •1 Интегральные микросхемы и их элементы

- •1.1 Общие сведения о микроэлектронике

- •1.2 Классификация интегральных микросхем (имс)

- •1.3 Плёночные, гибридные и совмещенные ис

- •1.3.1 Плёночные ис

- •1.3.2 Технология изготовления плёночных имс

- •1.3.3 Изготовление маски (трафарета)

- •1.3.4 Гибридные имс

- •1.3.5 Совмещённые имс

- •1.4 Полупроводниковые имс

- •1.4.1 Транзисторы биполярные

- •1.4.2 Планарная технология изготовления имс

- •1.4.3 Планарно-эпитаксиальная технология изготовления имс

- •1.4.4 Диоды

- •1.4.5 Резисторы

- •1.4.6 Конденсаторы

- •1.4.7 Индуктивности

- •1.4.8 Изоляция элементов имс.

- •1.4.9 Корпуса для имс

- •1.4.11 Внутрисхемные соединения

- •1.5 Разновидности транзисторов

- •1.5.1 Транзистор с барьером Шоттки.

- •1.5.2 Многоэмиттерный транзистор

- •1 .5.3 Составные транзисторы

- •1.5.4 Биполярные транзисторы с инжекционным питанием

- •1.5.5 Приборы с зарядовой связью

- •1.5.6 Монокристалл

- •1.6 Функциональные устройства

- •2 Цифровые интегральные схемы

- •2.1 Основные логические операции и логические элементы.

- •2.1.1 Основные аксиомы и теоремы алгебры логики

- •2.1.2 Основные параметры логических интегральных микросхем

- •2.2 Логические интегральные схемы

- •2.2.1 Схема ртл ‑ резисторно-транзисторной логики

- •2.2.2 Схема дтл ‑ диодно-транзисторной логики

- •2.2.3 Схемы ттл ‑ транзисторно-транзисторной логики

- •2.2.3.1 Схема ттл ‑ транзисторно-транзисторной логики с простым инвертором

- •2.2.3.2 Схема ттл со сложным инвертором

- •2.2.3.3 Схема ттл с расширителем по или

- •2.2.3.4 Схема ттл с коррекцией передаточной характеристики

- •2.2.3.5 Разновидности схем ттл

- •2.2.4 Схемы эсл ‑ эмиттерно-связанной логики

- •2.2.4.1 Особенности эсл

- •2.2.4.2 Переключатель тока.

- •2.2.4.3 Принцип действия базовой схемы эсл

- •2.2.4.4 Разновидности схем эсл

- •2.2.5 Логические элементы на полевых транзисторах

- •2.2.5.1 Логические элементы на мдп

- •2.2.6 Логические элементы интегрально-инжекционной логики (иил)

- •3 Аналоговые интегральные схемы

- •3.1 Дифференциальный усилитель. Режимы работы

- •3.1.1 Дифференциальный усилитель с генератором стабильного тока

- •3.1.2 Разновидности схем дифференциальных усилителей

- •3.1.3 Дифференциальный усилитель с динамической нагрузкой

- •3.2 Интегральные операционные усилители

- •3.2.1 Назначение и основные параметры операционных усилителей

- •4 Цифровые запоминающие устройства

- •4.1. Оперативные запоминающие устройства

- •4.2. Динамические озу

- •4.3 Постоянные запоминающие устройства

- •Список литературы

2 Цифровые интегральные схемы

2.1 Основные логические операции и логические элементы.

Логические функции ‑ функции, которые принимают два значения:

F=0, если сообщение ложное,

F=1, если сообщение истинное.

Логические операции описывают связь между логическими функциями.

Электрические схемы, реализующие элементарные логические операции, называются логическими элементами (ЛЭ).

Существуют 3 простейших логических операции: НЕ, ИЛИ, И.

а) Операция НЕ - логическое отрицание, инверсия.

![]()

(F равно не А)

(F равно не А)

ЛЭ, выполняющий операцию НЕ, называется инвертором (рисунок 2.1). Его таблица истинности приведена в таблице 2.1.

Таблица 2.1

А |

|

0 |

1 |

1 |

0 |

Временные диаграммы приведены на рисунке 2.2.

Здесь потенциал Е принимается за единичное значение “1”. За ноль принимается нулевое значение логической функции.

Простейшая реализация инвертора ‑ транзисторный ключ (рисунок 2.3).

При А = 1, т.е UВХ

= E, транзистор

открыт и насыщен. UВЫХ=

Uкн

=

0, т.е.

![]() .

.

При А = 0, т.е. UВХ

= 0, транзистор заперт, UВЫХ

= Ек,

т.е.

![]() .

.

б) Операция ИЛИ ‑ логическое сложение, дизъюнкция.

F=АВ, либо F=А+В (F есть А или В).

ЛЭ, выполняющий операцию ИЛИ, называется сборкой или дизъюнктором (рисунок 2.4). Таблица истинности для операции ИЛИ показана в таблице 2.2.

А |

В |

А+В |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

Таблица 2.2

Временные диаграммы приведены на рисунке 2.5. Выходной сигнал равен единице, если хотя бы один из аргументов равен единице.

Простейшая реализация операции ИЛИ возможна на диодной сборке (рисунок 2.6).

В схеме достаточно подать “+Е” хотя бы на один из входов, чтобы на выходе появился положительный сигнал Е, т.е. F = 1.

в) Операция “И”- логическое умножение или конъюнкция.

F=A![]() B

(F есть А и В);

B

(F есть А и В);

F=AB.

Логический элемент, выполняющий операцию И называется схемой совпадения, или конъюнктором (рисунок 2.7).

Таблица 2.3

А |

В |

АВ |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

На рисунке 2.8 показаны временные диаграммы конъюнктора (рисунок 2.7), из которого видно, что выходной сигнал равен единице, только в том случае, если все входные сигналы равны единице.

Простейшая реализация операции И возможна на диодной схеме совпадения (рисунок 2.9).

В схеме RH >> R. Если хотя бы на одном из входов низкий уровень напряжения, т.е. около нуля, откроется диод на этом входе, потечет ток через открытый диод, и напряжение на RH UВЫХ будет равно нулю. UВЫХ будет равно единице только в случае, если запрутся все диоды на входе, т.е., если на всех входах высокий уровень напряжения.

Этот набор элементов И, НЕ, ИЛИ называется основным базисом или основной функционально полной системой элементов. Т.е. с помощью только этих элементов можно создать любую логическую схему.

Более широко в схемотехнике используются элементы других базисов ‑ двухступенчатые ИЛИ-НЕ, И-НЕ:

а) стрелка Пирса, или отрицание дизъюнкции, или операция ИЛИ-НЕ

АВ =

![]() .

.

Условное обозначение приведено на рисунке 2.10. Логический элемент называется элементом Пирса.

Таблица истинности представлена в таблице 2.4

Таблица 2.4

А |

В |

|

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

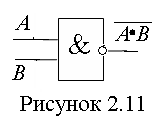

б) Штрих Шеффера, или отрицание конъюнкции, или операция И-НЕ

АВ =

![]() .

Таблица истинности представлена в

таблице 2.5.

.

Таблица истинности представлена в

таблице 2.5.

Таблица 2.5

-

А

В

0

0

1

0

1

1

1

0

1

1

1

0

У словное

обозначение приведено на рисунке 2.11.

Логический элемент называется элементом

Шеффера.

словное

обозначение приведено на рисунке 2.11.

Логический элемент называется элементом

Шеффера.

С помощью только одного типа микросхем ИЛИ-НЕ, либо И-НЕ можно построить любую логическую схему, т.е. каждая из них является основным базисом.

Самым распространенным является элемент Шеффера И-НЕ.

Т акже

широкое применение нашли многоступенчатые

логические элементы:

акже

широкое применение нашли многоступенчатые

логические элементы:

а) 2И-ИЛИ-НЕ, выполняющее операцию

![]() .

Условное обозначение приведено на

рисунке 2.12.

.

Условное обозначение приведено на

рисунке 2.12.

б) исключающее ИЛИ, или сумма по модулю два, или функция неравнозначности имеет вид

F =

![]() Это означает, что F

равно либо A, либо B.

Логический элемент исключающее ИЛИ

иногда называют элементом типа

«что-нибудь, но не все». Символ

Это означает, что F

равно либо A, либо B.

Логический элемент исключающее ИЛИ

иногда называют элементом типа

«что-нибудь, но не все». Символ

![]() (псевдоплюс) означает, что входы А

и В связаны логической функцией

исключающее ИЛИ.

(псевдоплюс) означает, что входы А

и В связаны логической функцией

исключающее ИЛИ.

Из алгебры логики известно:

![]() ;

;

![]()

![]() ;

;

![]() .

.

Таблица истинности для элемента исключающее ИЛИ приведена в таблице 2.6.

Таблица 2.6

А |

В |

А В |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

Из таблицы видно, что, если на какой-либо из входов (но не на все) подана логическая единица, то на выходе также появляется единица. Сравните с таблицей 2.3 (ИЛИ).

Условное обозначение элемента неравнозначности приведено на рисунке 2.13,а. Поскольку этот элемент выполняет операцию сложения по модулю 2, то его обозначают так же, как на рисунке 2.13,б.

в) исключающее ИЛИ-НЕ, или функция равнозначности имеет вид

![]() .

Это означает, что F

равно инверсии либо A,

либо B.

.

Это означает, что F

равно инверсии либо A,

либо B.

Таблица истинности для элемента исключающее ИЛИ-НЕ приведена в таблице 2.7.

А |

В |

|

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

Условное обозначение элемента равнозначности приведено на рисунке 2.14