- •1.Электропроводность полу проводников.

- •3.Прямое и обратное смещение р-п перехода.

- •4.Вольтамперная характеристика.

- •5.Основные параметры р-п перехода.

- •6.Пробой р-п перехода.

- •7.Методы изготовления р-п перехода.

- •8.Выпрямительный диод.

- •10.Варикап.

- •11.Туннельный диод. Обращенный диод.

- •12.Контакт металл-полупроводник. Диод Шоттки.

- •13.Классификация транзисторов.

- •14.Устройство биполярного транзистора.

- •15.Принцип действия транзистора.

- •16.Токи в транзисторе.

- •18.Схемы включения транзистора с об, оэ, ок.

- •19.Основные параметры транзисторов: а) физические б) һ-параметры.

- •20.Основные характеристики транзисторов, таблица основных параметров.

- •21.Характеристики с оэ (входные, выходные, прямой передачи тока).

- •22.Униполярные транзисторы с управляющим р-n переходом.

- •23.Униполярные транзисторы с изолированным затвором.

- •24.Тиристор, динистор.

- •27.Фотодиод, вах.

- •29.Классификация интегральных схем.

- •30.Усилители. Структурная схема. Классификация.

- •39.Дифференциальный усилитель с генератором стабильного тока (ду с гст)

- •40.Дифференциальный усилнтель с динамической нагрузкой (с зеркалом токов).

- •32.Однокаскадный усилитель.

- •41.Операционный усилитель, общие сведения.

- •42.Операционный усилитель, основные параметры.

- •43.Операционный усилитель, струкгурная и принципиальная схемы.

- •44.Основные логические операции и логические элементы.

- •45Анализ и синтез клс.

- •46Минимизация логических функций.

- •47. Схема ттл транзисторно-транзисторной логики с простым инвертом.

- •48Схема эсл эмитгерно-связанной логики.

- •49 Переключатель тока.

- •55.Схема и - не на мдп и кмдп.

- •56.Мультиплексор

- •57.Демультиплексор.

- •58.Дешифратор.

- •59.Шифратор.

- •60.Триггеры, классификация.

- •65.Регистр хранения.

- •6 6.Регистр сдвига.

- •67. Счетчики суммирующие.

- •68.Счетчики вычитающие.

- •69. Десятичный счетчик.

- •70.Операционный усилитель, внешние цепи.

- •71.0Перационный усилитель с отрицательной обратной связью.

- •79.Тригтер Шмита

- •80.Генераторы сигналов, условия самовозбуждения генератора.

- •82.Мультивибратор.

- •83.Генератор линейно-изменяющегося напряжения.

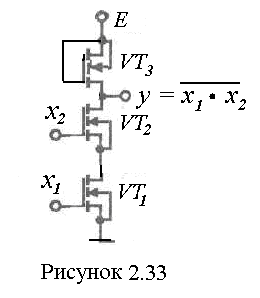

55.Схема и - не на мдп и кмдп.

В

схеме И-НЕ на МДП (2.33)

Если хотя бы на один из входов подан 0,

соответствующий транзистор запирается,

и на выходе схемы будет 1. И только при

подаче на все входы схемы 1 транзисторы

VT1

и VT2

откроются, и на выходе будет 0. *В

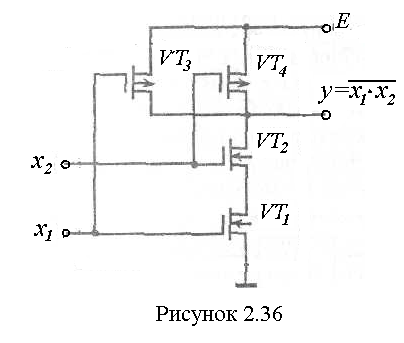

схеме И-НЕ на КМДП (2.33)

параллельно соединены транзисторы

с каналами р-типа,

а последовательно

— с каналами п-типа.

0

на выходе

устанавливается только

при одновременной подаче на оба входа

элемента 1,

а во всех остальных случаях на выходе

будет присутствовать

1. При

одновременной подаче на входы x1

и

x2

1

транзисторы VT1

и

VT2

открываются,

а транзисторы VT3

и VT4

закр. На

выходе 0.

При подаче хотя бы на один из

входов 0. На выходе 1.

схеме И-НЕ на МДП (2.33)

Если хотя бы на один из входов подан 0,

соответствующий транзистор запирается,

и на выходе схемы будет 1. И только при

подаче на все входы схемы 1 транзисторы

VT1

и VT2

откроются, и на выходе будет 0. *В

схеме И-НЕ на КМДП (2.33)

параллельно соединены транзисторы

с каналами р-типа,

а последовательно

— с каналами п-типа.

0

на выходе

устанавливается только

при одновременной подаче на оба входа

элемента 1,

а во всех остальных случаях на выходе

будет присутствовать

1. При

одновременной подаче на входы x1

и

x2

1

транзисторы VT1

и

VT2

открываются,

а транзисторы VT3

и VT4

закр. На

выходе 0.

При подаче хотя бы на один из

входов 0. На выходе 1.

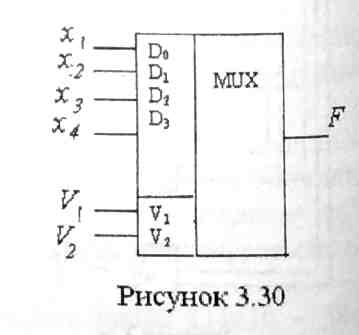

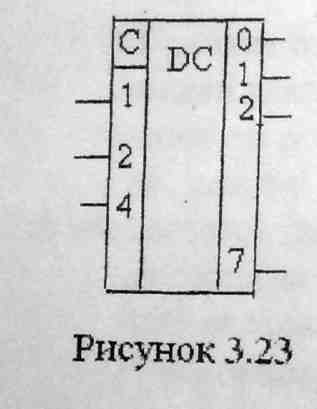

56.Мультиплексор

-многовходовая

КЛС с одним выходом, подключает

единственную общую выходную шину к

одному из входов в зависимости

от управляющего сигнала,

заданного двоичным

кодом.Применяется

для преобразования

параллельного кода в последовательный,

сравнения кодов и т.д. Бывают 4в1,8в1,16в1.

-многовходовая

КЛС с одним выходом, подключает

единственную общую выходную шину к

одному из входов в зависимости

от управляющего сигнала,

заданного двоичным

кодом.Применяется

для преобразования

параллельного кода в последовательный,

сравнения кодов и т.д. Бывают 4в1,8в1,16в1.

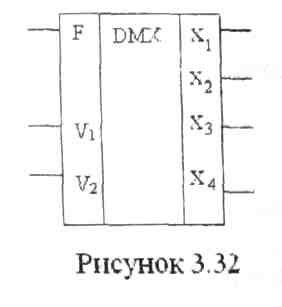

57.Демультиплексор.

Д -

это КЛС, имеющая один информационный

вход Ғ, к

управляющих

входов Vk..V1

и п

информацонных

выходов (х1...хn).

Коэффициент

усиления используется для распределения

данных одного канала

между несколькими приемниками.

Бывают

-

это КЛС, имеющая один информационный

вход Ғ, к

управляющих

входов Vk..V1

и п

информацонных

выходов (х1...хn).

Коэффициент

усиления используется для распределения

данных одного канала

между несколькими приемниками.

Бывают

4в1,8в1,16в1.

58.Дешифратор.

Д -

мног о в ь гх о д н а я к о м б и н а ционная

л о ги ч еская схема (КЛС), в кот каждой

ком бинации переменных на входе с о

о т в е т с тву е т единйчный

сигнал только на одном из выходов.Д

в ои чные д е ш и ф р а т о р ы преобразуют

двоичный код в код «1 из к».В

дешифраторе иногда выполняется

операция стробирования, разрешающая

выработку

выходных сигналов с определенным

интервалом времени.

Дешифратор

называется полным, если к

=2п

, т.е. реализует

все минтермы.

-

мног о в ь гх о д н а я к о м б и н а ционная

л о ги ч еская схема (КЛС), в кот каждой

ком бинации переменных на входе с о

о т в е т с тву е т единйчный

сигнал только на одном из выходов.Д

в ои чные д е ш и ф р а т о р ы преобразуют

двоичный код в код «1 из к».В

дешифраторе иногда выполняется

операция стробирования, разрешающая

выработку

выходных сигналов с определенным

интервалом времени.

Дешифратор

называется полным, если к

=2п

, т.е. реализует

все минтермы.

59.Шифратор.

Ш ифратор

(СД)

вьшолняет

функцию, обратную функции дешифратора.Двоичный

шифратор - КЛС, преобразует код "1 из

N" в двоичный. При наличии

«1» на одном из входов, появляется

n-элементная

комбинация на выходе,

соответствующая номеру возбужденного

входа.Шифратор

применяется для ввода данных с клавиатуры,

для преобразования

в двоичный код номера нажатой кнопки и

т.д. Полный двоичный

шифратор имеет Nвх =2^

n

-

входов, где и- число выходов, неполный

ифратор

(СД)

вьшолняет

функцию, обратную функции дешифратора.Двоичный

шифратор - КЛС, преобразует код "1 из

N" в двоичный. При наличии

«1» на одном из входов, появляется

n-элементная

комбинация на выходе,

соответствующая номеру возбужденного

входа.Шифратор

применяется для ввода данных с клавиатуры,

для преобразования

в двоичный код номера нажатой кнопки и

т.д. Полный двоичный

шифратор имеет Nвх =2^

n

-

входов, где и- число выходов, неполный

60.Триггеры, классификация.

триггер имеет два устойчивых состояния равновесия - «1» и «0»это запоминающий элемент для временного хранения информации. Имеет два выхода: прямой и инверсный.Классификация:1) RS-триггер с раздельной установкой 0 и 1;2) D-триггер с приемом информации по 1 входу. повторяет входной сигнал с задержкой;3) Т-триггер со счетным входом, переброс триггера происходит с каждым очередным сигналом; 4) DV-, TV- имеют дополнительный вход;5)JK-триггтер - универсальный триггер с раздельной установкой «0» и «1». Наборы 11 не запрещены. 6) комбинированный триггер совмещает несколько режимов; 7)триггер со сложной логикой 61. Синхронный RS-триггер.

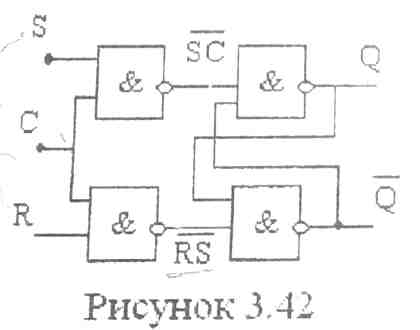

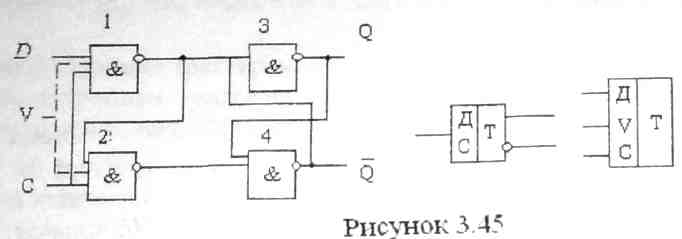

.42схема

тактируемого RS-триггера

на логических элементах

И-НЕ. На

каждом входе запоминающей ячейки есть

дополнительная схема

совпадения (И-НЕ). Первые

входы их объединены, на них

подаются синхроимпульсы, на вторые

входы -информационные

сигналы. При С=0 – состояние

тригтера не меняется.

.42схема

тактируемого RS-триггера

на логических элементах

И-НЕ. На

каждом входе запоминающей ячейки есть

дополнительная схема

совпадения (И-НЕ). Первые

входы их объединены, на них

подаются синхроимпульсы, на вторые

входы -информационные

сигналы. При С=0 – состояние

тригтера не меняется.

62.D-триггер.

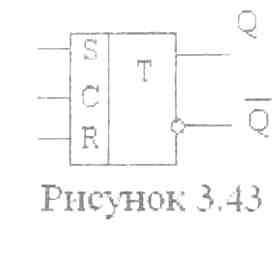

А синхронный

D-тригтер

имеет 1 вход и 2 выхода, осуществляет

задержку

сигнала. информация на выходе

равна информации на входе на предыдущем

такте.В

тактируемых триг момент принятия

информации определяется тактовым

сигналом С.

Для правильной

работы D-триггера

должен быть интервал времени после

прихода информации на вход D

перед приходом синхросигнала С. 2

входа: D

- информационный,

С-тактируемый

3.45. При С=1 записывается в триггер то,

что было подано на вход В до подачи

синхросигнала С.В DV

-триггере

при V=1

работает как

Д, при V=0-

сохраняется информация.

синхронный

D-тригтер

имеет 1 вход и 2 выхода, осуществляет

задержку

сигнала. информация на выходе

равна информации на входе на предыдущем

такте.В

тактируемых триг момент принятия

информации определяется тактовым

сигналом С.

Для правильной

работы D-триггера

должен быть интервал времени после

прихода информации на вход D

перед приходом синхросигнала С. 2

входа: D

- информационный,

С-тактируемый

3.45. При С=1 записывается в триггер то,

что было подано на вход В до подачи

синхросигнала С.В DV

-триггере

при V=1

работает как

Д, при V=0-

сохраняется информация.

63.Т-триггер

И![]() меет

1 информационный вход Т

и переключается,

когда на вход триггера

поступает сигнал. Из

характеристического уравнения Qn+1=

с чертой ТQ+Tс

чертQ

видно, что триггер производит

сложение по модулю 2. Частота

на выходе в 2 раза меньше, чем на входе.

Поэтому

можно использовать триггер как делитель

на два и для построения счетчиков.

меет

1 информационный вход Т

и переключается,

когда на вход триггера

поступает сигнал. Из

характеристического уравнения Qn+1=

с чертой ТQ+Tс

чертQ

видно, что триггер производит

сложение по модулю 2. Частота

на выходе в 2 раза меньше, чем на входе.

Поэтому

можно использовать триггер как делитель

на два и для построения счетчиков.

64.JK-триггер имеет 3 входа:JKC.Но одноступенчатый триггер работает не надежно, т.к. запоминающая ячейка – служит одвременно источником информ(с него поступает сигнал старого состояния) и приемником(переключ в новое сост и стирает старое). Одновременное выполнение 2 операций невозможно.Поэтому исп 2-ступенчатые триггеры.