- •1.Электропроводность полу проводников.

- •3.Прямое и обратное смещение р-п перехода.

- •4.Вольтамперная характеристика.

- •5.Основные параметры р-п перехода.

- •6.Пробой р-п перехода.

- •7.Методы изготовления р-п перехода.

- •8.Выпрямительный диод.

- •10.Варикап.

- •11.Туннельный диод. Обращенный диод.

- •12.Контакт металл-полупроводник. Диод Шоттки.

- •13.Классификация транзисторов.

- •14.Устройство биполярного транзистора.

- •15.Принцип действия транзистора.

- •16.Токи в транзисторе.

- •18.Схемы включения транзистора с об, оэ, ок.

- •19.Основные параметры транзисторов: а) физические б) һ-параметры.

- •20.Основные характеристики транзисторов, таблица основных параметров.

- •21.Характеристики с оэ (входные, выходные, прямой передачи тока).

- •22.Униполярные транзисторы с управляющим р-n переходом.

- •23.Униполярные транзисторы с изолированным затвором.

- •24.Тиристор, динистор.

- •27.Фотодиод, вах.

- •29.Классификация интегральных схем.

- •30.Усилители. Структурная схема. Классификация.

- •39.Дифференциальный усилитель с генератором стабильного тока (ду с гст)

- •40.Дифференциальный усилнтель с динамической нагрузкой (с зеркалом токов).

- •32.Однокаскадный усилитель.

- •41.Операционный усилитель, общие сведения.

- •42.Операционный усилитель, основные параметры.

- •43.Операционный усилитель, струкгурная и принципиальная схемы.

- •44.Основные логические операции и логические элементы.

- •45Анализ и синтез клс.

- •46Минимизация логических функций.

- •47. Схема ттл транзисторно-транзисторной логики с простым инвертом.

- •48Схема эсл эмитгерно-связанной логики.

- •49 Переключатель тока.

- •55.Схема и - не на мдп и кмдп.

- •56.Мультиплексор

- •57.Демультиплексор.

- •58.Дешифратор.

- •59.Шифратор.

- •60.Триггеры, классификация.

- •65.Регистр хранения.

- •6 6.Регистр сдвига.

- •67. Счетчики суммирующие.

- •68.Счетчики вычитающие.

- •69. Десятичный счетчик.

- •70.Операционный усилитель, внешние цепи.

- •71.0Перационный усилитель с отрицательной обратной связью.

- •79.Тригтер Шмита

- •80.Генераторы сигналов, условия самовозбуждения генератора.

- •82.Мультивибратор.

- •83.Генератор линейно-изменяющегося напряжения.

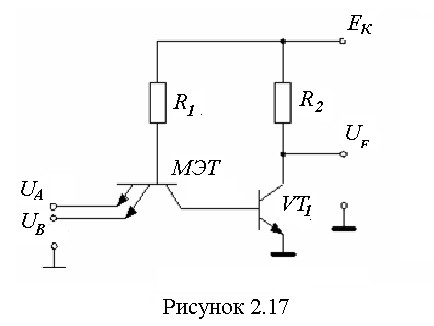

47. Схема ттл транзисторно-транзисторной логики с простым инвертом.

Т ТЛ

(2.17) ‑ результат развития

ДТЛ. Матрица

диодов заменяется многоэмиттерным

транзистором (МЭТ).

ТЛ

(2.17) ‑ результат развития

ДТЛ. Матрица

диодов заменяется многоэмиттерным

транзистором (МЭТ).

Это интегральный прибор, объединяющий функции диодных логических схем и транзисторного усилителя. ТТЛ относится к потенциальным элементам, выполняет логическую операцию И-НЕ. При низком уровне сигнала (логический 0) хотя бы на одном из входов МЭТ последний находится в состоянии насыщения, а VT1 закрыт. На выходе схемы присутствует высокий уровень напряжения (логическая 1). При высоком уровне сигнала на всех входах МЭТ работает в активном инверсном режиме (эмиттерный переход смещен в обратном направлении, а коллекторный – в прямом), VT1 находится в состоянии насыщения. На выходе схемы низкий уровень сигнала, т.е. ноль.

48Схема эсл эмитгерно-связанной логики.

49 Переключатель тока.

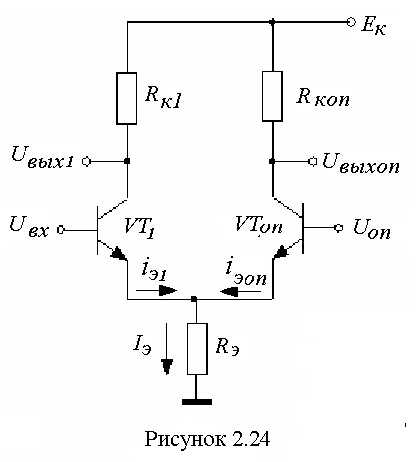

О собенность

ЭСЛ

- схема логического элемента строится

на основе интегрального

дифференциального усилителя (ДУ)

в ключевом режиме,

выполненный на двух транзисторах (2.24),

кот могут

переключать

ток и никогда

не входят в режим насыщения. Функционально

схема ЭСЛ состоит из трех узлов: а)

токового переключателя

б) источника опорного напряжения в)

выходных эмиттерных повторителей,ускоряющие

процесс заряда емкости нагрузки,Rвых

мало, Iвых

большой. Парафазный выход позволяет

снимать прямые и инверстные значения,

умен число микросхем. Можно объединить

выходы элементов для расширения

возможностей.

собенность

ЭСЛ

- схема логического элемента строится

на основе интегрального

дифференциального усилителя (ДУ)

в ключевом режиме,

выполненный на двух транзисторах (2.24),

кот могут

переключать

ток и никогда

не входят в режим насыщения. Функционально

схема ЭСЛ состоит из трех узлов: а)

токового переключателя

б) источника опорного напряжения в)

выходных эмиттерных повторителей,ускоряющие

процесс заряда емкости нагрузки,Rвых

мало, Iвых

большой. Парафазный выход позволяет

снимать прямые и инверстные значения,

умен число микросхем. Можно объединить

выходы элементов для расширения

возможностей.

Условное

обозначение ЭСЛ имеет вид

![]()

50Логические элементы на МДП. См51,54,55

51Схема НЕ – на МДП с линейной нагрузкой.

52Схема НЕ – на МДП с нелинейной нагрузкой.

Т![]() ранзистор

VT1

работает в ключевом режиме,

VT2

– всегда в активном. VT2

является нелинейной

нагрузкой.

При подаче на вход х

0 VT1

запирается, VT2

близок к насыщению, на выходе 1. При

подаче на вход х

1 VT1

отпирается, VT2

близок к отсечке, на выходе 0. Выполняется

операция

ранзистор

VT1

работает в ключевом режиме,

VT2

– всегда в активном. VT2

является нелинейной

нагрузкой.

При подаче на вход х

0 VT1

запирается, VT2

близок к насыщению, на выходе 1. При

подаче на вход х

1 VT1

отпирается, VT2

близок к отсечке, на выходе 0. Выполняется

операция

;

;

53Схема НЕ на КМДП.

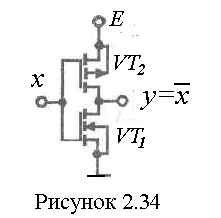

О снова-

каскад на двух соединенных

стоками МДП-транзисторах

VT1

и

VT2

(2.34)

с

различными типами проводимости.

Для КМДП

принято, чтобы единица отображалась

высоким уровнем, а ноль – низким. При

подаче на вход 1

транзистор VT1

открывается,

а транзистор VT2

снова-

каскад на двух соединенных

стоками МДП-транзисторах

VT1

и

VT2

(2.34)

с

различными типами проводимости.

Для КМДП

принято, чтобы единица отображалась

высоким уровнем, а ноль – низким. При

подаче на вход 1

транзистор VT1

открывается,

а транзистор VT2

закрывается.

На

выходе 0.

При подаче на вход 0 транзистор

VT1

закрыт,

а транзистор VT2

открыт.

на выходе каскада —1.

закрывается.

На

выходе 0.

При подаче на вход 0 транзистор

VT1

закрыт,

а транзистор VT2

открыт.

на выходе каскада —1.

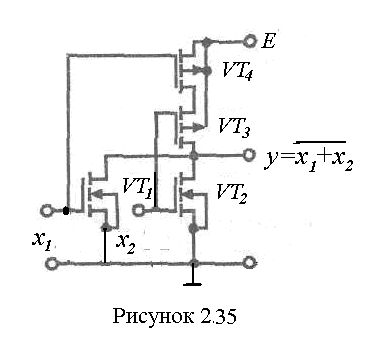

54.Схема ИЛИ - НЕ на МДП и КМДП.

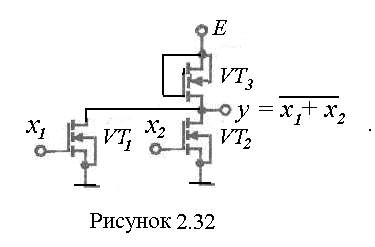

в

двухвходовой схеме ИЛИ-НЕ на МДП ( 2.32)

входные транзисторы VT1

и VT2

соединены параллельно. Если хотя бы на

один из входов подана 1, соответствующий

транзистор отпирается, и на выходе схемы

будет 0. И только при подаче на все входы

схемы 0 транзисторы VT1

и VT2

запрутся, и на выходе появится 1. *Схема

ИЛИ-НЕ на КМДП 2.35.

Если на оба входа поданы 0,

то транзисторы VT3

и VT4

будут открыты,

так как имеют канал

с проводимостью р-типа, а транзисторы

VT1

и

VT2

—

закрыты,

так как имеют канал с проводимостью

n-типа.

Установится 1.

При подаче 1 хотя бы

на один из входов соответствующий

транзистор VT3

или

VT4

закроется,

а транзистор VT1

или

VT2

соответственно

откроется. На выходе 0.

двухвходовой схеме ИЛИ-НЕ на МДП ( 2.32)

входные транзисторы VT1

и VT2

соединены параллельно. Если хотя бы на

один из входов подана 1, соответствующий

транзистор отпирается, и на выходе схемы

будет 0. И только при подаче на все входы

схемы 0 транзисторы VT1

и VT2

запрутся, и на выходе появится 1. *Схема

ИЛИ-НЕ на КМДП 2.35.

Если на оба входа поданы 0,

то транзисторы VT3

и VT4

будут открыты,

так как имеют канал

с проводимостью р-типа, а транзисторы

VT1

и

VT2

—

закрыты,

так как имеют канал с проводимостью

n-типа.

Установится 1.

При подаче 1 хотя бы

на один из входов соответствующий

транзистор VT3

или

VT4

закроется,

а транзистор VT1

или

VT2

соответственно

откроется. На выходе 0.