- •1. Постановка задачі

- •2. Дослідження роботи арифметично- логічного пристрою

- •2.1 Теоретичні відомості про арифметично-логічні пристрої

- •2.2 Дослідження роботи стандартного 4-бітного арифметично-логічного пристрою

- •3. Синтез спеціалізованого арифметичного пристрою

- •3.1 Теоретичні відомості про суматори

- •3.6 Синтез арифметичної функції

- •4. Синтез логічного спеціалізованого пристрою

- •5. Тестування спеціалізованого арифметично – логічного пристрою.

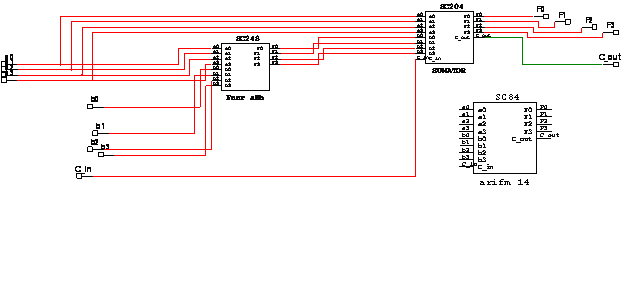

3.6 Синтез арифметичної функції

Рис 18 Субсхема і субблок арифметичної функції F14= A плюс (А+В)

3.7 Тестування спеціалізованого арифметичного пристрою

Таблиця 3 Результати тестування спеціалізованого арифметичного пристрою

Операція |

Код операції |

Тип М |

А |

В |

Код генератора |

Результат моделювання |

|||||||

F |

|||||||||||||

|

A мінус 1 |

2 |

0 |

6 |

7 |

000D6007 |

F |

||||||

|

A мінус 1 |

2 |

0 |

D |

6 |

400DD376 |

1 |

||||||

|

А мінус В мінус 1 |

6 |

0 |

6 |

7 |

10096937 |

2 |

||||||

|

А мінус В мінус 1 |

6 |

0 |

D |

6 |

5009D356 |

9 |

||||||

|

A плюс (А+В) |

A |

0 |

6 |

7 |

20056987 |

9 |

||||||

|

A плюс (А+В) |

A |

0 |

D |

6 |

6005D026 |

4 |

||||||

|

A плюс A |

E |

0 |

6 |

7 |

30016147 |

8 |

||||||

|

A плюс A |

E |

0 |

D |

6 |

7001D006 |

b |

||||||

|

|||||||||||||

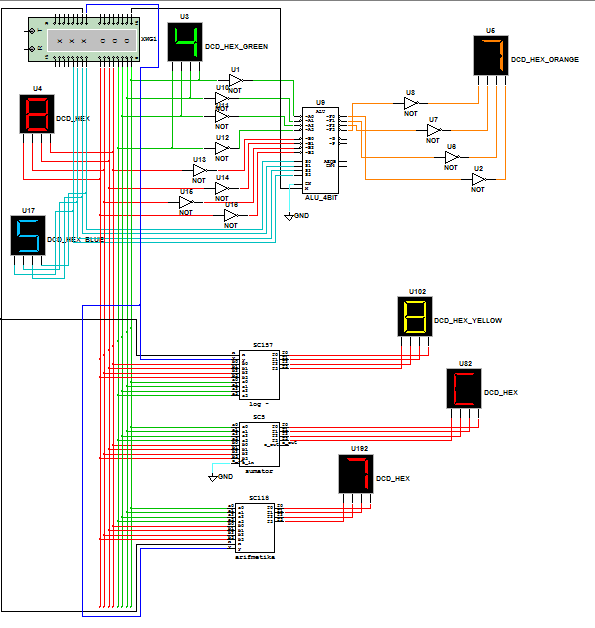

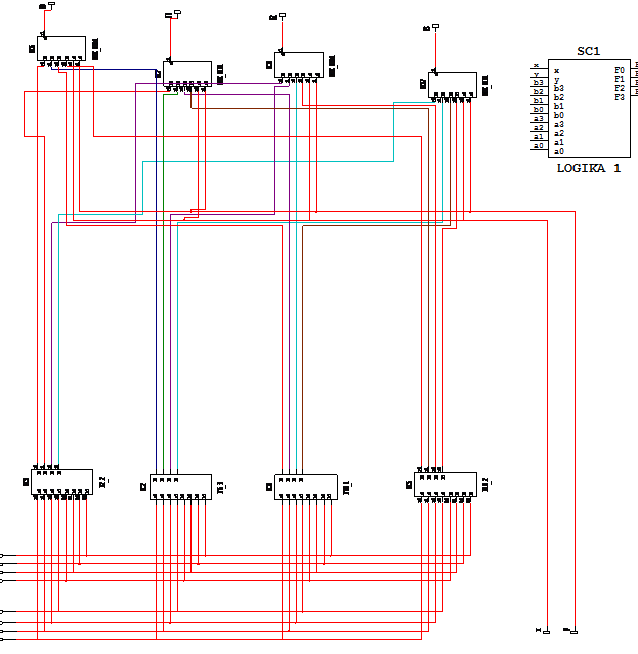

Рис 19 Функціональна схема арифметичного пристрою

4. Синтез логічного спеціалізованого пристрою

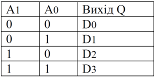

4.1 Теоретичні відомості про мультиплекс ори

Мультиплексор призначений для комутації в певному порядку на один вихід одного з декількох вхідних сигналів, в залежності від стану адресних входів. За допомогою мультиплексора здійснюється часове розділення інформації, що надходить по різним каналам. Мультиплексор можна порівняти з безконтактним багатопозиційним перемикачем. Мультиплексор має один або два взаємодоповнюючі виходи (прямий і інвертований) і дві групи входів: – інформаційні; – керуючі (адресні і дозволяючі). Якщо мультиплексор має n адресних входів, то кількість інформаційних входів буде 2n . Набір сигналів на адресних входах визначає конкретний інформаційний вхід, який буде з’єднаний з виходом мультиплексора. Дозволяючий (стробуючий) вхід керує одночасно всіма інформаційними входами незалежно від стану адресних входів. Заборонений сигнал на цьому вході блокує роботу всього пристрою. Наявність дозволяючого входу розширює функціональні можливості мультиплексора, дозволяє синхронізувати його роботу з роботою інших вузлів. Дозволяючий вхід використовується також для нарощування розрядності мультиплексора. Адресні входи мультиплексора позначимо літерами Ai {0, 1} ∈ , а інформаційні входи Di {0,1} ∈ (Рис ). Складаємо таблицю істинності мультиплексора 4:1

Q = ∧ ∧ D0 ∨ ∧ A0 ∧ D1 ∨ A1 ∧ ∧ D2 ∨ A1 ∧ A0 ∧ D3

Робота мультиплексора 4:1 описується логічним рівнянням, складеним на основі таблиці істинності.

Рис 20 Субсхема та субблок мультиплексора 4х1

4.2 Логічна функція: F2= A*

Рис 21 Схема логічної функції A*

Рис 22 Субсхема 4-х розрядної логічної функції F2= A*

Синтез Функції F2 відбувається завдяки множенню елементу a*.

Об’єднання чотирьох таких функції утворює субблок F2_2 .

4.3 Логічна функція: F6=(A*)+(*В)

Рис 23 Субсхема однорозрядної логічної функції : F6=(A*)+(*В)

Рис 24Субсхема та субблок 4-х розрядної логічної: F6=(A*)+(*В)

4.4 Логічна функція: F10= *

Рис 25 Субсхема логічної функції F3

Рис 26 Субсхема і субблок 4-х розрядної логічної F10

Даний субблок будується на основі під’єднання до 1 множника прямого (а) і інвертного сигнала (b), а до другого множника обидва інвертних сигнали.

4.5 Логічна функція: F4=(*)

Рис 27 Субсхема логічної функції

Рис 28 Субсхема 4-х розрядної логічної F14 та субблок

4.6 Тестування спеціалізованого логічного пристою

Таблиця 4 Результати дослідження спеціалізованого логічного пристрою

Операція |

Код операції |

Тип М |

А |

В |

Код генератора |

Результат моделювання |

|||||||

F |

|||||||||||||

1 |

*В |

D |

1 |

6 |

7 |

010D6007 |

0 |

||||||

2 |

*В |

D |

1 |

D |

6 |

410DD376 |

9 |

||||||

3 |

(*В)+( А+) |

9 |

1 |

6 |

7 |

11096937 |

1 |

||||||

4 |

(*В)+( А+) |

9 |

1 |

D |

6 |

5109D356 |

B |

||||||

5 |

|

5 |

1 |

6 |

7 |

21056987 |

8 |

||||||

6 |

|

5 |

1 |

D |

6 |

6105D026 |

9 |

||||||

7 |

(*) |

1 |

1 |

6 |

7 |

31016147 |

9 |

||||||

8 |

(*) |

1 |

1 |

D |

6 |

7101D006 |

B |

||||||

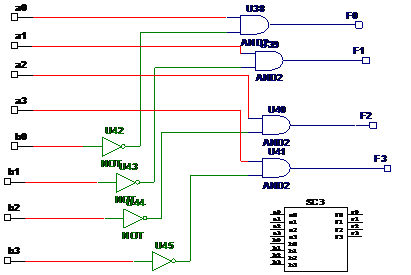

Рис29 Логічна субсхема і субблок з блоком мультиплексорів