- •Лекція №1 Основні положення задачі курсу

- •Лекція №2 Характеристика напівпровідників

- •Приєднання кристала до основи корпусу

- •Лекція №8 Гібридні інтегральні мікросхеми План

- •Загальні вимоги до логічних імс

- •Десятична система числення

- •Двійкова система численя

- •Література: с.В. Симонович и др. Информатика. Базовый курс. – сПб: Питер, 2005 – 640 с.

- •Відправлення сигналів

- •Обробка сигналів

- •Лекція №20 Дослідження роботи регістрів План

- •Призначення виводів

- •Лекція №17

- •Лекція №23 Взаємодія вузлів пеом-80

- •Література:

- •Лекція №24 Характеристика вузлів пеом-80

- •Література:

- •Загальна лекція

- •2. Однопрограмний і мультипрограмний режими керування

- •3. Сторінкова організація пам’яті

- •4. Використання віртуальної пам’яті в ос Windows та ос Unix

- •Лекція №25 Характеристика мікропроцесора к1810вм86

Лекція №20 Дослідження роботи регістрів План

Призначення та види регістрів

Регістр на RS тригера

Здвигуючий регістр

Призначення та види регістрів

При виконанні різних арефметичних операцій, а також в схемах рівняння виникає необхідність зберігати код числа в продовж часу, здвигати цей код вліво, вправо, виконувати розрахунок числа, імпульсов, перетворювати код числа в зворотній та навпаки. Ці операції виконують регістри.

Регістром наз. функціональний прилад призначений для тимчасового зберігання двійкової інформації.

В залежності від призначення регістри діляться:

Накопичувальні - для вводу, зберігання і виводу двійкової інформаії. Числа в регістр можуть поступать в аралельному двійковому коді або в парафазному 2-му коді. Ввід інформації може виконуватися як в одинакових так і в різних кодах.

Здвигаючі – для ввода, зберігання і вивода 2-их чисел, а також для їх здвигу, причому вибор може бути організований як вправо, так і вліво; ввод чисел у здвигаючому регістрі може бути виконаний як у паралельному, так і в послідовному коді.

Регістри перетворювачі – працюють з 2-ю інформацією в паралельному і послідовнму коді, виконують помимо операцій ввода, вивід, зберігання, здвиг, ряд логічних операцій. З допомогою цих регістрів можно перетворити паралельний код числа в послідовний і навпаки.

Основу регістрів складають тригери та комбінаціонні логічні елементи.

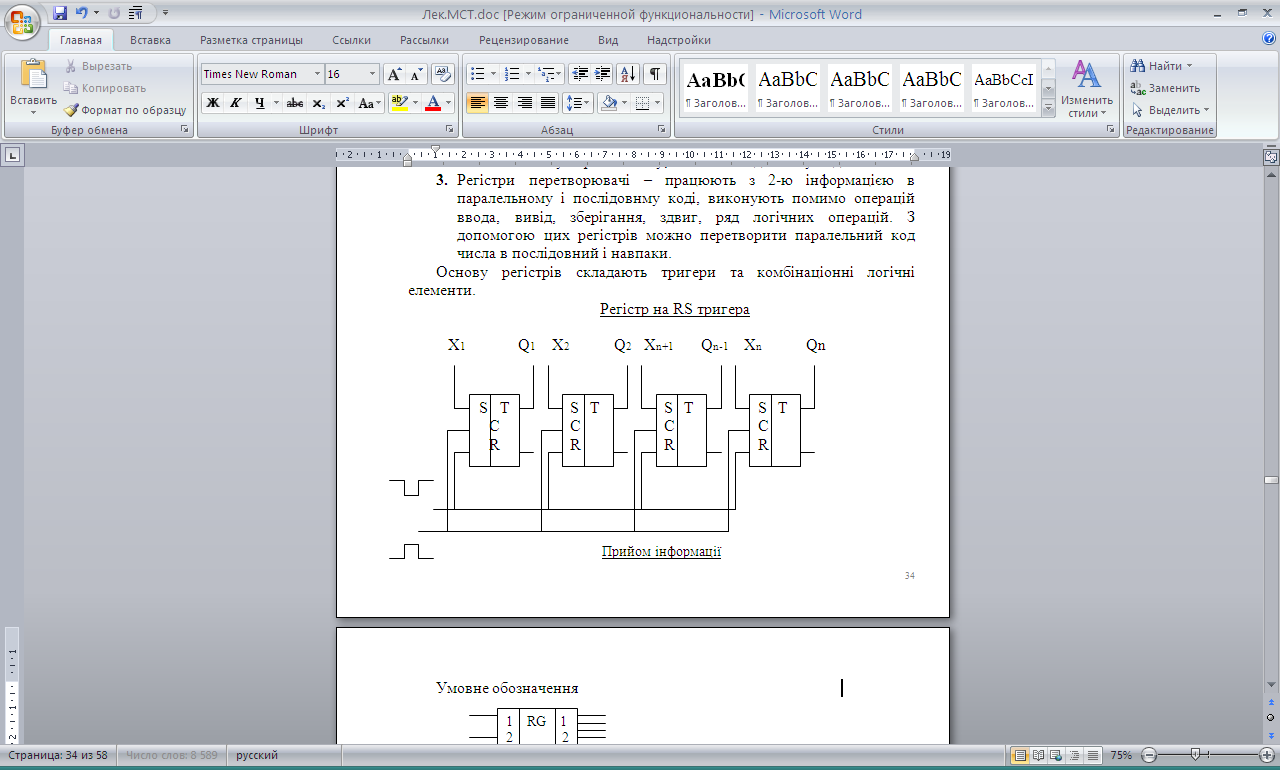

Регістр на RS тригерові

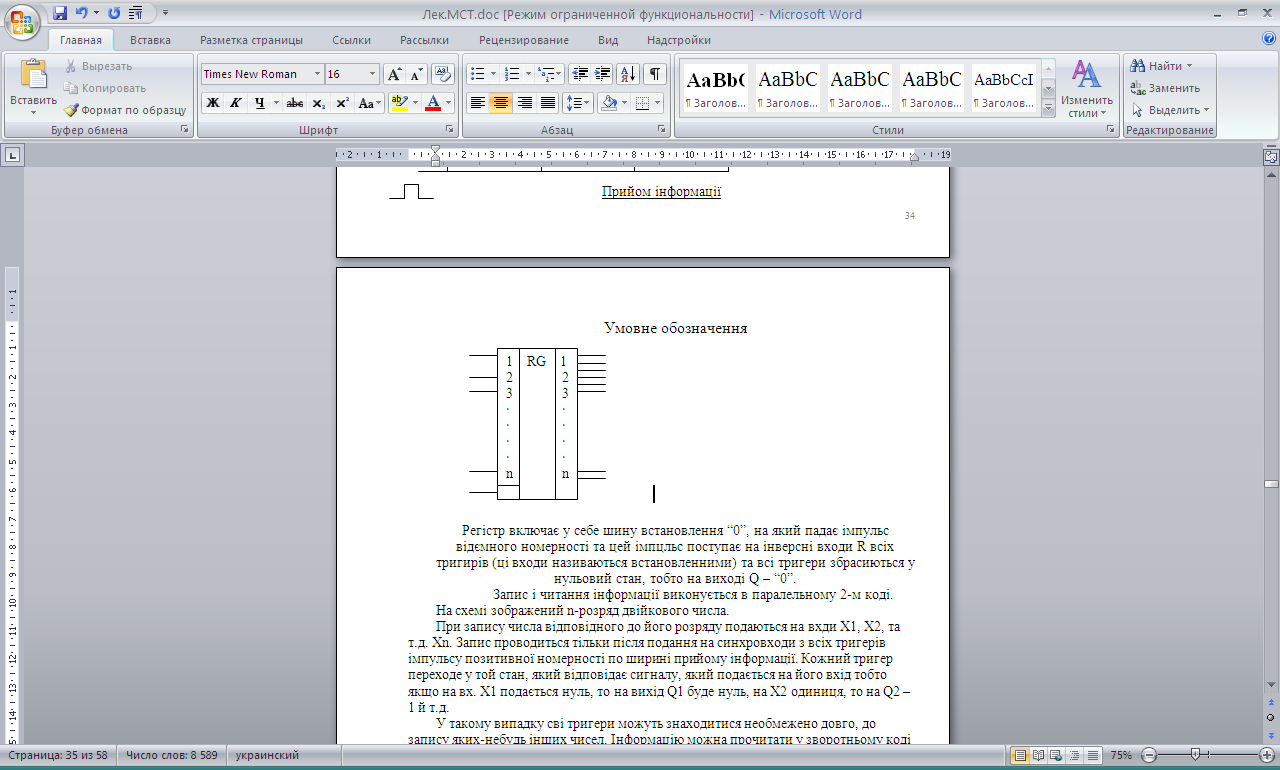

Умовне позначення

Регістр включає у себе шину встановлення “0”, на який падає імпульс відємного номерності та цей імпцльс поступає на інверсні входи R всіх тригирів (ці входи називаються встановленними) та всі тригери збрасиються у нульовий стан, тобто на виході Q – “0”. Запис і читання інформації виконується в паралельному 2-м коді.

На схемі зображений n-розряд двійкового числа.

При запису числа відповідного до його розряду подаються на вхди Х1, Х2, та т.д. Хn. Запис проводиться тільки після подання на синхровходи з всіх тригерів імпульсу позитивної номерності по ширині прийому інформації. Кожний тригер переходе у той стан, який відповідає сигналу, який подається на його вхід тобто якщо на вх. Х1 подається нуль, то на вихід Q1 буде нуль, на Х2 одиниця, то на Q2 – 1 й т.д.

У такому випадку сві тригери можуть знаходитися необмежено довго, до запису яких-небудь інших чисел. Інформацію можна прочитати у зворотньому коді з інверсних виходів всіх тригерів.

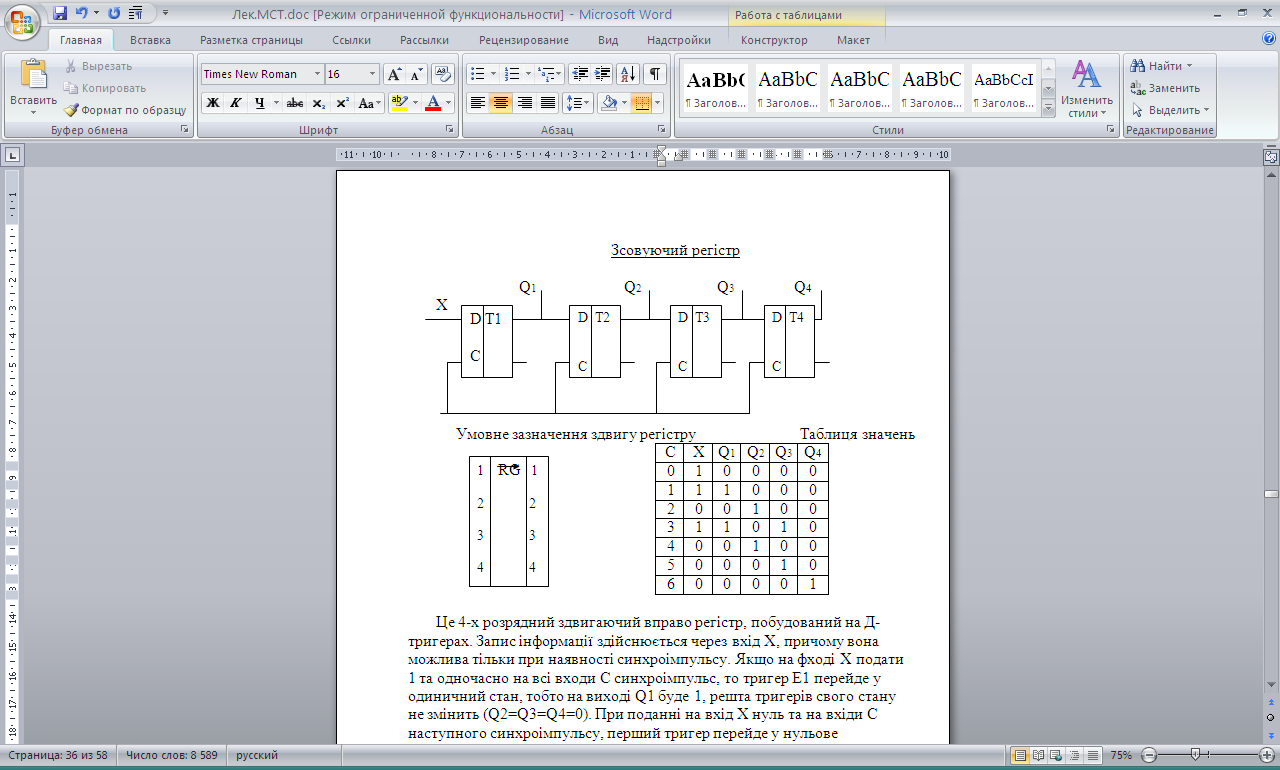

Здвигуючий регістр

У

1 RG

1

2 2

3 3

4

4 мовне

зазначення здвигу регістру

Таблиця значень

мовне

зазначення здвигу регістру

Таблиця значень

-

C

X

Q1

Q2

Q3

Q4

0

01

0

0

0

0

1

1

1

0

0

0

2

0

0

1

0

0

3

1

1

0

1

0

4

0

0

1

0

0

5

0

0

0

1

0

6

0

0

0

0

1

Це 4-х розрядний здвигаючий вправо регістр, побудований на Д-тригерах. Запис інформації здійснюється через вхід Х, причому вона можлива тільки при наявності синхроімпульсу. Якщо на фході Х подати 1 та одночасно на всі входи С синхроімпульс, то тригер Е1 перейде у одиничний стан, тобто на виході Q1 буде 1, решта тригерів свого стану не змінить (Q2=Q3=Q4=0). При поданні на вхід Х нуль та на вхіди С наступного синхроімпульсу, перший тригер перейде у нульове положення, Т2 – в одиничне, а Т3 та Тт – не змінить свого стану.

При переданні наступного синхроімпульсу С та одиниці на вход Х, Т1 - “1”; Т2 - “0”; Т3 – “1”, Т4 – не змінить свого стану.

Т.О. кожний синхроімпульс буде здійснювати здвиг двійкового коду вправо, який подається на вход Х. Цей двійковий код можна прочитати з виходу Q4.

Питання:

Що таке регістр?

Які є види регістрів?

Приведіть схему RS тригера?

Література:

Будыщев М. С. Електротехніка, електроніка та мікропроцесорна техніка. Підручник. – Львів: Афіша, 2001. – 424с.

Лекція №6

Класифікація запам’ятовувальних пристроїв(ср)

План

Типи запам‘ятовувальних пристроїв

Зовнішня пам‘ять

Ієрархічний принцип побудови пам’яті ЕОМ

У сучасній ПЕОМ машині пам'ять, поза всяких сумнівів, посідає друге за важливістю місце після процесору. Параметри оперативної пам'яті у значній мірі визначають ефективність виконання різноманітних задач. Підвищення технічних та експлуатаційних характеристик сучасних МПС (особливо їх можливостей що до розв'язання складних задач, які потребують обробки великих масивів інформації) перш за все пов'язано з підвищенням ємності та швидкодії ЗП. Адже не достатньо тільки мати потужну та швидкодіючу пам'ять; не менш важливим є створення "сприятливих умов" для максимального використання її потенційних можливостей.

Для пам’яті сучасних ПК характерний ієрархічний принцип побудови. Тобто, у складі підсистеми пам’яті повинні бути ЗП, яки виконують різні функції та побудовані на основі різних принципів, тому що вимоги до пристроїв пам’яті дуже суперечливі та не можуть бути виконані у єдиному пристрої.

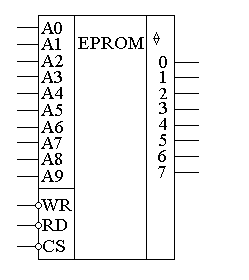

За виконуваними функціями розрізняють такі типи ЗП:

- оперативні запам'ятовуючі пристрої (ОЗП, RAM – Random Access Memory);

- постійні запам'ятовуючі пристрої (ПЗП, ROM – Read Only Memory);

- зовнішні запам'ятовуючі пристрої (ЗЗП) або накопичувачі інформації.

Оперативний запам'ятовуючий пристрій -- це пам'ять комп'ютера, призначена для зберігання даних, адрес та програм, які використовує комп'ютер в даний момент часу. У комп'ютері ОЗП використовують як для зберігання програм і даних користувача, так і для зберігання системних програм і даних, які забезпечують власне функціонування самої обчислювальної машини. Сукупність останніх отримала назву операційної системи.

Постійні запам'ятовуючі пристрої призначені для зберігання певної одноразово записаної до них інформації, яка має зберігатися навіть за умов знеструмлення комп'ютеру. Такою інформацією є базові системні дані і програми, потрібні для завантаження операційної системи та керування роботою зовнішніх пристроїв комп'ютеру. Таким чином, постійний запам'ятовуючий пристрій -- це пам'ять комп'ютера, призначена для зберігання службових програм і даних, які не можуть бути змінені у процесі його роботи.

Зовнішня пам'ять може розглядатися як архівна пам'ять, призначена для довготермінового зберігання великих масивів інформації.

Підсумовуючи вищесказане, взаємодію типів ЗП можна зобразити схемою, що подана на рис.1.

За способом доступу до інформації розрізняють такі типи ЗП:

1. ЗП з довільним доступом до інформації;

2. ЗП з прямим доступом до інформації;

3. ЗП з послідовним доступом до інформації.

Довільний доступ до інформації передбачає можливість прямого безпосереднього звернення до будь-якої комірки пам'яті не залежно від місця її розташування у ЗП. Треба також зазначити, що при цьому час, потрібний для такого звернення теж не залежить від місця розташування відповідної комірки у масиві пам'яті.

Рис. 1. Ієрархічний принцип побудови пам’яті ЕОМ.

Прямий доступ до інформації передбачає можливість також прямого безпосереднього звернення до будь-якої масиву (кластера) пам'яті не залежно від місця її розташування у ЗП.

Але ж час, потрібний для такого звернення залежить від місця розташування відповідного кластера у масиві пам'яті.

Послідовний доступ передбачає можливість звернення до комірок пам'яті тільки у порядку черги, тобто для запису чи читання будь-якої комірки треба перш за все "перегорнути" усі попередні комірки. Таку систему звернення можна порівняти із способом отримання доступу до певного запису на магнітофонній касеті. Перш ніж отримати його, треба перемотати касету до потрібного місця. Звичайно у цьому випадку неминучі великі витрати часу, тому такий метод доцільно застосовувати лише для архівних пристроїв зберігання даних на магнітній стрічці, які отримали назву стримерів.

За типом носіїв інформації розрізняють: напівпровідникові, магнітні та оптичні ЗП.

Напівпровідникові ЗП, побудовані з використанням біполярних та МОН (Метал-Окис-Напівпровідник) - транзисторів, використовують для реалізації швидкодіючої оперативної пам'яті, до якої висуваються досить високі вимоги. Ці пристрої використовують властивість деяких електронних пристроїв необмежений час знаходитись у одному з двох стійких станів ("0" або "1") або зберігати певний електричний заряд, як ознаку запису у ЗП одного біту інформації. Постійні ЗП також напівпровідникові.

Магнітні ЗП використовують властивість тонких плівок, виготовлених з феросплаву на основі оксиду хрому, або кобальту (раніше використовувався оксид заліза) довгий час зберігати остаточну намагніченість після впливу на них магнітним полем. Невелика область магнітної поверхні (домен) під впливом магнітного поля впорядковує свої елементарні вектори намагнічування, що розглядається як запис одного біту інформації. До таких пристроїв найбільш важливою є велика інформаційна ємність та низька вартість зберігання одиниці інформації. Найбільшого розповсюдження набули накопичувачі на магнітних дисках (гнучких та жорстких) та магнітних стрічках.

Оптичні ЗП, або пристрої пам'яті на лазерних дисках використовують властивість фоточутливого шару, нанесеного на пластикову поверхню диску, змінювати колір або форму під впливом сильно сфокусованого лазерного променя. Наявність у цьому шарі, захищеному зверху шаром лаку, мікрозаглиблення або мікрокрапки іншого кольору після її експозиції променем лазеру, сприймається як запис одного біту інформації. У порівнянні з магнітними носіями інформації, лазерні диски є більш надійними і можуть зберігатися набагато довше.

Класифікація ЗП за способом доступу до інформації та типом носія зображена на рис.2.

Рис. 2. Класифікація пристроїв пам’яті за способом доступа до інформації та типом носія .

Основними показниками ЗП є:

Обсяг пам'яті пристрою, який характеризує його здатність зберігати велику кількість програм і даних.

Розрядність пам'яті, яка визначає діапазон чисел, розміщених у комірках. Найбільш розповсюджена на даний момент розрядність -- 64 та 128. Цей показник тісно пов'язаний з розрядністю шини даних процесору, адже саме по цій шині інформація з пам'яті надходитиме до нього на обробку.

Швидкодія пам'яті, яка характеризує витрати часу на занесення даних до неї (запис) та на отримання їх назад (читання). Діапазон цього показника досить широкий: від кількох мілісекунд для накопичувачів на жорстких дисках і до наносекунд для сучасних ОЗП.

Енергоспоживання та геометричні розміри визначають ефективність використання того чи іншого типу пам'яті у конкретному обчислювальному пристрої. Особливо гостро стоїть проблема зниження розмірів та споживаної електроенергії для портативних переносних комп'ютерів, які мають працювати у автономному режимі 4-5 годин.

Питання:

Які є типи запам‘ятовувальних пристроїв?

Що таке зовнішня пам‘ять?

За способом доступу до інформації на які типи діляться ЗП?

Література:

1.Мікропроцесорна техніка: Підручник/ Ю.І. Якименко та інш. – К.: ІВЦ Політехніка; Кондор, 2004. с. 187-189, 217-235.

2. Угрюмов Е.П. Цифровая схемотехніка. – СПб.: БХВ-Петербург, 2002. с. 175-187, 221-245.

Лекція №7

Оперативні запам’ятовувальні пристрої різних типів(ср)

План

Оперативні запам’ятовувальні пристрої статичного типу

Оперативні запам’ятовувальні пристрої динамічного типу

Оперативні запам’ятовувальні пристрої статичного типу

Статична пам'ять (Static RAM -- SRAM) отримала свою назву через те, що кожен занесений до неї біт інформації може знаходитись там необмежений час без будь-якого поновлення. Єдиною умовою збереження інформації у статичних ЗП є постійна наявність електроживлення мікросхем пам'яті, тому вони, як і усі інші типи оперативної пам'яті, відносяться до енергозалежних пристроїв. При зникненні напруги живлення, уся інформація, що знаходилась у комірці такого типу пам'яті буде стерта.

Основою побудови статичних ЗП є простіші RS-тригери, реалізовані не у ТТЛ технології (яка є дуже енерговитратною) а у МОН. Наявність бістабільного елементу дозволяє приймати та видавати дані на відповідні шини комп'ютеру у будь-який момент часу майже без затримки, тобто швидкодія таких ЗП є достатньо високою. Додаткова перевага статичних ОЗП полягає в тому, що при читанні інформація не руйнується, тобто не потрібно втрачати час на її відновлення на відміну від динамічних ОЗП.

Найбільш суттєвим недоліком таких ЗП є їх відносна складність у виготовленні, особливо коли мова йде про ЗП з великою інформаційною ємністю. Неважко підрахувати, що для виготовлення найпростішого тригеру потрібні принаймні два транзистори, декілька резисторів навантаження і хоча б два конденсатори (запам’ятовуючий елемент сучасної статичної пам’яті має принаймні шість транзисторів). Тому статичні ЗП у якості основного ОЗП не використовують. Але висока швидкодія цих ЗП дозволила використовувати їх у якості буферних пристроїв пам'яті. Головне завдання їх полягає у узгодженні між собою пристроїв ЕОМ, які мають суттєву різницю у швидкодії. До речі, пристрій пам'яті, які виконує таку функцію отримав назву кеш-пам'яті.

Схематичне зображення мікросхеми ОЗП інформаційною ємністю Nx8 ілюструє рис. 5. Такий ОЗП припускає читання/запис 8-розрядного коду. Для запису 0 або 1, що надходять на входи DIO7- DIO0, потрібно на адресні входи подати код адреси, а на входи CS і W/R відповідно сигнали дозволу і читання/запису (1/0). Подача пасивного рівня на вхід ОЕ переводить мікросхему у так званий високоімпедансний стан (третій стан), тобто відключає від інформаційного обміну по шині даних. Таким чином процесор може здійснити читання/запис інформації із статичного ОЗП за два такти, що і обумовлює високо швидкодію пам’яті цього типу ( цикл звертання -- одиниці нс).

Рис. 1. УГП восьмирозрядного ОЗП

Статичні ОЗП при невеликій інформаційній ємності будуються за структурою 2D, при великій -- 2DM )з використанням мультиплексора).

Оперативні запам’ятовувальні пристрої динамічного типу

Елементарна комірка динамічної пам'яті (Dynamic RAM – DRAM) складається з одного конденсатора і замикаючого транзистора. Це дає можливість досягти набагато більшої щільності розміщення елементів і, у результаті, значно знизити вартість ОЗП. З іншого боку, дана технологія має ряд недоліків, головним з який є те, що заряд, що накопичується на конденсаторі, згодом губиться. Незважаючи на те, що при конструюванні конденсаторів комірки динамічної пам'яті використовується гарний діелектрик з електричним опором декілька тераОм (1012 Ом), заряд конденсатора губиться дуже швидко, тому що розміри одного конденсатора мікроскопічні, а ємність мізерна (порядку 10-15 Ф). При такій ємності на такому конденсаторі накопичується усього близько 40000 електронів! Середній час витоку заряду при сучасному дизайні комірок динамічної пам'яті складає сотні навіть десятки мілісекунд. Виходить, заряд кожного осередку потрібно відновлювати протягом даного відрізка часу, інакше інформація, що зберігається в пам'яті, буде загублена.

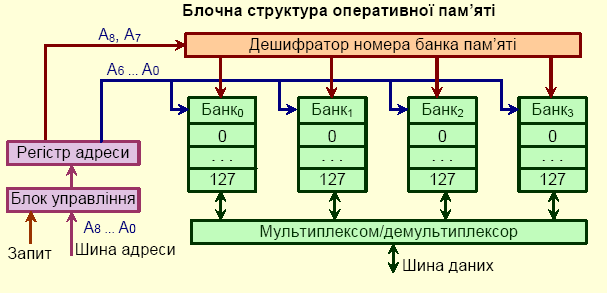

Рис. 2. Блочна структура організації ОЗП

ОЗП пройшли довгий путь еволюції, у ПЕОМ використовувалися модулі та мікросхеми пам’яті багатьох типів. В дійсний час найбільш розповсюджені пам'ять типів SDRAM (Synchronic DRAM – синхронний динамічний ОЗП), DDR (Double Data Rate – подвійна швидкість передавання даних) SDRAM, DDR2 SDRAM. Найбільш сучасний та швидкодіючий тип ОЗП -- DDR2 SDRAM

Питання:

Що таке статична пам'ять ?

Що таке динамічна пам'ять ?

Література:

Угрюмов Е.П. Цифровая схемотехніка. – СПб.: БХВ-Петербург, 2002. с. 175-187, 221-245.

Лекція №8

Дискретиза́ція , квантування и кодування сигналів(ср)

План

Дискретиза́ція

Квантування

Кодува́ння

Дискретиза́ція — перетворення функцій неперервних змінних у функції дискретних змінних, за якими початкові неперервні функції можуть бути відновлені із заданою точністю. Роль відліків виконують квантовані значення функцій. Під квантуванням розуміють перетворення неперервної за значеннями величини у величину з дискретною шкалою значень з скінченної множини дозволених, які називають рівнями квантування. Якщо рівні квантування нумеровані, то результатом перетворення є число, яке може бути виражене в будь-якій системі числення.

Для виробничих задач обробки даних зазвичай потрібно значно менше інформації, ніж її надходить від вимірювальних датчиків у вигляді безперервного аналогового сигналу. При статистичних флюктуаціях вимірюваних величин і кінцевої похибки засобів вимірювань інформація про величину сигналу завжди обмежена. Раціональне виконання дискретизації і квантування початкових даних дає можливість знизити витрати на зберігання і обробку інформації. Використання дискретних сигналів дозволяє застосовувати методи кодування інформації з можливістю подальшого виявлення і виправлення помилок при зверненні до збереженої інформації. Цифрова форма сигналів полегшує також уніфікацію операцій перетворення інформації на всіх етапах звернення до неї.

Квантування

В інформатиці під квантуванням (англ. quantization) неперервної або дискретної величини розуміють розбивку діапазону її значень на кінцеве число інтервалів. Існує також векторне квантування - розбивка простору можливих значень векторної величини на кінцеве число областей. Квантування часто використовується при обробці цифрових сигналів, у тому числі при стисканні звуку й зображень. Найпростішим видом квантування є розподіл цілочисельного значення на натуральне число, називане коефіцієнтом квантування.

Не слід плутати квантування з дискретизацією (і, відповідно, рівень квантування з частотою дискретизації). При дискретизації величина, що змінюється в часі (сигнал) заміряється із заданою частотою (частотою дискретизації), таким чином, дискретизація розбиває сигнал за часовою складовою (на графіку - по горизонталі). Квантування ж приводить сигнал до заданих значень, тобто, розбиває за рівнем сигналу (на графіку - по вертикалі). Сигнал, до якого застосована дискретизація й квантування, називається цифровим.

При оцифровці сигналу рівень квантування називають також глибиною дискретизації або розрядністю. Глибина дискретизації виміряється в бітах і позначає кількість біт, що виражають амплітуду сигналу. Чим більше глибина дискретизації, тим точніше цифровий сигнал відповідає аналоговому.

Кодува́ння (рос. кодирование, англ. encoding, нім. Kodieren n) — 1. Ототожнювання символів чи груп символів одного коду з символами чи групами символів іншого коду або обробка певної інформації через знакову систему певного коду.

Ефективне кодування — кодування, яке передбачає усунення надлишковості інформації.

Завадостійке кодування — кодування, яке характеризується підвищенням вірогідності передачі інформації без помилок.

Кодування інформації — перетворення будь-якої інформації в кодові комбінації для передачі, зберігання і т. ін.

Кодування (криптографія) — шифрування повідомлення (сигналу) за допомогою коду.

Питання:

Що таке дискретизація, в чому полягає?

Що таке квантування, в чому полягає?

Що таке кодування, в чому полягає?

Література:

Угрюмов Е.П. Цифровая схемотехніка. – СПб.: БХВ-Петербург, 2002. с. 175-187, 221-245.

Лекція №9

Класифікація мікропроцесорів(ср)

План

Класифікація МП за функціональним призначенням

Класифікація МП за числом ВІС, використовуваних для побудови функціонально повного МП

Класифікація МП за розрядністю оброблюваних кодових слів даних

1. За функціональним призначенням розрізняють універсальні і спеціалізовані МП.

Універсальні МП мають алгоритмічно універсальний набір команд, за допомогою якого можна здійснювати перетворення інформації відповідно до будь-якого заданого алгоритму. Продуктивність (швидкодія) таких процесорів практично не залежить від специфіки розв'язуваних задач.

Спеціалізовані МП призначені для рішення обмеженого і строго визначеного кола задач, іноді навіть для рішення однієї конкретної задачі. До спеціалізованих МП належать: сигнальні; медійні та мультимедійні; трансп’ютери; мікроконтролери.

Сигнальні процесори (процесори цифрових сигналів) призначені для цифрової обробки сигналів у реальному масштабі часу (наприклад, фільтрація сигналів, обчислення згортки та кореляційної функції, підсилення, обмеження та трансформація сигналу, пряме та обернене перетворення Фур’є).

Медійні та мультимедійні процесори призначені для обробки аудіо сигналів, графічної інформації, відеозображень, а також для розв’язування ряду задач у мультимедіакомп’ютерах, іграшкових приставках, побутової техніці.

Трансп’ютери призначені для масових паралельних обчислень і роботи у мультипроцесорних системах. Для них характерним є наявність внутрішньої пам’яті та вбудованого міжпроцесорного інтерфейсу, тобто каналів зв’язку з іншими МП.

Серед спеціалізованих МП також можна виділити мікроконтролери -- МП, призначені для рішення задач керування якими-небудь процесами або пристроями.

Класифікація МП за функціональним призначенням подана на рис. 1.

Рис. 1. Класифікація МП за функціональним призначенням

На допомогу центральному процесорові в комп'ютер іноді вводять співпроцесори, орієнтовані на ефективне виконання яких-небудь специфічних функцій. Раніше широко були поширені математичні співпроцесори, що обробляють числові дані у форматі з плаваючою комою; графічні співпроцесори, що виконують геометричні побудови й обробку графічних зображень; співпроцесори введення-виведення, що розвантажують центральний процесор від нескладних, але численних операцій взаємодії з зовнішніми пристроями. Можливі й інші співпроцесори, однак усі вони несамостійні - виконання основного обчислювального процесу здійснюється центральним процесором, що відповідно до програми видає "завдання" співпроцесорам на виконання їхніх допоміжних функцій.

2. За числом ВІС, використовуваних для побудови функціонально повного МП, розрізняють однокристальні, багатокристальні і багатокристальні секційні МП.

Однокристальні МП реалізуються у вигляді один ВІС. Логічна структура багатокристального МП розбивається на складні функціональні вузли, кожен з яких реалізується у вигляді окремої ВІС.

Однокристальні МП можуть бути одноядерними та багатоядерними. Багатоядерний процесор має фактично декілька обчислювальних пристроїв, розташованих на одному кристалі, яки можуть працювати паралельно та мають загальні кола введення-виведення.

Багатокристальні секційні (розрядно-модульні) МП використовуються для побудови багаторозрядних МП на основі паралельно включених мікропроцесорних секцій. Мікропроцесорна секція являє собою ВІС для обробки декількох розрядів даних (від 2 до 16), що може використовуватися як самостійно, так і як модуль для побудови МП, що обробляє більш довгі кодові слова.

Переважна більшість сучасних універсальних МП є однокристальними.

3. За розрядністю оброблюваних кодових слів даних МП можуть бути з фіксованою або нарощуваною розрядністю слів.

Процесорами з нарощуваною розрядністю кодів слів є тільки багатокристальні секційні МП, всі інші МП обробляють слова фіксованої розрядності.

4. За способом керування обчислювальним процесом розрізняють МП із мікропрограмним і з схемним (апаратним) керуванням.

Мікропроцесори зі схемним керуванням мають фіксований набір команд, розроблений фірмою-виробником, який не може змінювати користувач. У МП з мікропрограмним керуванням систему команд розробляють при проектуванні конкретного мікропроцесорного комплекту на базі набору найпростіших мікрокоманд з урахуванням класу задач, для яких призначений МПК.

Взагалі мікропроцесорним комплектом називають сукупність інтегральних схем, сумісних за електричними, інформаційними та конструктивними параметрами і призначених для побудови електронно-обчислювальної апаратури та мікропроцесорних систем керування.

За типом архітектури, або принципом побудови розрізняють МП з нейманівською архітектурою та МП з гарвардською архітектурою.

За типом системи команд розрізняють CISC (Complete Instruction Set Computing) – процесори з повним набором команд, і RISC (Redused Instruction Set Computing) – процесори зі зменшеним набором команд.

Питання:

Які є класифікації МП?

Що таке мікропроцесорний комплект?

Для чого існують співпроцесори?

Література:

Аваев Н.А. Основы микроэлектроники . Год издания: 1991

Лекція №10

Принципи функціонування універсальних мікропроцесорів(ср)

План

Загальні принципи побудови та функціонування універсальних МП

Мікроархітектура МП

Складові частини мікропроцесора

Загальні принципи побудови та функціонування універсальних МП:

Всі МП працюють у двійковій системі числення.

Будь-який МП складається з двох основних частин: пристрою управління та АЛП.

АЛП універсального МП будується на основі багаторозрядного суматора; операція додавання чисел із знаками – основна операція, що виконує АЛП. Додавання чисел із знаками звичайно виконується з використанням додаткового коду.

Обчислювальний процес організовується на основі принципу мікропрограмного управління.

Будь-який МП має у своєму складі набір регістрів різного призначення, частина яких доступна для дій, обумовлених безпосередньо програмістом - збереження операндів, виконання дій над ними і формування адрес і операндів у пам'яті. Ці регістри називаються регістрами загального призначення. Інша частина регістрів використовується процесором для службових (системних) цілей, доступ до них може бути обмежений. Є навіть програмно-невидимі регістри. Поняття архітектури МП визначає його складові частини, зв’язки та взаємодію між ними. Архітектура містить: 1) структурну схему МП; 2) програмну модель МП (опис функцій регістрів); 3) організацію пам’яті (ємність пам’яті та способи її адресації); 4) опис організації процедур введення-виведення. Але, як правило, говорячи про архітектуру МП, звичайно мають на увазі його програмну модель, тобто програмно-видимі властивості. Зокрема, 32-розрядні процесори сімейства Іntel х86 мають архітектуру ІA-32 (Іntel Archіtecture 32 bіt).

Під мікроархітектурою МП розуміють внутрішню реалізацію цієї програмної моделі. Тобто, процесори, що мають ті самі програмно-видимі властивості (архітектуру), можуть істотно розрізнятися мікроархітектурними реалізаціями цих властивостей, оскільки розроблювачі МП безупинно прагнуть до максимального підвищення продуктивності, тобто швидкості виконання програм.

Спрощена схема мікропроцесора, зображена на Рис. 1, містить у собі наступні складові частини:

- арифметико-логічний пристрій,

- пристрій керування,

- блок декодування команд,

- блок внутрішніх регістрів МП,

- пристрій шинного інтерфейсу, що включає в себе блок випереджальної вибірки,

- роздільні блоки буферної пам'яті (кеш-пам'яті) команд і даних.

Рис. 1. Спрощена схема універсального мікропроцесора

АЛП – це комбінаційна схема на основі суматора, який сигналами з виходів пристрою керування налагоджується на виконання певної арифметичної або логічної операції над операндами, які пересилаються з пам’яті або регістрів МП.

Пристрій керування відповідно до кодів команд та зовнішніх керуючих сигналів і сигналів синхронізації виробляє сигнали управління для всіх блоків МП.

Внутрішні регістри призначенні для зберігання проміжних результатів обчислень. У складі внутрішніх регістрів виділяється акумулятор – регістр у якому зберігається один з операндів. Після виконання команди в акумуляторі замість операнда розміщується результат операції.

Блок декодування команд формує сигнали для пристрою керування згідно з дешифрованим кодом команди.

Блок випереджальної вибірки самостійно ініціює випереджаючу вибірку кодів команд з пам’яті у чергу команд.

Кеш команд (даних) – буферна статична пам’ять, звернення до якої відбувається на частоті функціонування процесора.

Послідовність функціонування мікропроцесора визначається програмним кодом.

Програмний код - це послідовність команд або інструкцій, кожна з яких певним чином закодована і розташована в цілому числі суміжних байт пам'яті. Кожна інструкція обов'язково має операційну частину, що несе процесорові інформацію про необхідні дії. Операндна частина вказує процесорові, де знаходиться його "предмет праці" -- операнди. Операнди – це об’єкти у вигляді значення даних, вмісту регістрів або комірок пам’яті, з яким оперує команда.

Одноядерний процесор фактично може виконувати тільки один процес - передачу керування від інструкції до інструкції відповідно до програми яка виконується. При цьому можуть виконуватися переходи, розгалуження і виклики процедур, але весь цей ланцюжок запрограмований розроблювачем програми. Послідовність виконання інструкцій, запропонована програмним кодом, може бути порушена під впливом внутрішніх або зовнішніх (щодо процесора) причин - виключень і апаратних переривань.

Типова послідовність роботи МП при виконанні якої-небудь команди містить у собі наступні етапи:

- вибірку чергової команди і даних, необхідних для її виконання, з оперативної пам'яті ЕОМ,

- декодування команди,

- власне її виконання,

- запис отриманого результату в оперативну пам'ять.

Щоб зрозуміти, як працює МП, розглянемо крок за кроком, як він виконує нескладну задачу додавання двох чисел (2+3=5). Вирішується вона в чотири етапи.

Питання:

Які є принципи побудови універсальних ПМ?

Що таке мікроархітектура МП?

Які складові входять до універсального мікропроцесора?

Література:

Угрюмов Е.П. Цифровая схемотехніка. – СПб.: БХВ-Петербург, 2002. с. 175-187, 221-245.

Лекція №11

Принцип роботи МП(ср)

План

Розгляд роботи МП поетапно

Етапи 1-4

Щоб зрозуміти, як працює МП, розглянемо крок за кроком, як він виконує нескладну задачу додавання двох чисел (2+3=5). Вирішується вона в чотири етапи.

Етап 1. Введення цифри "2" приводить МП у стан готовності і подає блокові попередньої вибірки сигнал на запит в оперативній пам'яті комп'ютера інструкції у відношенні нових даних , що надійшли,, оскільки командна кеш-пам'ять такої інструкції не містить.

Нова інструкція з роботи з даними надходить з пам'яті комп'ютера через шинний інтерфейс у МП і записується в командну кеш-пам'ять, де їй привласнюється код "2=X" Слідом за цим блок попередньої вибірки запитує з кеш-пам'яті копію коду "2=X", що направляє для подальшої обробки в блок декодування.

Блок декодування декодує інструкцію "2=X", перетворює її в ланцюжок двійкових символів, що пересилається в керуючий блок і в кеш даних, даючи їм указівка про те, як з отриманою інструкцією надходити далі.

Оскільки блоком декодування прийняте рішення про збереження цифри 2 у кеш даних, керуючий блок виконує відповідну інструкцію для коду "2=X": цифрі 2 у кеш-пам'яті даних привласнюється адреса "Х", тут вона і буде знаходитися в чеканні подальших указівок.

Після цього копія коду "3=Y" надходить з командної кеш-пам'яті в блок попередньої вибірки, відкіля переправляється в декодувальний блок для подальшої обробки.

Етап 2. Введення цифри "3". Блок попередньої вибірки одержує команду на запит у системній пам'яті комп'ютера й у командній кеш-пам'яті інструкцій про дії у відношенні знову даних , що надійшли. Оскільки командна кеш-пам'ять таких інструкцій не містить, вони надійдуть з оперативної пам'яті.

Аналогічно команді "2=X," нові інструкції з даних надходять з пам'яті комп'ютера в МП і записуються в командну кеш-пам'ять, де одержують код адресації "3=Y".

Декодувальний блок декодує інструкцію "3=Y", перетворює її в ланцюжок двійкових символів, що направляє в керуючий блок і в кеш-пам'ять даних, даючи їм указівки про те, як з даною інструкцією поводитися далі.

Оскільки декодувальний блок приймає рішення про збереження цифри 3 у кеш-пам'яті даних, то він виконує відповідну інструкцію для коду "3=Y": цифрі 3 привласнюється в кеш-пам'яті даних адреса "Y", де вона, аналогічно цифрі 2, і буде знаходитися в чеканні подальших указівок.

Етап 3. Уведення команди "+" змушує блок попередньої вибірки запросити з оперативної пам'яті комп'ютера і командної кеш-пам'яті інструкції у відношенні знову даних, що надійшли. Як і в попередніх випадках, ці інструкції повинні бути отримані з оперативної пам'яті.

Оскільки мова йде про інструкцію, яка не використовувалася раніше, "плюс" надходить у МП із пам'яті комп'ютера і записується в командну кеш-пам'ять із присвоєнням адресного коду "X+Y=Z", що позначає операцію додавання.

Слідом за цим блок попередньої вибірки запитує з командної кеш-пам'яті копію коду "X+Y=Z" і пересилає її блокові декодування для подальшої обробки.

Блок декодування декодує інструкцію "X+Y=Z", перетворює її в ланцюжок двійкових символів, що направляє в керуючий блок і в кеш-пам'ять даних, даючи їм указівки про те, як з даною інструкцією надходити далі. Одночасно арифметичний логічний пристрій одержує вказівки на виконання операції ДОДАВАННЯ.

Блок керування аналізує код, а арифметичний логічний пристрій виконує по команді операцію ДОДАВАННЯ чисел, закодованих як "X" і "Y" і витягнутих з кеш-пам'яті даних. Після цього ALU, пересилає в блок регістрів отримане число 5 для запису по одному з адрес.

Етап 4. Вивід результату. Блок попередньої вибірки в черговий раз перевіряє командну кеш-пам'ять на предмет наявності інструкцій, що відносяться до нових даних , що надійшли. Як і колись, такі інструкції там відсутні. Інструкція для значка "=" надходить у МП з оперативної пам'яті комп'ютера через шинний інтерфейс і записується в командну кеш-пам'ять, одержавши код адресації "Prіnt Z" ("відобразити на екрані символ Z).

Слідом за цим блок попередньої вибірки запитує з командної кеш-пам'яті копію коду "Prіnt Z", що пересилає декодувальному блокові для подальшої обробки.

Декодувальний блок декодує інструкцію "Prіnt Z", перетворює її в ланцюжок двійкових символів, що потім пересилається керуючому блокові з указівкою на те, як з отриманою інструкцією поводитися далі.

Тепер, коли значення величини, представленої кодом Z, вже обчислене і записано в позиції № 5 блоку регістрів, для завершення операції додавання 2+3 залишається виконати команду виводу вмісту регістра 5 на екран дисплея. На цьому робота МП закінчується.

Питання:

Розкажіть принцип роботи МП поетапно?

Література:

Угрюмов Е.П. Цифровая схемотехніка. – СПб.: БХВ-Петербург, 2002. с. 175-187, 221-245.

Лекція №12

Генератор тактових сигналів КР580ГФ24(ср)

План

Поняття КР580ГФ2

Принцип роботи генератора КР580ГФ24

Призначення виводів генератора

КР580ГФ24

КР580ГФ24 -электронный компонент, мікросхема спеціалізованого генератора тактових імпульсів (ГТИ), що входить вмикропроцессорный комплект серії КР580. Призначена для спільної роботи з ЦПУ КР580ВМ80А. Є аналогом мікросхеми Intel 8224. Напруга живлення - +5 В, +12 В. Тип корпусу - DIP16.

Мікросхема формує: тактові сигнали C1 і C2 cо взаємнозміщеними фронтами; тактовий сигнал C, по рівню сумісний з ТТЛ і синхронізований з сигналом C2; сигнал STB# "Строб стану", який, поступаючи на системний контроллер, фіксує стан шини даних мікропроцесора; сигнал RESET "Установка".

Генератор опорної частоти при підключенні до виводів X1 і X2 кварцевого резонатора забезпечує високу стабільність частоти, визначувану основною частотою збудження кварцевого резонатора, резонансна частота якого має бути в 9 разів більше вибраної тактової частоти мікропроцесора. При частоті резонатора більше 10 Мгц потрібно послідовно в ланцюзі під'єднати керамічний конденсатор місткістю 3 - 10 пФ.

Вихід генератора опорної частоти виведений на зовнішнє виведення OSC і сполучений усередині мікросхеми з лічильником-дільником, що входить до складу тактового генератора. Тактовий генератор складається з лічильника-дільника на 9, логічних дешифраторів, що формують необхідні тактові імпульси, вихідних формувачів і допоміжних логічних схем і тригерів для генерації вихідних сигналів : C1, C2, C, STB#. Тактові імпульси C1 і C2 амплітудою 12 В управляють МОП-входами мікропроцесора КР580ВМ80А. Тактовий импульc C використовується для управління ТТЛ-входами в режимі прямого звернення до пам'яті.

Інверсний сигнал STB#, тривалість якого дорівнює одному періоду частоти опорного генератора, формується мікросхемою КР580ГФ24 при вступі на її вхід з мікропроцесора КР580ВМ80А сигналу SYN "Синхронізація", машинного циклу, що свідчить про початок. При вступі вхідного сигналу RESIN# мікросхема КР580ГФ24 за допомогою тригера Шмитта і тригера Т1 виробляє сигнал RESET, синхронізований з тактовим сигналом C2, По сигналу RESET здійснюється установка в початковий стан різних пристроїв мікропроцесорної системи. Наявність в мікросхемі тригера Шмитта дозволяє подавати на вхід RESIN# сигнал з пологим фронтом. За допомогою тригера Т2 здійснюється стробування вхідного сигналу RDYIN "Готовність" тактовим сигналом C2.