Кристалдағы жүйелерді Cadence тәсілдерімен жобалау

А.А.Иванов, А.П.Рыжов

Жұмыста заманауи микроэлектрониканың маңызды бағыттарының біріне, кристалдағы жүйелерді жобалауға шолу жасалған. Микроэлектрониканың технологияны өңдеу және автоматтандырылған жобалау жүйесі (САПР) аймағындағы әлемдік көшбасшы Cadence Design Systems, Inc. компаниясының сәйкес келетін өнімдеріне шолу жасалған. Бұл шолу заманауи тапсырмаларға және микроэлектронды құрылғыларды өңдеу тәсілдеріне қызығушылықтары бар мамандар, аспиранттар және студенттер үшін пайдалы.

Кіріспе

Кристалдағы жүйелерді жобалау System-on-Chip (SoC) заманауи микроэлектрониканың дамуындағы озық бағыт болып табылады. SoC-тың кең ауқымда қолданылуын қамтамасыз еткен негізгі факторлар қатарына төмендегілерді жатқызуға болады:

сигналдарды өңдеу тапсырмаларының күрделенуі,

нақты уақыт режиміндегі құрылғылардың жұмысы,

нарыққа жаңа өнімдердің шығу мерзімдерінің негізгі қысқаруы,

прототиптеу құнын қоса отырып, энергия тұтынудың және құрылғылардың құнының төмендеуі.

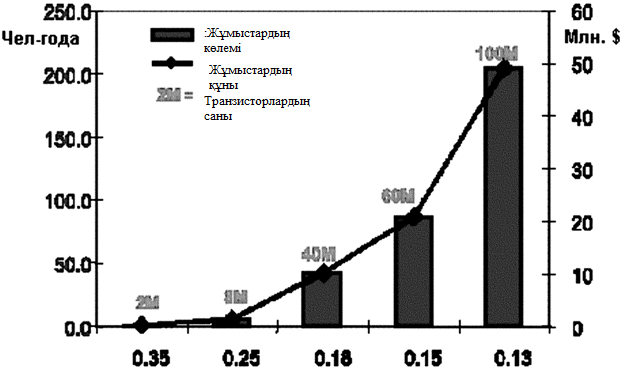

1-суретте уақыт шығынының интегралдық сұлбаларды (ИС) өңдеуге тәуелділік диаграммасы және оның дайындалу технологиясынан алынған құны көрсетілген.

1-сурет.

Сондықтан, САПР-ды өңдеуші компаниялар SoC аймағындағы өздерінің технологияларын, шешімдерін және жүйелерін интегралды сұлбаларды өндірушілерге ұсынады. Cadence Design Systems, Inc. берілген аймақтағы әлемдік көшбасшылардың бірі болып табылады, оның тапсырыскерлері – IBM, Intel, Siemens, Philips, ATI және т.б. сияқты атақты микроэлектронды құрылғыларды өндірушілер.

Кристалдағы жүйелерді өңдеудегі мәселелер

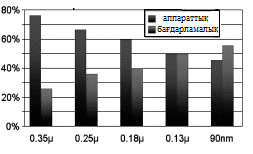

Жобалауда ІР (Intellectual Property) ядроларды қолданғанда SoC жүзеге асуына кететін уақыттық және қаржылық шығындардың төмендеуі мүмкін. ІР блок – кез келген жартылай өткізгішті блоктарды құруда қолдануға жарамды бұрыннан жасалған функция. Нарықта ІР блоктардың орнын процессорлық ядролар, шиналық интерфейстер, кодектер, және т.б. құрылғылар басады. Бағдарламалық ІР-блоктардың сегментінің өсуін ескеруіміз қажет. Заманауи SoC-тарда бағдарламалық бөлімге кететін шығын үлесі аппараттық бөлімге кететін шығын үлесіне қарағанда айтарлықтай тез артуда (2-сурет).

2-сурет. Аппараттық және бағдарламалық SoC құрамдас бөліктерінің құны.

IP-блоктарды пайдалану ұйымдық мәселелердің де (лицензиялау, IP-ядролар кітапханалаары мен стандарттары), техникалық та мәселелердің де (кристалдағы жүйелерді жобалау әдістемелерін әзірлеу, бағдарламалық-аппараттық модельдеу, прототиптеу, заманауи технологиялар базасындағы өндіріс және анықтау) кешенді шешімін талап етеді. Осынша күрделі және кешенді тапсырмаларды шешу, SoC жобалауы секілді, әзірлеу мен модельдеудің заманауи бағдарламалық құралдары – автоматтандырылған жобалар жүйелерін пайдаланбаудың мүмкін еместігі айдан анық.

АЖЖ (САПР) нарығыИС әзірлеу мен анықтау бағыттырының (маршруттараның) бөлек кезеңдерін жүзеге асыру үшін көптеген бағдарламаларды ұсынады, бірақ SoC жобалауының өтпелі бағыты бойынша кешенді шешімдерге тек ірі компаниялардың шамасы келеді. интегралды сұлбалар мен электрониканы жобалау құралдарын әзірлеуде әлемдік көсбасшы Cadence Design Systems болып табылады. Cadence бүгінде SoC заманауи аналогтық-сандық әзірлеу бойынша жүйелік деңгейде IP-блоктарды пайдалану арқылы жобалау кезеңінен ИС топологияларын әзірлеу және өндіріске шығаруға дейінгі анағұрлым біріктірілген шешімді ұсынуға дайын.

2. Кристалдағы жүйелерді жобалау:

Cadence амалы (подход)

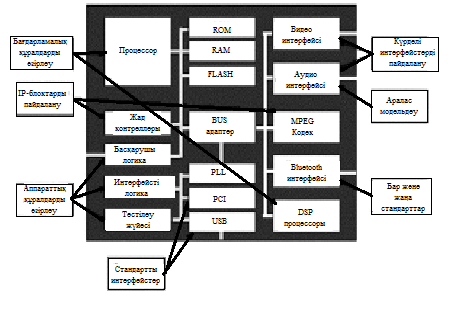

3-сурет. Кристалдағы жүйе.

Заманауи кристалдағы жүйе (3-сурет) бағдарламалық және аппараттық құралдарды: процессорлы ядроларды, бағдарламаланатын логиканы, жадты, интерфейстерді, тестілеудің кіріктірме құралдарын, аналогтық құраушыларын біріктіруі мүмкін. Физикалық барлық осы блоктар бір кристалда жүзеге асуы мүмкін, ал жүйеге бөлек құраушылар ретінде қосылуы мүмкін. Cadence әдістемесі шеңберінде негізгі тапсырмалар жүйені тұтас оңтайландыру, анықтау және құру болып табылады, ал оған жататын құралдарды жобалау алынатын спецификация негізінде жүргізіледі.

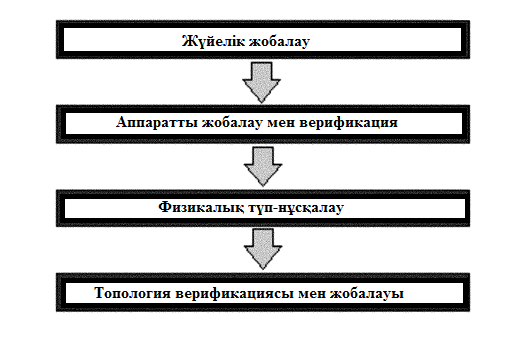

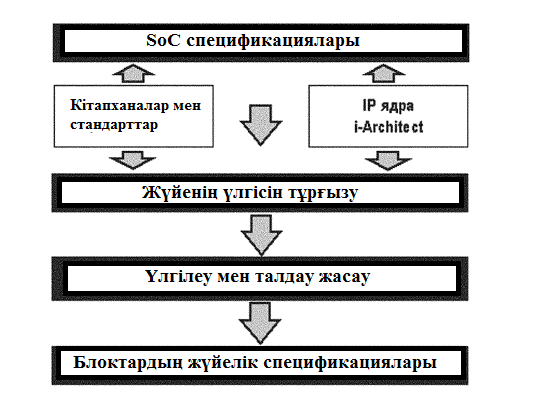

Cadence-ң SoC жобалауының бағыты және оның негізгі кезеңдері 4-суретте көрсетілген.

Пайдаланылатын ұғымдардың келесі анықтамаларын келтіруге болады:

Жүйелік жобалау – C/C++/SystemC пайдалану арқылы абстракцияның жоғарғы деңгейінде жүйелер модельдерін құру, бағдарламалық және аппараттық модульдерге бөліктеу, жүйелер параметрлерін зерттеу, бағдарламалық және аппараттық блоктарға спецификациялар алу;

Аппаратты жобалау мен верификация - Verilog|VHDL тілдерін қолданумен, жүйенің жекеленген мінездемелік үлгілерін олардың спецификациялары негізінде іске асыру, бағдарламалы-аппаратты орындалудың SoC спецификациясына сәйкестігін тексеру мен жобаның құрастырылуы.

SoC жобалауының бағдары

4-сурет. Cadence амалдары арқылы кристаллдағы жүйелерді жобалау

Физикалық түп-тұлғалау - Интегралды сұлбалар өндірісінің базисінде жобаны іске асыру, алдын-ала орналастыру, пайдаланылған қуатқа баға беру, блокты сигналдар ирархиясы мен қорек шиналарын жобалау, мүмкін болатын сигналдардың бұрмалануына сапалы баға беру.

Кристаллдар топологиясының жобалануы мен верфикациясы- тапсырыс блоктарының топологиясын дайындау, ұяшықтар деңгейінің трассировкасын, топологияны жобалау ережелерін тексеру, зиянкес параметрлердің экстракциясы жүзеге асыру.

Жобалау бағдарының әрбір элементін қарастырайық.

2.1 Жүйелік жобалау

Жүйелік жобалаудың негізгі міндеті SoC толықтай спецификациясын жасау мен жоғары деңгейде жүйе үлгілерін құру, бағдарламалық және аппаратты бөліктерінің анықтамаларымен бірге абстракцияларын орындау, жекеленген блоктардың спецификациясынан алынған параметрлерін зерттеу. Бұл кезеңде жобалануының ортақ бағдары 5-суретте көрсетілген.

Жүйелік жобалау

5-сурет.

SoC спецификациясын дайындау кезеңінде функционалды параметрлері мен сипаттамалары, амалдық ортасы, қажет стандарттары мен протоколдары анықталады. Ары қарай Cadence SPW2000 мен i-Architect бағдарламалық амалдарын қолдана отырып, жүйенің үлгісі құрылады. Жүйенің үлгісі SPW2000 блоктарының немесе Matlab, IP - блоктар үлгілерінің, сонымен қатар C\C++\ System C тілдерінде сипатталған, Xilinx IP - ядролары мен блоктарды қолдайтын, кіріктірме кітапханаларының негізінде жасалған, ирархиялық блок-диаграмма түрінде, мамандандырылған BDE редакторында құрылады. SPW2000 кітапханалары коммуникацялық жүйелермен бірге 3500-ге жуық үлгілерді ұсынады:

- CDMA (3GPP)

- CDMA 2000/ IS 2000(NIST)

- Антенналар үлгісі GSM-GPRS-HSCSD-EDGE

-IEEE802.11a/b,HiperLAN/2 WLAN

- Bluetooth WLAN

- IS-54/136,IS-95

- Радиожиіліктік және радарлы кітапханалар

-ADSL

- DVB-T,ISDB-T (Digital TV Comms)

-Matrix library, Galois field және мультимедиялық жүйелер

- MPEG 1,2 кодектер

- Сандық камераның түп-тұлғалануы

- Оптикалық жүйе, датчиктер, компрессия жүйесі

- Сымсыз видеожүйе,JPEG2000 WCDMA интерфейсі

- NTSC кодегінің жобалануы

I-Architect платформалары ғаламтор технологияларын қолдана отырып жұмыс істейді, әр түрлі платформаларды қолдайды және көптеген IP-блоктарының кітапханаларымен жұмыс істеуге мүмкіндік береді, IP қайталап қолданылу және SoC үшін интеграциялануын қамтамасыз етеді.

Жүйе құрылымның жасалуы аяқталғаннан кейін, оған модельдеу мен талдау жасалады. SPW2000 амалдары жүйе жұмысының толығымен немесе жекеленген блоктарының модельдеуін ұсынады. Модельдеу нақты мәліметтер мен сигналдар үшін жүргізілуі мүмкін. Мысалы, сандық байланыс каналдары арқылы суреттердің таралуын модельдеуге болады. Модельдеу кезеңінде жүйенің өнімділігі мен сипаттамаларына талдау жасалады, архитектурасы тексеріледі, туындайтын жанжалдарды шешу амалдары анықталады, алгоритмдер мен протоколдардың оңтайландырылуы жүзеге асады. Қажет болған жағдайларда, бағдарламалық және аппараттық амалдырдың қайта үлестірілуі іске асады, жекеленген блоктарға функционалды өзгертулер енгізіледі және қайта модельдеу жүргізіледі.

Жобалау мен модельдеу циклдерінің қортындысы бойынша, жүйелік архитектуралардың толық сипаттамасы жасалады, жекленген блоктардың спецификациясы мен C\C++\ System C тілдерінде олардың функционалды сипаттамасы іске асады. Ары қарай бір - біріне тәуелсіз құрастырушылар тобымен жасалатын бағдарламалы-аппараттық кезеңмен жалғасады. SPW2000 платформаның жобалаудың аппаратты деңгейімен байланысуын HDS2000 амалдары қамтамасы етеді.

SPW2000 және жобалаудың аппараттық деңгейі арасындағы байланыс HDS2000 құралдарымен жүзеге асырылады. HDS2000 жүйесі фиксацияланған нүктелі мәліметтер тұрпатын қолданады, аппараттық жүйелі модельдеу интерфейсі бар және кітапханалық блоктарын қолданатын құрылымдық сипаттаудан тұратын Verilog/VHDL кодтарды автоматты генерациялауды орындауға мүмкіндік береді. Бұдан басқа, HDS2000-да стандартты және микроархитектуралық блокты кітапханалары, ақырғы күйлер автоматының редакторы, SPW сигналдарының калькуляторы үшін жан-жақты логикалық анализаторы бар.

Жобаны табысты жүзеге асыру үшін оның верификациясын жылжу өлшемі бойынша жүйелік деңгейден толық аппараттық жүзеге асыруына қарай жүргізу қажет. Мұндай верификацияның басты проблемасы – жүйені көрсетудің терең детальдық деңгейінде модельденуіне көп уақыттық шығын кетеді және ол жобаны орындау мерзімінің кенет артуына алып келеді. SPW-та жүйенің функционалдық блоктарының кез-келгені оның HDL-дағы жүзеге асыруымен алмастырылуы мүмкін. SPW модельдеу архитектурасы көріністің аралас деңгейіндегі толық жүйелі модельдеуге мүмкіндік береді, ал ол әрдайым күрделенетін жобаның верификациясына кететін уақыттық шығындардардың өсуін оңтайландыруға мүмкіндік береді. Берілген жүйені қолданудың артықшылығы – жобалаудың циклдарының санын қысқарту кезінде (итерацияның аз көлемімен) , жобаның бірінші реттен табысты жүзеге асыру мүмкіндігінің кенет артуында.