- •Лекція № 12 Комп’ютерні системи класу sisd

- •13.1 Матричний процесор

- •13.2 Матрична комп’ютерна система

- •If a (умова a) then do в

- •13.3 Архітектура матричних комп’ютерних систем

- •13.4 Структура процесорного елементу в матричній кс

- •13.5 Підключення і відключення процесорних елементів в матричних кс

- •13.6 Мережі взаємозв’язків процесорних елементів в матричних кс

- •13.7 Матрична комп’ютерна система illiac IV

- •13.8 Обробка інформації векторним процесором

- •13.9 Структура векторного процесора

- •13.10 Асоціативні кс

- •Контрольні запитання

- •Лекція №14 Конвеєрні комп’ютерні системи

- •14.1 Конвеєрні алп

- •Vliw-конвеєр

- •Суперконвеєр

- •Суперскалярний суперконвеєр

- •Лекція № 15 комп’ютерні системи класу miмd: мультипроцесорні, мультикомп’ютерні, системи з неоднорідним доступом до оперативної пам’яті (numa системи), кластерні системи, grid системи

- •15.1 Мультипроцесорні комп’ютерні системи

- •15.2 Мультипроцесорні кс типу numa

- •15.3 Мультикомп’ютерні комп’ютерні системи

- •Мультикомп’ютерна кс

- •15.4 Кластерні кс

- •15.5 Grid системи

- •Grid технологія створення розподіленої обчислювальної інфраструктури

- •Grid-системи як засіб групового використання ресурсів

- •Grid обчислень

- •Grid даних

- •Grid інструментальних засобів

- •Grid додатків

- •Напрямки використання grid

- •Розвиток і впровадження grid-технологій

- •Контрольні запитання

- •Лекція № 16 Комп’ютерні системи з нетрадиційною архітектурою

- •16.1 Систолічні кс

- •16.2 Класифікація структур систол

- •16.3 Кс з наддовгими командами (vliw)

- •16.4 Комп’ютерні системи з явним паралелізмом команд

- •16.5 Кс з обробкою за принципом хвильового фронту

- •16.6 Кс на базі трансп’ютерів і з неоднорідним доступом до пам’яті

- •Контрольні запитання

- •Лекція № 17 структури комп’ютерних систем з фіксованою системою зв’язків

- •17.1 Системи з фіксованою структурою з серійних мікропроцесорів

- •17.2 Спеціалізовані системи з фіксованою структурою

- •Контрольні запитання

- •Лекція № 19 системи введення-виведення даних в кс

- •19.1 Мережева базова система введення-виведення netbios

- •19.2 Периферійні пристрої для введення-виведення даних в кс

- •19.3 Клавішні пристрої

- •19.4 Сканери

- •19.5 Засоби відображення інформації

- •19.6 Пристрої друкування

- •19.7 Плотери

- •Контрольні запитання

- •Лекція № 20 інтерфейси комп’ютерних систем

- •20.1 Графі́чний інтерфе́йс користувача

- •20.2 Послідовний інтерфейс rs-232c

- •20.3 Паралельні інтерфейси

- •20.4 Шина usb

- •20.5 Пристрої введення (виведення) аналогової інформації в еом (аналого-цифрові інтерфейси)

- •Лекція № 22 структурні аспекти побудови відмовостійких комп’ютерних систем

- •Перелік рекомендованих джерел

- •Литература

13.10 Асоціативні кс

В основі асоціативних КС лежить асоціативний процесор. Асоціативні КС мають n процесорних елементів (ПЕ), як правило, послідовної порозрядної обробки для кожного з елементів пам’яті. Операції здійснюються одночасно всіма n ПЕ. Всі або частина елементарних послідовних ПЕ можуть синхронно виконувати операції над всіма комірками або над вибраною множиною слів асоціативної пам’яті. Приклад асоціативної КС - система STARAN, розроблена Goodyear Aerospace Corporation в 1972 році.

Асоціативний процесор (АП) - це асоціативна пам’ять, що допускає паралельний запис у всі комірки, для яких було зафіксовано збіг з асоціативною ознакою. Ця особливість АП, що носить назву мультизапису, є першою відмінністю асоціативного процесора від традиційної асоціативної пам’яті. Прочитування і запис інформації можуть проводитися по двох зрізах масиву, що запам’ятовує, - або це все розряди одного слова, або один і той же розряд всіх слів. При необхідності виділення окремих розрядів зрізу зайві позиції можна маскувати. Кожен розряд зрізу в АП забезпечений власним процесорним елементом, що дозволяє між прочитуванням інформації і її записом проводити необхідну обробку, тобто паралельно виконувати операції арифметичного складання, пошуку, а також емулювати багато рис матричних КС.

Контрольні запитання

1 Які є типи архітектурної організації масиву процесорних елементів у матричних SIMD-системах?

2 Яка різниця між матричними і векторними комп’ютерними системами?

3 З яких компонентів складається матрична комп’ютерна система?

4 Які функції контролера масиву процесорів?

5 Коли була розроблена комп’ютерна система ILLIAC IV?

Лекція №14 Конвеєрні комп’ютерні системи

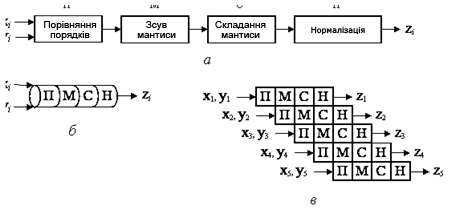

14.1 Конвеєрні алп

У варіанті з конвеєрним АЛП обробка елементів векторів проводиться конвеєрним АЛП для чисел з плаваючою комою (рис.14.1). Операції з числами у формі з плаваючою комою достатньо складні, але піддаються розбиттю на окремі кроки. Наприклад, складання двох чисел зводиться до чотирьох етапів:

- порівняння порядків;

- зміщення мантиси меншого з чисел;

- складання мантис;

- нормалізації результату.

П М С Н

Рисунок 14.1 – Обробка елементів векторів конвеєрним АЛП для чисел з плаваючою комою

Кожен етап може бути реалізований за допомогою окремого ступеня конвеєрного АЛП. Черговий елемент вектора подається на вхід конвеєра, як тільки звільняється перший ступінь (рис.14.2).

|

|

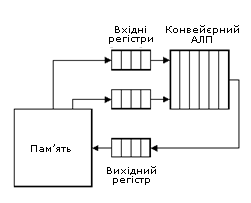

Рисунок 14.2 – Процесор з конвеєрним арифметико-логічним пристроєм

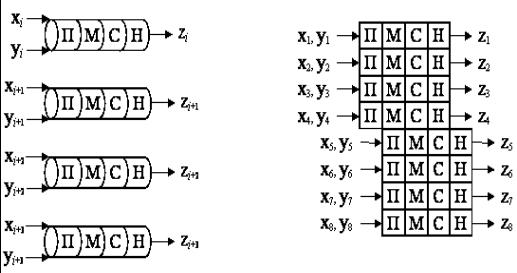

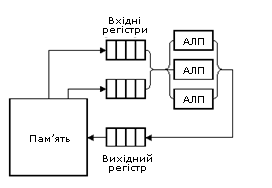

Процесор з паралельними конвеєрними АЛП

Якщо паралельно використовуються конвеєрні АЛП, то можливий ще один рівень конвеєризації. Обчислювальні системи, де реалізована ця ідея, називаються векторно-конвеєрними (рис.14.3).

Рисунок 14.3 – Обробка чисел з плаваючою комою векторно-конвеєрними КС

Комерційні векторно-конвейєрні КС відомі як суперЕОМ (рис.14.4). Треба відмітити, що в склад даних систем для забезпечення універсальності включений також скалярний процесор. |

|

|

|

Рисунок 14.4 – Процесор з масивом паралельних арифметико-логічних пристроїв

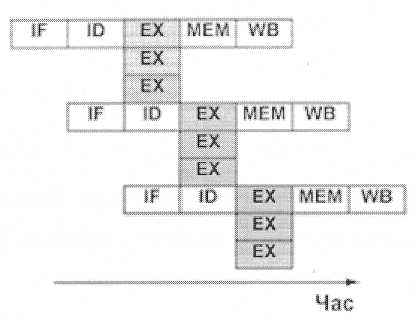

Принцип конвеєрної обробки інформації знайшов широке застосування в обчислювальній техніці. У першу чергу це відноситься до конвеєра команд. Конвеєр команд - апаратна структура в обчислювальних пристроях ЕОМ, призначена для прискорення виконання машинних команд шляхом суміщення певних стадій їх виконання в часі. Практично всі сучасні ЕОМ використовують цей принцип. В основі концепції конвеєризації обчислень є твердження про те, що процес обробки машинної команди можна розбити на декілька практично незалежних етапів, які потім можна суміщати в часі для декількох команд в відповідній апаратурі (конвеєрі команд).

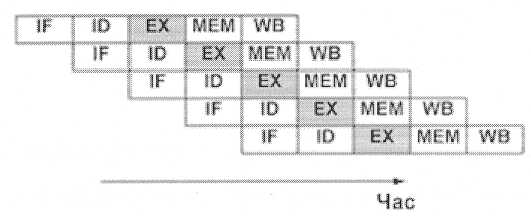

Загальноприйнятим в теорії конвеєрних структур є така послідовність етапів:

- вибірка (instruction fetch, IF) - завантаження нової команди з пам'яті;

- декодування (instruction decode, ID) - інтерпретація та відправка команди у відповідний операційний пристрій в залежності від різновиду операції;

- виконання (execution, ЕХ) - виконання команд та обчислення ефективної адреси пам'яті для результату або операндів, які необхідно завантажити;

- звертання до пам'яті (memory, MEM) - виконання операцій з пам'яттю (для команд завантаження/збереження);

- збереження результату (writeback, WB) - збереження результату обчислень в регістрі.

Слід зазначити, що така структура є типовою для RISС-архітектур. семантика та кількість етапів в яких зазвичай не дуже відрізняється від наведених, тоді як в CISC-архітектурах конвеєр може бути набагато складнішим.

В процесі виконання команд в конвеєрі, відбувається суміщення вказаних етапів виконання для декількох команд (тобто в конвеєрі одночасно знаходяться декілька - до 5 в даному випадку) команд на різних стадіях. Кожний етап конвеєрного обчислення виконується за один машинний цикл. Зрозуміло, що виконання однієї окремої команди на послідовному процесорі (де команда виконується зразу за один машинний цикл) може бути швидшим, аніж в конвеєрній організації. Але за рахунок суміщення виконання різних команд загальна швидкодія істотно збільшується.

Визначимо декілька понять:

- пропускна здатність - максимальна кількість команд, які виконуються за один такт машинного часу (instructions per cycle, ІРС);

- тривалість етапу (стадії) - кількість машинних циклів для виконання одного етапу конвеєрного обчислення (може бути різною для різних етапів);

- необхідний (максимальний) ступінь паралелізму - кількість (незалежних) команд, які потрібно завантажити в конвеєр для повного використання його потенціалу.

Найпростіший (класичний) конвеєр

Характеристики пристрою:

- пропускна здатність = 1 ІРС;

- тривалість стадії = 1 цикл;

- необхідний (максимальний) ступінь паралелізму = 1 команда.

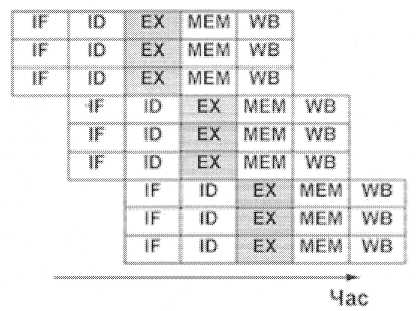

Суперскалярний конвеєр

Характеристики пристрою:

- пропускна здатність = п ІРС (=3 ІРС на малюнку);

- тривалість стадії = 1 цикл;

- необхідний (максимальний) ступінь паралелізму = п команд (=3 на малюнку).

В тому випадку, коли тривалість всіх стадій є однаковою, пропускна здатність суперскалярного конвеєра в п разів вища за звичайний. Однак для повного завантаження та максимальної ефективності необхідно, щоби на кожному циклі роботи він був завантажений п командами, які можуть виконуватись незалежно одна від одної. Така вимога істотно обмежує ефективність суперскалярного конвеєра, адже ступінь схованого паралелізму звичайних послідовних програм, зазвичай, є не дуже високою і в середньому обмежена числами близько 2.5-3 ІРС, хоча на окремих класах задач може бути істотно вищою. Подальше збільшення рівня паралелізму потребує вже зміни самої парадигми програмування.