- •Печатается по плану издания некоммерческого акционерного общества «Алматинский университет энергетики и связи» на 2014 г.

- •1 Описание лабораторного стенда дегем системс

- •1.4 Рабочее задание

- •1.5 Методические указания к выполнению лабораторной работы

- •2 Лабораторная работа. Исследование логических элементов –инвертора серии ттл

- •2.1 Предварительная подготовка

- •2.2. Контрольные вопросы

- •2.3 Задания к лабораторной работе

- •2.4 Расчетное задание

- •2.5 Методические указания к выполнению работы

- •2.6 Задания и методические указания к выполнению виртуальной части лабораторной работы-исследование передаточной характеристики ттл-элемента

- •2.7 Задание Исследование таблицы истинности ттл-элемента с положительной логикой

- •3 Лабораторная работа. Исследование схемы логической серии ecl nor

- •3.1 Предварительная подготовка

- •3.2 Рабочее задание

- •3.3 Методические указания к выполнению работы

- •4 Лабораторная работа. Логические элементы с комплиментарной моп-структурой

- •4.1 Домашняя подготовка

- •4.2 Описание элементов серии cmos

- •4.3 Рабочее задание

- •4.4 Методические указания к выполнению лабораторной работы

- •4.5 Задания и методические указания на выполнение виртуальной части лабораторной работы-исследование передаточной характеристики кмоп – элемента

- •5 Лабораторная работа. Исследование различных комбинации серий логических элементов

- •5.1 Предварительная подготовка

- •5.2 Задание к лабораторной работе

- •5.3 Расчетное задание

- •5.4 Методические указания к выполнению лабораторной работы

- •6 Лабораторная работа. Отыскание повреждении на плате 220

- •6.1 Предварительная подготовка

- •6.2 Рабочее задание

- •6.3 Расчетное задание

- •6.4 Методические указания к выполнению лабораторной работы

- •7 Лабораторная работа. Триггер Шмитта. Электронный сторож на триггерах Шмитта

- •7.1 Предварительная подготовка

- •7.2 Рабочее задание

- •7.3 Методические указания к выполнению работы

5 Лабораторная работа. Исследование различных комбинации серий логических элементов

Цель работы: изучить, как логические элементы, принадлежащие различным сериям, могут быть скомбинированы.

5.1 Предварительная подготовка

5.1.1 Предварительно, до выполнения лабораторной работы изучить по рекомендованной литературе теоретические сведения по различным логическим элементам.

5.1.2 Изучить задание на лабораторную работу и методические указания к нему.

5.1.3 По справочнику записать паспортные данные и перерисовать характеристики исследуемых типов различных логических элементов.

Используемые приборы и элементы:

– центральный процессор РU–2000;

– печатная плата ЕВ–220;

– цифровой универсальный прибор;

– осциллограф.

Контрольные вопросы

1 Если заменить Q2 на многоэмиттерный транзистор, какая схема логического элемента будет И-НЕ или НЕ- И?

2 Почему ток текущий через R8 и R10 может быть пренебрежимо мал?

3 В чем особенность элементов И2Л?

5.2 Задание к лабораторной работе

5.2.1 Проверьте как работает схема и докажите, что она действительно является инвертором.

5.2.2 Измерьте ток потребляемый из источника питания.

5.2.3 Запишите в таблицу 2 значения тока как функции входного логического уровня.

5.2.4 Представьте себе схему, где логический элемент ТТЛ нагружен логическим элементом с комплиментарной МОП-структурой; будет ли она работать правильно?

5.2.5 Измерьте входной ток в каскаде с комплиментарной МОП- структурой.

5.3 Расчетное задание

5.3.1 Рассчитайте ток потребляемый из источника питания и сравните с измеренным значением. Если есть различие большое, то попытайтесь оценить почему?

5.3.2 Рассчитайте среднюю потребляемую мощность схемами логическим элементом CMOS и ТТL. Примите, что половину времени на входе схема имеет логический 0, а логическую 1 – оставшееся время. Сравните этот результат с мощностью, потребляемой мощностью.

5.4 Методические указания к выполнению лабораторной работы

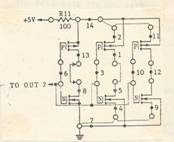

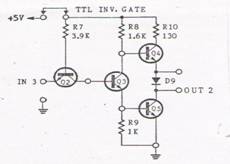

5.4.1 Подсоедините вход инвертора с комплиментарной МОП – структурой к выходу инвертора ТТЛ. Теперь выход инвертора с комплиментарной МОП – структурой будет следовать за входом инвертора ТТЛ. Измерьте затем уровни напряжения на выходе. Подсоедините схему как на рисунке 1, чтобы ТТЛ- инвертор бы нагружен тремя логическими элементами инвертора с комплиментарной МОП – структурой.

а) Подсоедините штыри 2,11 к +5 В.

б) Подсоедините штыри 4,9 к 7 (земля).

в) Cоедините штыри 1 и 5.

г) Cоедините штыри 13 и 8.

5.4.2 Найдите напряжения для обеих логических уровней на выходе одного из логических элементов с комплиментарной МОП- структурой для входных величин 0 и 1.

5.4.3 Отсоедините нагрузочную схему, содержащую С1 и подсоедините выход к резистору R12 (предварительно измерив его сопротивление). Вторую сторону резистора надо заземлить. Как эта нагрузка будет влиять на выходной сигнал?

Рисунок 5.1 Комбинации серии логических инверторов.

Т а б л и ц а 5.1

Uвх, В |

Uвых, В |

|

|