4 семестр / ППЭВС. 4 семестр. Лекция 1

.pdfЛекция 1.

Введение.

В настоящем курсе будут рассматриваться структуры основных узлов цифровых устройств, основанных на базовых цифровых устройствах, относящихся к классу КЦУ или ПЦУ (конечные автоматы). При изучении конструкций таких схем будет представлена возможность проектирования и программирования их в кристалл программируемой логики. Соответственно, для начала необходимо понять, что же представляет собой кристалл программируемой логики, а затем уже перейти непосредственно к конструкциям проектируемых узлов.

Программируемые логические интегральные схемы (ПЛИС).

Если вспомнить этапы синтеза цифрового устройства, то можно выделить два основных момента: запись таблицы функционирования (истинности) и составления на ее основе системы логических уравнений в канонической форме. Структура любого кристалла базируется на p-n переходе, но, соответственно возможностям описания цифрового устройства, эти переходы могут группироваться для построения матриц логических элементов (И – ИЛИ), реализующих функции, записанные в уравнениях, или же для построения матриц на основе простейших таблиц функционирования. Таким образом, ПЛИС делятся на два различных класса:

CPLD – Complex Programmable Logic Devices и FPGA – Field Programmable Gate Array.

Конструктивно любая ПЛИС состоит из внешней части, содержащей буферные и различные адаптирующие элементы, и внутренней части, состоящей из логических блоков, системы межсоединений этих блоков и элементов памяти конфигурации. Рассмотрим структуру внутренней части для каждого из классов ПЛИС.

ПЛИС семейства CPLD.

Структура кристаллов класса CPLD основана на представлении устройства на основе описания его с помощью системы логических уравнений. Такие структуры получили распространение в 80-е – 90-е годы прошлого века. Представление устройства согласно записи в уравнениях было привычно и понятно разработчикам, и, при использовании ПЛИС, не требовало ресурса под создание большой схемы на плате. Изначально такие микросхемы

назывались SPLD (Simple Programmable Logic Devices) и структурно были представлены в виде двух матриц: матрицы элементов И на диодной основе и матрицы элементов ИЛИ на основе биполярных транзисторов. Матрица И всегда полнодоступная – каждый вход в нее, как прямой, так и инверсный, потенциально имеет доступ на каждый выход (терм).

Матрица ИЛИ может быть как полнодоступная – любой из термов может пройти на каждый выход, так и неполнодоступная – на каждый выход может пройти лишь определенная группа термов.

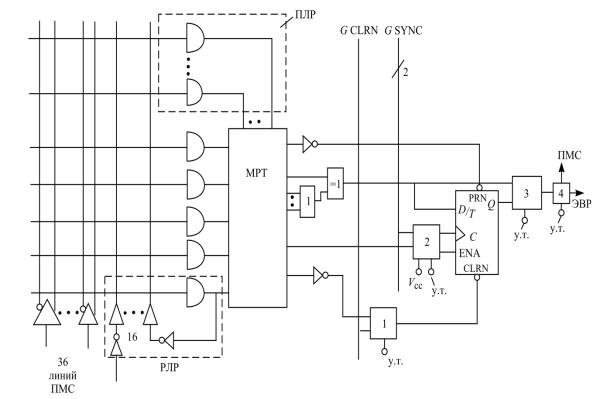

Соответственно, первый тип SPLD назывался ПЛМ (программируемые логические матрицы), а второй тип носил название ПМЛ (программируемая матричная логика). ПЛМ позволяли создать более гибкую структуру, но имели слишком громоздкую матрицу ИЛИ, ПМЛ, в свою очередь, имели облегченную матрицу ИЛИ, но не позволяли создавать гибкие структуры. По мере совершенствования этих структур и создания матриц на основе полевых транзисторов, возникли комбинированные структуры ПЛИС, называемые CPLD. ПЛИС этого типа имеет структуру логического блока, представленную устройством ПМЛ (программируемой матричной логики) с

параметрами для кристаллов фирмы Altera 36x80x16. Т.е. блок содержит 36входов, каждый из которых разделяется на прямой и инверсный, 80 термов (элементов И) и 16 выходов (элементов ИЛИ). Матрица элементов «И» полнодоступная (несвязанная), каждый вход может входить в каждый элемент «И».

Матрица «ИЛИ» для ПМЛ связана, поэтому логический блок состоит из 16 макроячеек, в каждой из которых в элемент «ИЛИ» возможно подключение 5 термов. Для увеличения количества термов, включаемых в «ИЛИ», в структуре блока содержится параллельный логический расширитель. Кроме того, для расширения состава терма в структуре первичной матрицы встроен разделяемый логический расширитель, подключающий инверсный выход пятого терма каждой макроячейки для доступа всем термам своего логического блока. Для сохранения информации предыдущего такта в состав макроячейки входит триггер.

Система межсоединений CPLD представлена программируемой матрицей соединений, позволяющей соединить любую макроячейку с кристалла с другой, в котором из логических блоков она бы ни находилась. Такая структура строится по принципу программируемой логической матрицы (ПЛМ), матрица ИЛИ в которой полнодоступная. Система межсоединений, построенная на основе гибкой логики, позволяет предсказать задержки в схеме.

Память конфигурации CPLD распределенная, построена на базе EEPROM. Это позволяет сохранять конфигурацию схемы в кристалле при выключенном питании.

Функцию, программируемую в кристалле CPLD, желательно описывать с помощью системы логических уравнений в канонической форме с минимизацией. При программировании использовать неразветвленные алгоритмы.

Как следует из вышеизложенного, в кристаллах рассмотренного класса возможно построение схем невысокой степени сложности (КЦУ, конечные автоматы). Единственным преимуществом таких кристаллов является их энергонезависимость.

ПЛИС семейства FPGA.

Основа архитектуры кристалла представленного класса – матрица логических блоков, соединяемых посредством выделенных линий (каналов). Изначально такие логические блоки представляли собой выделенные пространства с определенным количеством переходов: несконфигурированных или сконфигурированных в логические элементы. В этих пространствах строились узлы схем, но выполнялось все не самим пользователем, а под заказ на предприятиях. Схемы назывались GA – Gate Array, вентильные матрицы. Далее, когда прошивать схемы могли уже пользователи, название изменилось на FPGA – Field Programmable Gate Array, программируемые пользователем вентильные матрицы.

Логический блок основан на табличном ЗУ – LUT.

Основа системы межсоединений – выделенные линии каналов. При такой системе компилятору было невозможно предсказать путь соединения логических блоков, расположенных на поверхности кристалла, поэтому задержка в таких схемах оказывалась непредсказуема. Непредсказуемость задержки в схемах, построенных на базе FPGA первых поколений, создавала значительные трудности при работе на высоких частотах.

Для устранения подобных недостатков в FPGA последующих поколений (второго и третьего) стали вводить дополнительные логические связи – локальную матрицу соединений, позволяющую объединять отдельные ячейки, сформированные на основе LUT, в логический блок. Для компенсации фазовых сдвигов в структуру кристалла вошли блоки DLL (Delay locked loop), построенные на основе линий задержек. Логические блоки объединялись с помощью глобальной матрицы соединений канальной структуры.

FPGA 3 поколения

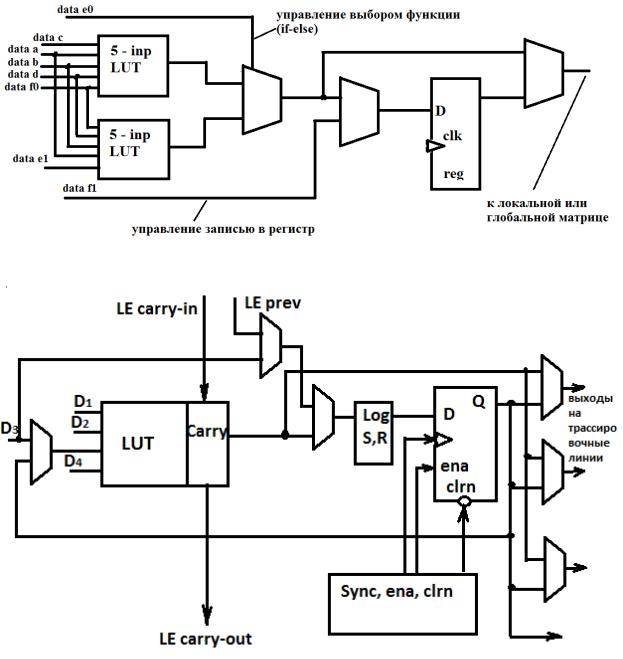

Логический блок стал строиться на основе небольших блоков запоминающих устройств, LUT (Look-up-tables) на16 ячеек (4 входа). Для коммутаций в структуре блока присутствуют управляемые мультиплексоры, для сохранения состояния предыдущего такта – триггер. В дальнейшем, в 4-м и 5-м поколениях FPGA объем памяти LUT возрастает до 64 ячеек.

Фрагменты структуры конфигурируемого логического блока (логического элемента).

Первый фрагмент – укрупненный блок Cyclone V, второй фрагмент –

Cyclone IV.

В FPGA 4 и 5 поколений архитектура основана на матрице мегаблоков, включающих в себя некоторое количество конфигурируемых логических блоков, объединенных посредством локальной матрицы соединений. Элементами такой матрицы служат правые части каждого логического блока,

представленные простой логикой. Левую часть представляют LUT. Каждый мегаблок обслуживает DCM (Digital clock manager), позволяющий не только компенсировать задержки на глобальной матрице, но и изменять частоту и фазу сигнала. Кроме того, мегаблок содержит блок умножителя и встроенный блок памяти.

Рассмотрим структуру FPGA CycloneV . (см. Handbook)

Для структур ПЛИС фирмы Altera характерно применение наборных логических блоков LAB (Logic Array Block) состоящих из адаптивных логических модулей ALM(Adaptive Logic Module). ALM могут конфигурироваться для выполнения различных функций: логических, арифметических, или запоминающих устройств (регистров). LUT в составе ALM может иметь 3, 4, 5 или 6 входов. LUT на 6 входов часто используется в качестве простой (безбуферной) памяти. Таким образом, в качестве дополнительных устройств памяти используется четверть всех имеющихся LAB. В случае такого использования блок именуется MLAB. Каждый LAB может управлять 30-ю ALMs, из которых 10 входят непосредственно в управляющий LAB, и два по 10 - в соседние. Объединение может производиться как по локальным линиям (внутренняя логика), так и по глобальным (линии каналов – строки и столбцы).

Блок управления позволяет получать сигналы тактовой частоты на каждый из управляемых блоков, сигнал разрешения записи, сигнал синхронной загрузки, а также сигналы синхронного и асинхронного сброса.

Режимы работы ALM.

Различают 4 режима работы адаптивных логических модулей.

1.Обычный режим. Допускает обработку двух функций в блоке, или одной функции, имеющей более 6-ти переменных.

2.Режим расширенного LUT. Позволяет объединить 2 блока LUT на 5 входов для представления функции от 7 переменных с использованием оперетора if-else.

3.Арифметический режим. Использует в ресурсе блока две структуры из двух 4-входовых LUT с подсоединенными к ним двумя полными одноразрядными сумматорами. Это позволяет выполнить сложение двух функций из 4-х переменных. Цепь переноса разъединена с выходом.

4.Режим объединенного сумматора. Позволяет осуществить сложение чисел, размещенных в нескольких адаптивных модулях.

Память конфигурации FPGA строится на основе триггерных ячеек (SRAM) и представлена как распределенной (отдельные ячейки, обслуживающие точки связи на каналах)

так и выделенной памятью (LUT, встроенные блоки памяти). В распределенной памяти транзисторы Т1в момент прошивки дают доступ к триггерам, позволяющим осуществлять коммутацию точек a и b, или разрывать соединение между ними.

Встроенные блоки памяти конфигурируются по длине ячейки. Блоки двухбуферные, в начальных вариантах небольшой общей емкости (2К). В последних поколениях схем такие блоки имеют существенно больший объем.

Память конфигурации на ячейках SRAM не позволяет сохранять конфигурацию схемы в кристалле при отключенном питании. Для восстановления конфигурации на плате к схеме присоединяют конфигурационную FLASH, где коды сохраняются при выключенном питании.

Программирование под FPGA всегда следует производить с использованием разветвленных алгоритмов, т.к. в таблицах все ячейки должны быть заполнены.