Задача №4

Из таблицы 4, в соответствии со своим вариантом, выберите тип микросхемы ЗУ, режим работы, значения адреса ячейки памяти.

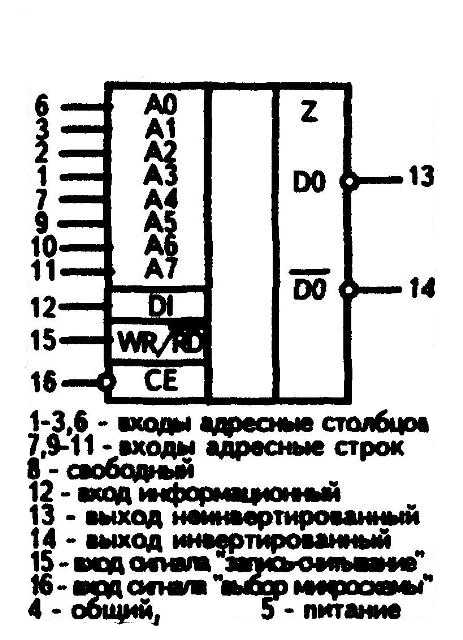

Приведите УГО микросхемы, цоколевку, укажите назначение выводов, разрядность адреса m, разрядность данных n.

Дайте характеристику МКС ЗУ: тип ЗУ, технология изготовления, приведите таблицу режимов работы, на УГО микросхемы укажите значения разрядов адреса, управляющих сигналов для заданного режима работы.

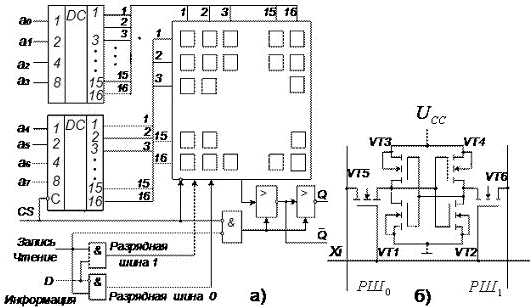

Начертите структурную схему матрицы памяти ЗУ заданной микросхемы, укажите максимальное количество строк и столбцов, выделите на схеме элемент памяти, выбранный в соответствии с указанным в задании адресом.

Запишите адрес ячейки памяти, к которой происходит обращение, в десятичной и шестнадцатеричной системах счисления.

Таблица 4

-

Номер варианта

Тип микросхемы

Режим работы

Адрес ячейки памяти

1

К176РУ2

Запись 1

10011011

Т аблица

истинности микросхемы

аблица

истинности микросхемы

|

WR/ |

A11…A0 |

DI |

DO |

Режим работы |

1 |

X |

X |

X |

Z |

Хранение |

0 |

1 |

A |

1 |

Z |

Запись 1 |

0 |

1 |

A |

0 |

Z |

Запись 0 |

0 |

0 |

A |

X |

данные |

Чтение |

Микросхема К176РУ2) — статическое ОЗУ, имеющее организацию: 256 слов по 1 биту (256 ячеек хранения данных). Структурная схема этого ОЗУ показана на рисунке. В центре ОЗУ К176РУ2 располагается матрица из 256 защелок-триггеров (показана схема одного триггера). Триггеры образуют 16 колонок и 16 рядов. Соответственно имеется 16 вертикальных и 16 горизонтальных линий управления, которые выходят из дешифраторов адреса колонок Y и адреса строки Х соответственно. Оперативное запоминающее устройство имеет восемь входов адреса. Первые четыре разряда A0 — A3 выбирают адрес линии, старшие четыре А4 — А7 адрес колонки, где расположены ячейки хранения каждого одноразрядного слова.

Группа логических элементов, образующих входы CS (доступ к памяти) и R/W (Чтение/Запись), вырабатывает внутренние сигналы К2, K2 (для разрешения записи) и К1, K1 (для разрешения или запрета чтения содержимого памяти).

Выводы 13 и 14 (выходы Q и Q) обслуживают инверторы, имеющие состояние разомкнуто Z. Бит хранения данных вносится в память по выбранному адресу AO — A7 через вход D. Как адрес ячейки записи, так и адрес ячейки считывания выбираются в произвольном порядке. Для чтения и записи на вход CS следует подать напряжение низкого уровня. Напряжением высокого уровня на входе CS эти операции запрещаются, а выходы переходят в Z-состояние. В моменты высокого уровня на входе CS можно менять адреса ячеек (независимо от уровня на входе R/W). Вход CS в схемах, где объединяется много корпусов К176РУ2 служит сигналом выбора отдельного корпуса.

Выходы Q и Q станут активными (чтение), если на обоих входах CS и R/W уровни низкие. Если на входе R/W сменить уровень на высокий, можно записать бит информации. Сигналы управления и выходные состояния сведены в таблицу.

Микросхема К176РУ2 с организацией 256×1 изготовлена по технологии КМОП и представляют собой ЗУ со структурой 3D

4. Микросхема К176РУ2: а) Структурная схема; б) Элемент памяти.

Адрес ячейки памяти: 10011011 получаем 1001(2) = 9(10) и 1011(2) = 11(10)

Номер столбца – 9; Номер строки – 11.

5. 10011011(2) = 128+16+8+2+1 = 155(10) = 9B(16)