- •Содержание

- •Задание к курсовому проекту

- •Введение

- •Простой пятиуровневый конвейер в risc-процессорах

- •История

- •Тактовый генератор

- •Конфликт конвейера

- •Бесконвейерная архитектура

- •Преимущества и недостатки

- •Общий конвейер

- •Общий четырёхуровневых конвейер; цветные квадраты символизируют независимые друг от друга инструкции

- •«Пузырек»

- •Пузырек в третьем такте обработки задерживает исполнение

- •Трудности

- •Граф информационных связей линейного конвейера

- •Операционная схема линейного конвейерного устройства

- •Управляющий автомат линейного конвейерного устройства

- •Гса линейного конвейерного устройства в закодированном виде

- •Граф информационных связей конвейерного устройства

- •Операционная схема конвейерного устройства с обратными связями

- •Сокращенная таблица занятости

- •Полная таблица занятости

- •Граф-схема алгоритма (гса) в закодированном виде

- •Граф-схема алгоритма в закодированном виде

- •Формат микропрограммы

- •Формат микропрограммы

- •Микропрограмма для управляющего автомата

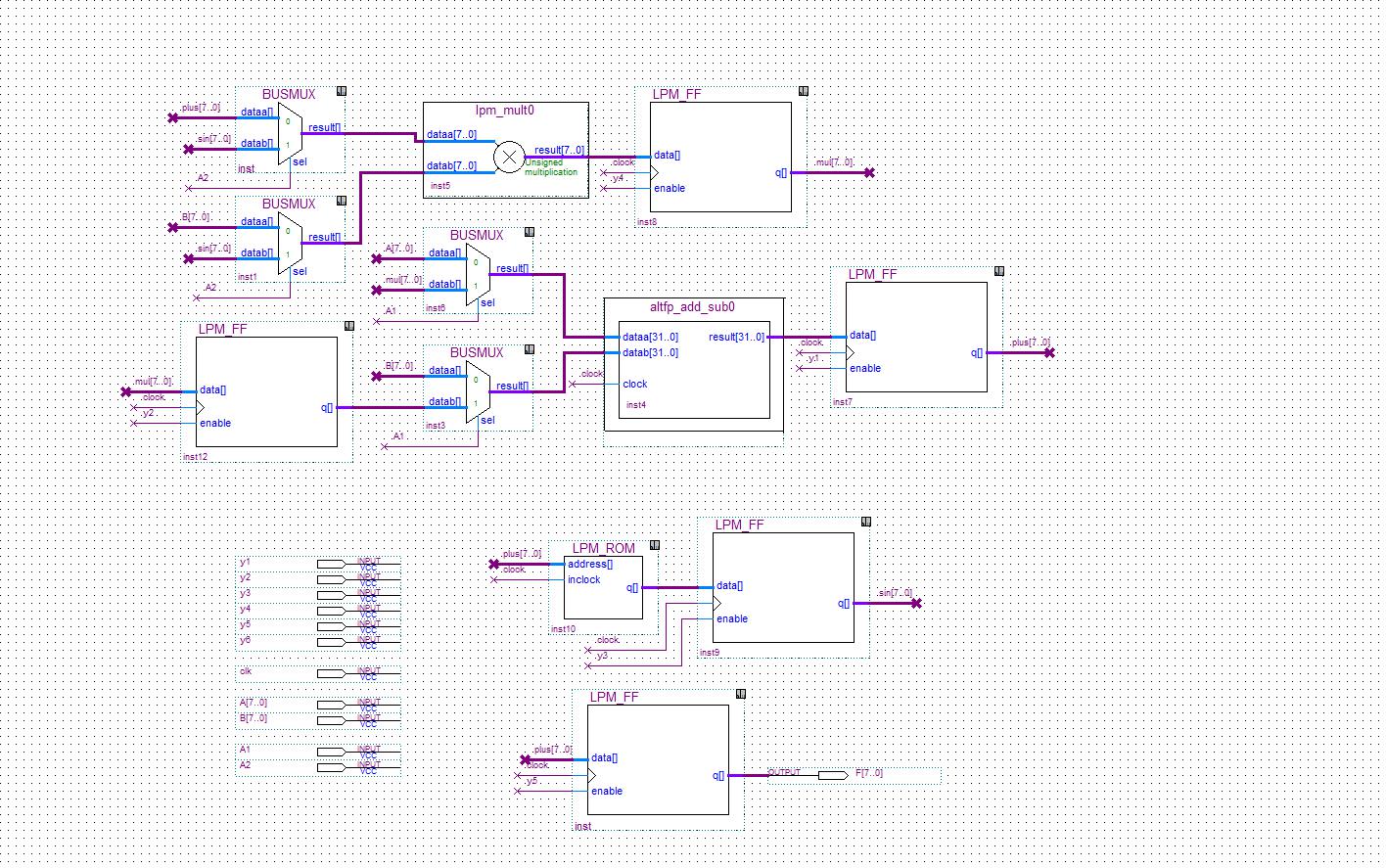

- •Принципиальная схема вычислителя

- •Принципиальная схема конвейерного устройства в визуальном редакторе среды Quartus II Выводы

- •Список использованной литературы

Граф-схема алгоритма (гса) в закодированном виде

Опираясь на таблицу 4 составим ГСА, а также выделим микрокоманды автомата с гибкой логикой. Одной из особенностей данной схемы будет то, что все условия являются инвертированными, т.е. переход будет осуществляться по логическому уровню нуля.

Граф-схема алгоритма в закодированном виде

Формат микропрограммы

На каждый управляющий сигнал отводится один бит. У нас имеется семь таких сигналов: начиная от y0 и заканчивая y6.

На управления двумя парами мультиплексоров отводится 2 управляющих сигнала. Их можно свести до одного, затратив дополнительный логический элемент НЕ. Но это снизит гибкость управляющей микропрограммы, т.к. пары мультиплексоров смогут находится только в противофазе.

Имеется три осведомительных канала и соответственно для них отведено 3 бита.

Т. к. максимальный адрес перехода - АМ5, то для этого механизма достаточно задействовать 3 бита.

Формат микропрограммы

Y |

|

X |

A |

7 |

2 |

3 |

3 |

Микропрограмма для управляющего автомата

Микропрограмма для управляющего автомата с гибкой логикой

|

Y |

|

X |

A |

M0 |

- |

*,* |

|

AM0 |

M1 |

y0 y6 |

*,* |

- |

- |

M2 |

y1 |

0,* |

- |

- |

M3 |

y0 y3 y4 |

*,0 |

- |

- |

M4 |

y1 y2 y4 |

0,1 |

- |

- |

M5 |

y0 y1 y3 y4 |

*,0 |

- |

- |

M6 |

y1 y2 y4 y5 |

*,1 |

- |

- |

M7 |

- |

*,* |

|

AM5 |

M8 |

y1 y3 y4 |

1,0 |

|

|

M9 |

y2 y4 y5 |

*,1 |

|

|

M10 |

y1 |

1,* |

- |

- |

M11 |

y5 |

*,* |

1 |

AM0 |

Принципиальная схема вычислителя

В среде Quartus II была построена принципиальная схема вычислителя, которая представлена на рисунке 11. Следует заметить, что проводники, имеющие одно название - соединены, хотя на схеме могут находится в разных местах. Это сделано, чтобы избежать усложнения восприятия схемы из-за нагромождения рисунков.

Принципиальная схема конвейерного устройства в визуальном редакторе среды Quartus II Выводы

В данной курсовой работе был реализован цифровой вычислитель с конвейерной обработкой данных.

Для проектировании линейного конвейера требуется большее количество информационных блоков, чем при проектировании конвейера с обратными связями – возрастают затраты, но при этом в линейном конвейере нет простоя – выше производительность. Конвейер с обратными связями проектируется для сокращения одинаковых операционных блоков – сокращаются затраты при наличии одинаковых операционных блоков, но падает производительность.

В ходе работы было получено большое количество практических навыков и приобретен опыт по проектированию цифровых вычислителей с конвейерной обработкой данных или просто конвейеров. Работу можно считать успешной, т.к. задание успешно выполнено.