- •6.080402 “Інформаційні технології проектування”

- •Титульний аркуш

- •Основна частина

- •Список літератури

- •Оформлення додатків

- •Правила оформлення текстових документів

- •2.1 Загальні положення

- •2.2 Вимоги до документів, які містять суцільний текст

- •3 Загальні вказівки до виконання курсової роботи

- •3.1 Структура курсової роботи

- •Додаток а

- •Додаток б

- •Список літератури

- •Додаток в Реалізація операції додавання (фрагмент) виконання курсової роботи

- •Функціональна схема алп для виконання операції додавання

- •Реализація операції віднімання

- •Додаток г

Реализація операції віднімання

Вихідні дані

тип арифметичної операції —віднімання двійкових чисел;

вхідний код представлення операндів — додатковий;

розрядність операндів — 8 біт;

код виконання перації в суматорі — додатковий модифікований;

структура операційного блоку — з закріпленими мікроопераціями;

тип керуючого блоку — автомат Мілі с памятю на D -тригерах;

схема логічної ознаки переповнення розрядної сітки;

схема логічного порозрядного множення кодів вхідних операндів А і В.

Алгоритми віднімання двійкових чисел

Алгоритм віднімання двійкових чисел реалізується в наступній послідовності:

в регістри RGA і RGB з вхідної шини один за одним паралельним кодом записуються відповідні їм операнди А і В;

операнди В безумовно інвертується;

мікрооперація віднімання виконується в додаткових модифікованих кодах на протязі одного машинного такту;

аналізується результат розрахунку. При відсутності переповнення розрядної сітки результат записується в регістр RGС і потім пересилається в оперативну пам'ять, при наявності переповнення – результат не фіксується і в ЦПК передається сигнал переповнення Тn.

Функціональная схема АЛП для виконаня операції віднімання

Схема АЛП містить ;

регистри RGA і RGB для приймання і наступного зберігання на протязі виконання мікропрограми з вхідної шини Ш1 операндів А і В;

схему інвертування BIN з вмістом регістру RGB;

електронні ключі SW1 і SW2 для комутації операндів;

схему порозрядного логічного множення;

комбінаційний суматор SM с з додатковим старшим розрядом знаку П для створення модифікованого додаткового коду. На вхід переносу розряду суматора подається логічна одиниця;

регистр результату RGC;

схеми виробітку ознак переповнення ПР;

модуль керуючого блоку МБК на основі автомату Мілі з памятю на D-триггерах.

Мікропрограми віднімання

Мікропрограма віднімання двійкових чисел в модифікованих додаткових кодах має наступний вид:

Початок, якщо K[1], то М1 iнакше – чекати

М1 у1: RGA := 101 <прийому першого операнда>

y2: RGB := 100 <прийому другого операнда>

у3: SM:= 101 + 100 + 1 <мікрооперація віднімання в додаткових кодах>

Якщо <φ3, то M2 інакше

y4: RGC := SM <присвоєння результату>

у5: Ш2 := RGC <пересилка в пам'ять>

Перейти М3

M2 y6 :Тп:= ПП <тригеру переповнення Тп присвоюється признак ПП>

М3 Кінець.

Примітка. К[1] – однорозрядний код команди віднімання

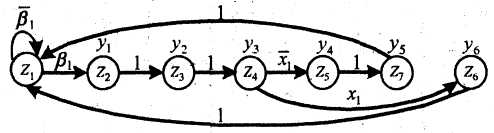

Рисунок Б.5. Змістовний а) і закодований б) графи мікропрограми віднімання

Додаток г

Приклад проектування модуля блока керування

Проектування модуля блоку керування (МБК) на основі автомату Мура з памятю на JK-триггері виконується в наступній послідовності:

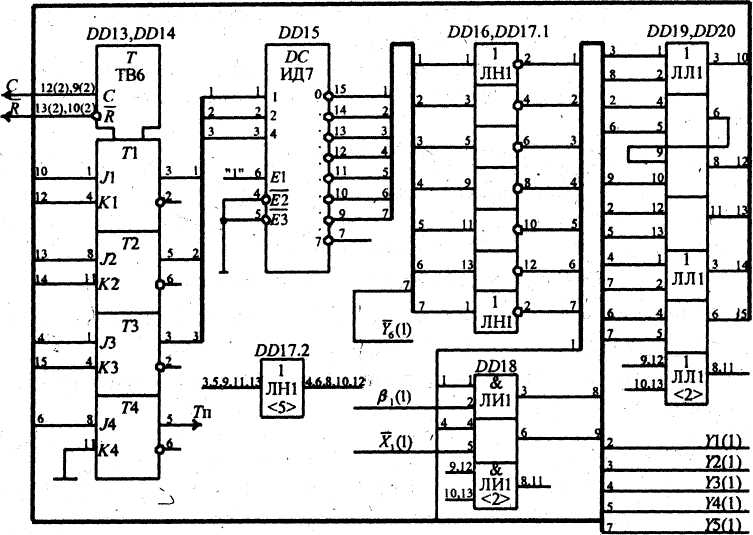

Розмічається закодований граф мікропрограми додавання (рисунок В.1.). Визначається максимальна кількість станів автомату Мура, що дорівнює L = 7. Для реалізації такого числа станів необхідно використовувати n = ]log27[ = 3 триггера.

На основі розміченого графу мікропрограми будується граф автомату Мура (рис. 1.5), який інтерпретує мікропрограму додавання.

Рисунок В.1. 5. Граф автомата Мура для мікропрограми додавання

Стан автомату Мура кодується значеннями виходів JK-триггерів

![]()

На основі графа автомата Мура записується його структурная таблиця переходів (табл. 1.1).

Таблиця В.1 – Структурна таблиця переходів автомату Мура

zi |

k(zi) |

zj |

k(zj) |

{ xi } |

{ yi } |

JK |

|

K |

J |

||||||

z1 |

000 |

z1 |

000 |

не β1 |

- |

- |

- |

z2 |

001 |

β1 |

y1 |

- |

J1 |

||

z2 |

001 |

z3 |

010 |

1 |

y2 |

K1 |

J2 |

z3 |

010 |

z4 |

011 |

1 |

y3 |

- |

J1 |

z4 |

011 |

z5 |

100 |

не xi |

y4 |

K2, K1 |

J3 |

z6 |

101 |

xi |

y6 |

K2 |

J3 |

||

z5 |

100 |

z7 |

110 |

1 |

y5 |

- |

J2 |

z6 |

101 |

z1 |

000 |

1 |

- |

K3, K1 |

- |

z7 |

110 |

z1 |

000 |

1 |

- |

K3, K2 |

- |

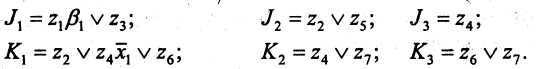

На основі даних табл. В.1 записуються системи логічних рівнянь для функцій збудження входів JK-триггерів і виходів:

Для функцій збудження входів:

Для вихідних сигналів керування:

![]()

Будується принципова схема модуля керування МБК (рисунок В.2.).

Відповідність між входами керування мікросхем МБК і сигналами мікрооперацій наведено у таблиці В.2.

Таблиця В.2 - Відповідність між входами керування мікросхем МБК і сигналами мікрооперацій

Входи |

LA |

LB |

ЛИ1 |

LC |

Tn(J4) |

не EZ |

Сигнали мікрооперацій |

y1 |

y2 |

y3 |

y4 |

y6 |

y5 |

Рисунок В.2. Принципова схема МБК для операції додавання

Для побудови принципової схеми модуля МБК (рисунок В.2) використані наступні мікросхеми:

DD13, DD14 – дві мікросхеми типу ТВ6, кожна з яких містить по два JK-триггера (память автомата Мура);

DD15 — дешифратор типа ИД7. Використовується для виділення станів автомату;

DD16, DD17.1 — дві мікросхеми типу ЛН1, кожна з яких містить шість інверторів;

DD18 — мікросхема типу ЛИ1, кожна містить чотири конюнктора;

DD19, DD20 — дві мікросхеми типу ЛЛ1.

Перелік мікросхем, які використані для побудови АЛП, який реалізує операцію додавання, наведений в таблиці В.3.

Таблиця В.3

Позиції

|

Науменування именование микросхемы |

Кількість |

DDl,DD2 |

КР1533ИР35 |

2 |

DD3, DD4, DD19, DD20 |

КР1533ЛЛ1 |

4 |

DD5-DD8,DD18 |

КР1533ЛИ1 |

5 |

DD19 |

КР1533ЛП5 |

1 |

DD1O |

КР1533ИР22 |

1 |

DD1, DD12 |

КР1533ИМ6 |

2 |

DD13, DD14 |

KP1533TB6 |

2 |

DD15 |

КР1533ИД7 |

1 |

DD16, DD17 |

КР1533ЛН1 |

2 |

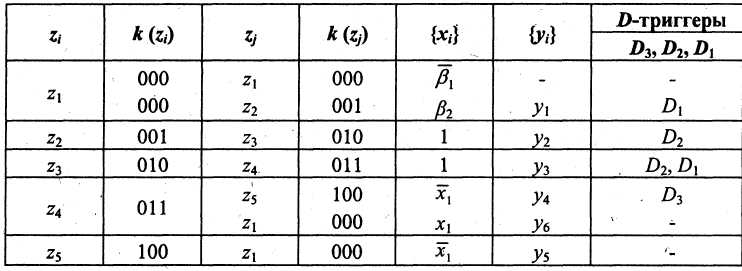

Проектування модуля блоку керування для мікропрограми віднімання

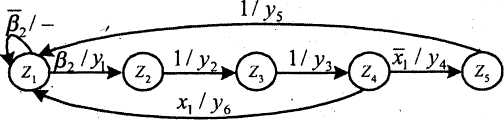

Проектування модуля блоку керування (МБК) на основі автомату Мілі з памятю на D-триггері виконується в наступній послідовності:

Розмічається закодований граф мікропрограми віднімання (рисунок В.3). Визначається максимальна кількість станів автомату Мілі, що дорівнює L = 5. Для реалізації такого числа станів необхідно використовувати n = ]log25[ = 3 триггера.

На основі розміченого графу мікропрограми будується граф автомату Мілі (рис. 1.10), який інтерпретує мікропрограму віднімання.

Рисуенок В.3. Граф автомата Мілі для мікропрограми віднімання

Стан автомату Мілі кодується значеннями виходів D-триггерів

![]()

На основі графа автомата Мілі записується його структурная таблиця переходів (табл. В.4).

Таблиця В.4 – Структурна таблиця переходів автомату Мілі

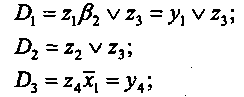

На основі даних табл. В.4 записуються системи логічних рівнянь для функцій збудження входів JK-триггерів і виходів:

Для функцій збудження входів:

Для вихідних сигналів керування:

![]()

Будується принципова схема модуля керування МБК.

Відповідність між входами керування мікросхем МБК і сигналами мікрооперацій наведено у таблиці В.5.

Таблиця В.5 - Відповідність між входами керування мікросхем МБК і сигналами мікрооперацій

Входи |

LA |

LB |

ТЛИ |

LС |

не EZ |

ТП |

Сигнали мікрооперацій |

у1 |

у2 |

у3 |

у4 |

не у5 |

у6 |

СПИСОК ЛІТЕРАТУРИ

Савельєв А. Я. Прикладна теорія цифрових автоматів. Підручник для втузів./ А. Я. Савельєв – М.: Мир, 1989. – 85с.

Шило В. Л. Популярні цифрові мікросхеми./ В. Л. Шило – Вид-во «Питер», 1988. – 352 с.

Бондаренко М. Ф., Білоус Н. В. Комп’ютерна дискретна математика./ М. Ф. Бондаренко, Н. В. Білоус – Харків: Компанія СМІТ, 2004. – 480 с.

Зубчук В. И., Сигорский В. П., Шкуро А. Н. Справочник по цифровой схемотехнике./ В. И. Зубчук, В. П. Сигорский, А. Н. Шкуро – К.: Техника, 1990. – 448с.

Бойко В. І., Жуйко В. Я. та інші. Основи схемотехніки електронних схем/ В. І. Бойко, В. Я. Жуйко та інші. Підручник. – К.: Вища школа, 2004. – 526 с.

Бабич Н. П., Жуков И.А. Компьютерная схемотехника. Методы построения и проектирования: Учебное пособие./ Н. П. Бабич, И. А. Жуков – К.: МК–Пресс “, 2004. –576 с.