- •Базовые понятия компьютерных систем. Классификация компьютерных систем.

- •Основные характеристики процессора

- •Основные компоненты программного обеспечения

- •Структура по

- •Системы счисления

- •Представление двоичных чисел

- •Дробные числа.

- •Аналоговые устройства

- •Цифровые устройства

- •Роль математики и логики в создании кс.

- •Битовые строки

- •Формы представления переключательной функции

- •Минимализация функции алгебры логики (фал)

- •Понятие «Базис»

- •Триггеры

- •Асинхронные rs-триггеры с инверсными входами

- •Регистры

- •Сдвиговые регистры (сдвигающие)

- •Счётчик

- •Сумматоры

- •Шифратор MxN (Coder – cd)

- •Принципиальная схема компьютера (кс)

- •Команда

- •Локальная операция

- •Процессор

- •Двухадресный процессор

- •Двухадресный процессор 1-ого типа

- •Двухадресный процессор 2-ого типа

- •Процессоры с регистрами общего назначения (рон)

- •Система команд фиксированной длинны

- •Система команд разной длины. Битовая память.

- •Косвенные, непосредственные, относительные адреса

- •Использование команд

- •Непосредственный адрес

- •Относительный адрес

- •Формат для относительной адреса:

- •Пересылки

- •Обмен с внешней памятью

- •Команды передачи управления Циклы

- •Блок – схема разветвления

- •Переадресация

- •Цикл итерационного типа

- •Цикл смешанного типа

- •Косвенные адреса

- •Автоинкремент/декремент

- •Индексный регистр

- •Подпрограммы и ввод/вывод

- •Сохранение адреса возврата в регистре

- •Использование стеков

- •Передача параметров

- •Операции ввода/вывода

- •Программно управляемый ввод/вывод

- •Сегментная организация памяти

- •Кэш прямого отображения

- •Ассоциативный кэш

- •Организация процессора Конвейер команд

- •Задержка работы устройств

- •Конфликты по ресурсам

- •Явный конфликт по данным

- •Передача управления

- •Условный переход

- •Основные направления развития системы команд

- •Архитектура с командным словом сверх большой длины

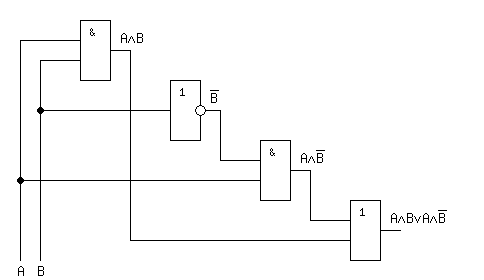

Понятие «Базис»

При составлении схем из логических элементов, решаются задачи анализа и синтеза. Задача синтеза – выбор типов элементов, на которых будут реализованы заданные функции. Минимальный набор логических элементов, образующих функционально полную систему элементов, называют базис, т.е. с помощью элементов базиса можно реализовать сколь угодно сложную логическую функцию.

Основной базис (базис Буль)

Элементы И, ИЛИ, НЕ

Базис Шеффера

Элемент И-НЕ

Базис Пирса

Элементы ИЛИ-НЕ

1 )y=A*B+A*B

Триггеры

Э то основной элемент памяти для хранения единиц информации. Имеет дополнительные схемы управления – ключи, с помощью которых создаются условия для записи и хранения данных. Различные виды триггеров имеют различные входы, но всегда два выхода – прямой и инверсный. Триггер может иметь два устойчивых состояния, которые оцениваются значением сигнала на прямом входе а,(а)- наоборот. Триггер может иметь входы информационные, которые обозначаются: R, S, J, K, D. И входы управляющие: C, V, T.

По способу записи триггеры подразделяются на асинхронные и синхронные. Асинхронный всегда доступен для записи.

В синхронном триггере доступ к ячейке осуществляется только при помощи управляющего сигнала, воздействующего на схему управления.

Типы триггеров:

Тип |

УГО |

Обозначение входов |

Функциональное назначение |

||

Асинхронный RS-триггер с прямыми входами, активный сигнал 1 |

a

|

R-сброс |

Наличие активных

сигналов на R

устанавливает триггер в |

||

Асинхронный RS-триггер с инверсными входами, активный сигнал 0 |

a

|

S-установка |

Наличие активного сигнала вх. 1 устанавливает триггер в 1 |

||

Синхронный триггер |

a

|

С-синхронизация |

Триггер доступен для записи в момент действия сигнала С |

||

D-триггер |

|

D-задержка |

И нформация на входе D попадает в ЭП через ключ с задержкой, определяемой сигналами R и J |

||

JK-триггер |

|

J-внезапное включение |

Информация на входе J будет записана в триггер с приходом сигнала на вход С |

||

Т-триггер |

a

|

Т-переключатель |

Вход Т для счетного режима. С приходом сигнала на вход триггер меняет состояние |