- •Базовые понятия компьютерных систем. Классификация компьютерных систем.

- •Основные характеристики процессора

- •Основные компоненты программного обеспечения

- •Структура по

- •Системы счисления

- •Представление двоичных чисел

- •Дробные числа.

- •Аналоговые устройства

- •Цифровые устройства

- •Роль математики и логики в создании кс.

- •Битовые строки

- •Формы представления переключательной функции

- •Минимализация функции алгебры логики (фал)

- •Понятие «Базис»

- •Триггеры

- •Асинхронные rs-триггеры с инверсными входами

- •Регистры

- •Сдвиговые регистры (сдвигающие)

- •Счётчик

- •Сумматоры

- •Шифратор MxN (Coder – cd)

- •Принципиальная схема компьютера (кс)

- •Команда

- •Локальная операция

- •Процессор

- •Двухадресный процессор

- •Двухадресный процессор 1-ого типа

- •Двухадресный процессор 2-ого типа

- •Процессоры с регистрами общего назначения (рон)

- •Система команд фиксированной длинны

- •Система команд разной длины. Битовая память.

- •Косвенные, непосредственные, относительные адреса

- •Использование команд

- •Непосредственный адрес

- •Относительный адрес

- •Формат для относительной адреса:

- •Пересылки

- •Обмен с внешней памятью

- •Команды передачи управления Циклы

- •Блок – схема разветвления

- •Переадресация

- •Цикл итерационного типа

- •Цикл смешанного типа

- •Косвенные адреса

- •Автоинкремент/декремент

- •Индексный регистр

- •Подпрограммы и ввод/вывод

- •Сохранение адреса возврата в регистре

- •Использование стеков

- •Передача параметров

- •Операции ввода/вывода

- •Программно управляемый ввод/вывод

- •Сегментная организация памяти

- •Кэш прямого отображения

- •Ассоциативный кэш

- •Организация процессора Конвейер команд

- •Задержка работы устройств

- •Конфликты по ресурсам

- •Явный конфликт по данным

- •Передача управления

- •Условный переход

- •Основные направления развития системы команд

- •Архитектура с командным словом сверх большой длины

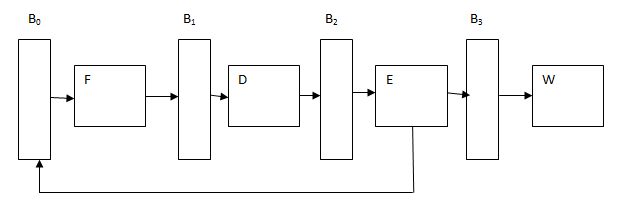

Задержка работы устройств

Если выполнение любого из шагов конвейера затянется, то это задержит все остальное. На чтение команды может уйти более одного такта, если нет команды в КЭШ-памяти. Этап декодирования извлечения операндов зависит от их наличия, выполнение арифметических операций происходит за разное время и зависит от типа операций.

На время работы устройств (F, D, W) влияние оказывает полезное усовершенствование конвейера – увеличение размеров буфера и организация в нем очереди команд. Другие усовершенствования более сложные:

Разработка параметров с несколькими конвейерами команд

Разработка параметра с системой команд, в которой все выполняется за равное число тактов

Конфликты по ресурсам

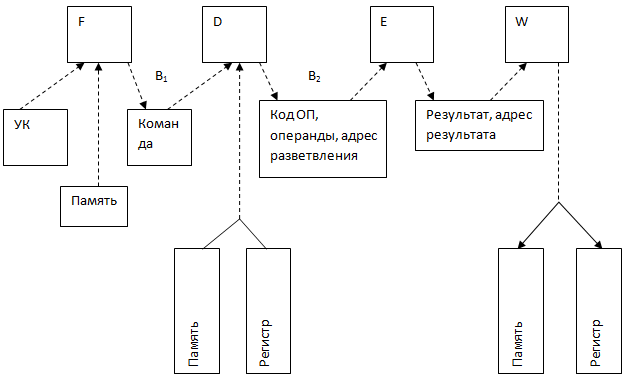

Конфликты возникают, когда два устройства одновременно обращаются к одному ресурсу. Так, в четырехступенчатом конвейере к памяти могут обратиться одновременно три устройства (F, D, W).

Схема конфликта по устройствам:

Меры для уменьшения числа конфликтов:

Разделение КЭШ для данных и команд

Введение двухпортовых регистров(возможно одновременное обращение)

Расслоение память – одновременно обращение к ячейке разных блоков

Явный конфликт по данным

Данные, полученные как результат команды, будут использованы как операнды для последующей команды. Если эта команда следует сразу за первой, то одновременное использование в конвейере приводит к ошибке – конфликту.

Конфликт типа “чтение после записи”, т.е программа рассчитана на последовательное выполнение команд. Сначала производиться запись, а потом чтение. Такая ошибка распознается на этапе трансляции. Имеет место в программе приема.

Изменение порядка следования команд, т.е команды имеющие зависимость по данным, не ставят рядом

Вставляют между зависимыми командами дну или более команд

Аппаратный метод борьбы с такими конфликтами – продвижение операндов.

Схема:

F(Fetch)

|

|

|

|

D(decode) |

|

|

|

E(execute)

|

|

|

|

W(write) |

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|||||||

B1 |

B 2 |

B3 |

Передача управления

Предположим, команда 1 – команда условной передачи управления. После ее завершения должна выполнять либо команду 2, либо команду N.

Схема условной передачи управления:

K1 |

F1 |

D1 |

F1 |

W1 |

|

|

|

|

K2 |

|

F2 |

D2 |

E1 |

W2 |

|

|

|

K3 |

|

|

F3 |

D3 |

E3 |

W3 |

|

|

K… |

|

|

|

… |

… |

… |

… |

|

Kn |

|

|

|

|

Fn |

Dn |

En |

Wn |

Kn+1 |

|

|

|

|

Fn+1 |

Dn+1 |

En+1 |

Wn+1 |

Если переход произойдет, то конвейер теряет 3 такта. Команды 2, 3, 4 из конвейера удаляются. Эти команды называют слотами задержки перехода. Число слотов зависит от числа ступеней. В длинных конвейерах их больше. Применяется условный адрес, передающихся непосредственно УК.

Безусловный переход – устройство Е(исполнительное) определяет, нужен ли переход, но если адрес перехода выполняется раньше устройством D. При этом теряется только один такт.

Другой, более дорогой вариант. Процессор имеет в своем составе буфер адресов перехода.

ВТВ(Branch Target Buffer) - небольшая КЭШ-память, хранящая таблицу последних переходов.

Формат:

Адрес команды

Адрес перехода

Устройство F ищет адрес команды в левой части таблицы. Когда находит, выбирает по адресу правую.