- •Цифровые схемы

- •1. Логические сигналы и вентили

- •Для не специалистов в области электроники надежда остается

- •3.2. Семейства логических схем

- •3.3. Кмоп-логика

- •3.3.1. Логические уровни кмоп-схем

- •3.3.3. Базовая схема кмоп-инвертора

- •Импеданс и сопротивление

- •Что заключено в обозначениях?

- •3.3.4. Кмоп-схемы и-не и или-не

- •Сравнение схем и-не и или-не

- •3.3.5. Коэффициент объединения по входу

- •3 .3.6. Неинвертирующие вентили

- •3.3.7. «Моп-схемы и-или-нЕи или-и-не

- •3.4. Электрические свойства кмоп-схем

- •3.4.1. Общий обзор

- •3.4.2. Справочные данные и спецификация

- •Не бойтесь!

- •Примечания:

- •Что означают числа?

- •3.5. Электрические характеристики кмоп-схем в установившемся режиме

- •3.5.1. Логические уровни и помехоустойчивость

- •3.5.2. Поведение схемы с активными нагрузками

- •Теорема тевенина

- •Правда о потребляемой мощности

- •3.5.3. Поведение схемы с неидеальными входными сигналами

- •3.5.4. Коэффициент разветвления по выходу

- •3.5.5. Влияние нагрузки

- •3.5.6. Неиспользуемые входы

- •Коварные ошибки

- •3.5.7. Броски тока и развязывающие конденсаторы

- •3.5.8. Как испортить кмоп-схему

- •Недопускайте неаккуратного обращения!

- •3.6. Динамические свойства кмоп-схем

- •3.6.1. Длительность переходного процесса

- •Не все так просто!

- •3.6.2. Задержка распространения

- •3.7. Другие варианты входных и выходных цепей кмоп-схем

- •3.7.1. Логические ключи

- •3.7.2. Триггер Шмитта

- •3.7.3. Схемы с тремя состояниями

- •Приведите в порядок передачу данных

- •Юридическая справка

- •3.7.4. Схемы с открытым стоком

- •*3.7.5. Подключение светодиодов

- •Сопротивления резисторов

- •*3.7.6. Шины с несколькими источниками сигналов

- •3.7.7. Монтажная логика

- •*3.7.8. Резисторы, соединяющие выходы схем с шиной питания

- •Допущение, касающееся открытого стока

- •3.8. Семейства схем кмоп-логикн

- •3.8.1. Семейства схем нс и нст

- •3.6.2. Семейства схем vhc и vhct

- •3.6.8. Электрические характеристики схем семейств нс, hct5vhc и vhct

- •Обратите внимание на систему обозначений

- •Экономия энергии

- •М ощность, потребляемая кмоп- и ттл-схемами

- •3.8.4 Схемы семейств fct и fct-t

- •3.8.5. Электрические характеристики схем семейства fct-t

- •Сверхбыстрая коммутация

- •3.9. Логические схемы на биполярных транзисторах

- •3.9.1. Диоды

- •Стрелок, действительно, две

- •Стабилитроны

- •3.9.2. Диодная логика

- •3.9.3. Биполярные транзисторы

- •3.9.4. Транзисторный инвертор

- •3.9.5. Транзисторы Шоттки

- •3 .10. Транзисторно-транзисторная логика

- •3.10.1. Базовый ттл-вентиль и-не

- •Г де же транзистор q1?

- •Снова броски тока

- •3.10.2. Логические уровни и запас помехоустойчивости

- •3.10.3. Коэффициент разветвления по выходу

- •Асимметрия выхода ттл-схем

- •Обожженные пальцы

- •3.10.4. Неиспользуемые входы

- •Плавающие входы ттл

- •Почему применяется резистор?

- •3.10.5. Ттл-схемы других типов

- •3.11. Семейства ттл-схем

- •3.11.1. Первые семейства ттл-схем

- •3.11.2. Ттл-схемы с транзисторами Шоттки

- •3.11.3. Характеристики ттл-схем

- •3.11.4. Справочные данные для ттл-схем

- •Примечания:

- •*3.12. Сопряжение кмоп- и ттл-схем

- •3.13. Схемы низковольтовой кмоп-логики и их сопряжение с другими схемами

- •*3.13.1. Lvttl- и lvcmos-логика с напряжением питания 3.3 в

- •*3.13.2. Входы, допускающие напряжение 5 в

- •*3.13.3. Выходы, допускающие напряжение 5 в

- •*3.13.4. Сопряжение ttl-схем и схем с уровнями lvttl: сводка результатов

- •3.13.5. Логические схемы с напряжениями питания 2.5Ви1.8в

- •3.14. Эмиттерно-связанная логика

- •3.14.1. Базовая схема эсл

- •3.14.2. Семейства эсл-схем 10к/1 он

- •*3.14.4. Эсл-схемы с положительным напряжением питания

- •Обзор литературы

- •Упражнения

*3.13.3. Выходы, допускающие напряжение 5 в

В случае, когда выходы схем с тремя состояниями с напряжением питания 3.3 В и 5 В подключаются к одной шине, необходимо проверить способность выходных цепей выдерживать напряжение 5 В. Когда выход 3.3-вольтовой схемы находится в третьем состоянии (в состоянии Hi-Z), схема с напряжением питания 5 В может стать источником сигнала, передаваемого по шине и на выходе 3.3-вольтовой схемы может появиться напряжение 5 В.

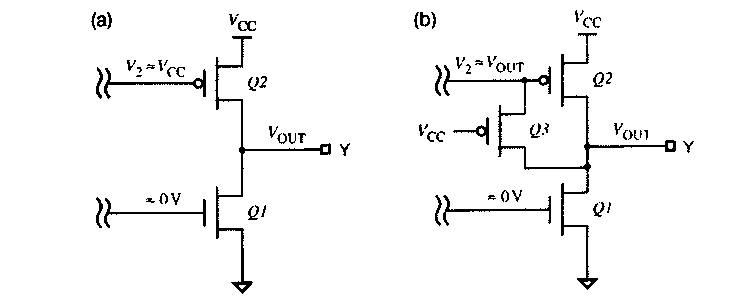

Р ис.

3.87. Выходные цепи КМОП-схем стремя

состояниями: (а) выходы схем НС и VHC, не

допускающих напряжение 5 В; (b) выходы

схем LVC, допускающих напряжение 5В

ис.

3.87. Выходные цепи КМОП-схем стремя

состояниями: (а) выходы схем НС и VHC, не

допускающих напряжение 5 В; (b) выходы

схем LVC, допускающих напряжение 5В

Рис. 3.87 поясняет, почему в этой ситуации некоторые выходные цепи допускают напряжение 5 В, а другие не допускают этого. Как показано на рис. 3.87(а), в обычной КМОП-схеме с тремя состояниями на выходе имеются и-канальный транзистор Q1 между выходом и землей и/т-канальный транзистор Q2 между выходом и шиной питания усс. Когда выход V находится в состоянии Hi-Z, с помощью схемы (не показанной на рисунке) напряжение на затворе транзистора Q1 поддерживается равным примерно О В, а напряжение на затворе транзистора Q2 — примерно равным напряжению питания fcc, так что оба транзистора закрыты.

Рассмотрим теперь, что произойдет, если Vсс = 3.3 В, а от другого устройства на выходной контакту [рис. 3.87(а)] поступает напряжение 5 В. Тогда на стоке транзистора Q2 (вывод Y) будет 5 В, в то время как напряжение на затворе (V2) равно всего лишь 3.3 В. Когда потенциал затвора окажется ниже, чем потенциал стока, транзистор Q2 начнет проводить, цепь от точки Y до шины питания ус„ будет иметь относительно малое сопротивление и потечет большой ток. Выходные цепи схем с тремя состояниями семейств НС и VHC имеют именно такую структуру, и поэтому напряжение 5 В для них не допустимо.

На рис. 3.87(b) приведена выходная цепь, допускающая напряжение 5 В. Дополнительный p-канальный транзистор Q3 позволяет предотвратить отпирание транзистора Q2, когда этого не должно быть. Если напряжение уо[л больше напряжения fcc, то открывается транзистор Q3. Этим обеспечивается относительно малое сопротивление между точкой Y и затвором транзистора Q2, который в данном случае остается закрытым, потому что напряжение V2 на его затворе теперь не меньше напряжения на стоке. Такой является выходная цепь схем LVC фирмы Texas Instruments (низковольтовые КМОП-схемы; low-voltage CMOS).

*3.13.4. Сопряжение ttl-схем и схем с уровнями lvttl: сводка результатов

На основе сведений, приведенных в предыдущих разделах, можно сделать вывод о возможности применения в одной системе ТТЛ-схем (с напряжением питания 5 В) и схем с уровнями LVTTL (с напряжением питания 3.3 В), только следуя следующим трем правилам:

1![]() .

Сигналы с выходов схем с уровнями LVTTL

можно непосредственно подавать

на

входы ТТЛ-схем при соблюдении обычных

ограничений на выходной ток

.

Сигналы с выходов схем с уровнями LVTTL

можно непосредственно подавать

на

входы ТТЛ-схем при соблюдении обычных

ограничений на выходной ток

схем, являющихся источниками сигналов.

2.Сигналы с выходов ТТЛ-схем можно непосредственно подавать на входы схем с уровнями LVTTL, если последние допускают входные напряжения 5 В.

3. Выходы ТТЛ-схем и схем с уровнями LVTTL с тремя состояниями можно подключать к одной и той же шине при условии, что выходы схем с уровнями LVTTL допускают напряжение 5 В.