- •Цифровые схемы

- •1. Логические сигналы и вентили

- •Для не специалистов в области электроники надежда остается

- •3.2. Семейства логических схем

- •3.3. Кмоп-логика

- •3.3.1. Логические уровни кмоп-схем

- •3.3.3. Базовая схема кмоп-инвертора

- •Импеданс и сопротивление

- •Что заключено в обозначениях?

- •3.3.4. Кмоп-схемы и-не и или-не

- •Сравнение схем и-не и или-не

- •3.3.5. Коэффициент объединения по входу

- •3 .3.6. Неинвертирующие вентили

- •3.3.7. «Моп-схемы и-или-нЕи или-и-не

- •3.4. Электрические свойства кмоп-схем

- •3.4.1. Общий обзор

- •3.4.2. Справочные данные и спецификация

- •Не бойтесь!

- •Примечания:

- •Что означают числа?

- •3.5. Электрические характеристики кмоп-схем в установившемся режиме

- •3.5.1. Логические уровни и помехоустойчивость

- •3.5.2. Поведение схемы с активными нагрузками

- •Теорема тевенина

- •Правда о потребляемой мощности

- •3.5.3. Поведение схемы с неидеальными входными сигналами

- •3.5.4. Коэффициент разветвления по выходу

- •3.5.5. Влияние нагрузки

- •3.5.6. Неиспользуемые входы

- •Коварные ошибки

- •3.5.7. Броски тока и развязывающие конденсаторы

- •3.5.8. Как испортить кмоп-схему

- •Недопускайте неаккуратного обращения!

- •3.6. Динамические свойства кмоп-схем

- •3.6.1. Длительность переходного процесса

- •Не все так просто!

- •3.6.2. Задержка распространения

- •3.7. Другие варианты входных и выходных цепей кмоп-схем

- •3.7.1. Логические ключи

- •3.7.2. Триггер Шмитта

- •3.7.3. Схемы с тремя состояниями

- •Приведите в порядок передачу данных

- •Юридическая справка

- •3.7.4. Схемы с открытым стоком

- •*3.7.5. Подключение светодиодов

- •Сопротивления резисторов

- •*3.7.6. Шины с несколькими источниками сигналов

- •3.7.7. Монтажная логика

- •*3.7.8. Резисторы, соединяющие выходы схем с шиной питания

- •Допущение, касающееся открытого стока

- •3.8. Семейства схем кмоп-логикн

- •3.8.1. Семейства схем нс и нст

- •3.6.2. Семейства схем vhc и vhct

- •3.6.8. Электрические характеристики схем семейств нс, hct5vhc и vhct

- •Обратите внимание на систему обозначений

- •Экономия энергии

- •М ощность, потребляемая кмоп- и ттл-схемами

- •3.8.4 Схемы семейств fct и fct-t

- •3.8.5. Электрические характеристики схем семейства fct-t

- •Сверхбыстрая коммутация

- •3.9. Логические схемы на биполярных транзисторах

- •3.9.1. Диоды

- •Стрелок, действительно, две

- •Стабилитроны

- •3.9.2. Диодная логика

- •3.9.3. Биполярные транзисторы

- •3.9.4. Транзисторный инвертор

- •3.9.5. Транзисторы Шоттки

- •3 .10. Транзисторно-транзисторная логика

- •3.10.1. Базовый ттл-вентиль и-не

- •Г де же транзистор q1?

- •Снова броски тока

- •3.10.2. Логические уровни и запас помехоустойчивости

- •3.10.3. Коэффициент разветвления по выходу

- •Асимметрия выхода ттл-схем

- •Обожженные пальцы

- •3.10.4. Неиспользуемые входы

- •Плавающие входы ттл

- •Почему применяется резистор?

- •3.10.5. Ттл-схемы других типов

- •3.11. Семейства ттл-схем

- •3.11.1. Первые семейства ттл-схем

- •3.11.2. Ттл-схемы с транзисторами Шоттки

- •3.11.3. Характеристики ттл-схем

- •3.11.4. Справочные данные для ттл-схем

- •Примечания:

- •*3.12. Сопряжение кмоп- и ттл-схем

- •3.13. Схемы низковольтовой кмоп-логики и их сопряжение с другими схемами

- •*3.13.1. Lvttl- и lvcmos-логика с напряжением питания 3.3 в

- •*3.13.2. Входы, допускающие напряжение 5 в

- •*3.13.3. Выходы, допускающие напряжение 5 в

- •*3.13.4. Сопряжение ttl-схем и схем с уровнями lvttl: сводка результатов

- •3.13.5. Логические схемы с напряжениями питания 2.5Ви1.8в

- •3.14. Эмиттерно-связанная логика

- •3.14.1. Базовая схема эсл

- •3.14.2. Семейства эсл-схем 10к/1 он

- •*3.14.4. Эсл-схемы с положительным напряжением питания

- •Обзор литературы

- •Упражнения

*3.13.2. Входы, допускающие напряжение 5 в

На входы вентиля не всегда можно подавать напряжение, превышающее напряжение питания VCC. Эта проблема возникает в том случае, если в системе применяются схемы как 5-вольтовых, так и 3.3-вольтовых логических семейств. Если, например, 5-вольтовые КМОП-схемы нагружены не сильно, то они вполне могут иметь на выходе 4.9 В, и даже при умеренной нагрузке КМОП- и ТТЛ-схемы обычно дают на выходе 4.0 В. Такие высокие напряжения могут «не понравиться» входам 3.3-вольтовых схем.

Максимальное напряжение Vlmax, которое можно подать на вход, указывается в разделе сообщаемых производителем справочных данных, озаглавленном «Пре-дельные значения». Для схем серии НС величина Vlmax равняется напряжению питания fcc Таким образом, если у схемы из этой серии напряжение питания равно 3.3 В, то на ее входы нельзя подавать сигналы с каких бы то ни было выходов 5-вольтовых ТТЛ- или КМОП-схем. С другой стороны, для схем серии VHC напряжение УЫгк равно 7 В; следовательно, схемы VHC с напряжением питания 3.3 В можно применять для преобразования выходных сигналов 5-вольтовых схем к уровням 3.3-вольтовых устройств для совместного использования с микропроцессорами, блоками памяти и другими устройствами в подсистемах с напряжением питания 3.3В.

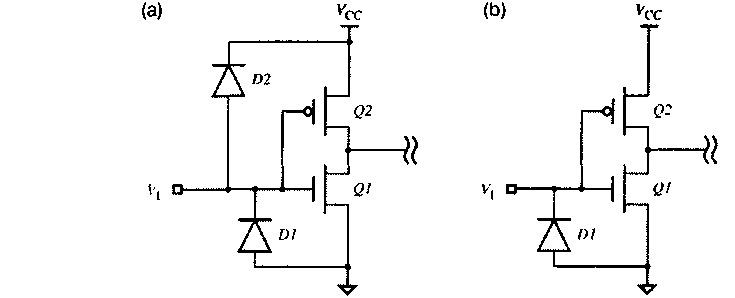

Из рис. 3.86 видно, почему на одни входы можно подавать напряжение 5 В, а на другие нельзя. Как показано на рис. 3.86(а), входная цепь схем НС и НСТ, в действительности, содержит два смещенных в обратном направлении фиксирующих диода (clamp diodes), которые мы прежде не показывали: один диод включен между каждым из входов и шиной питания VCC, а другой - между входом и землей. Назначение этих диодов состоит в том, чтобы с помощью диода D1 шунтировать вход на землю, когда входной сигнал во время переходного процесса становится отрицательным, а с помощью диода D2 замыкать вход на шину питания, когда входной сигнал превышает напряжение питания VCC. Такие кратковременные всплески могут происходить в результате отражений в линии передачи (см. параграф 11.4). Шунтирование входа на землю на время отрицательных выбросов напряжения или на шину питания VCC на время положительных выбросов уменьшает амплитуду и длительность отраженных сигналов.

Р ис.

3.86. Входные цепи КМОП-схем: (а) семейство

НС, не допускающее появления на входе

напряжения, равного 5 В; (b) семейство

VHC, допускающее появление на входе

напряжения, равного 5 В

ис.

3.86. Входные цепи КМОП-схем: (а) семейство

НС, не допускающее появления на входе

напряжения, равного 5 В; (b) семейство

VHC, допускающее появление на входе

напряжения, равного 5 В

С помощью диода D2 нельзя, конечно, отличить кратковременный положительный выброс от превышения входным напряжением напряжения питания V в течение длительного времени. Следовательно, если выход 5-вольтовой схемы соединен с одним из таких входов, то у этого входа не будет очень большого сопротивления, которое обычно ассоциируется с входом КМОП-схемы. Вместо этого входное сопротивление схемы будет относительно малым, равным сопротивлению смещенного теперь в прямом направлении диода D2, подключенного к шине питания VCC, по которому потечет большой ток.

На рис. 3-86(b) показан фрагмент КМОП-схемы, на вход которой можно подавать напряжение 5 В. Во входной цепи этой схемы просто отсутствует диод D2; благодаря диоду D1 сохраняется шунтирование входа при отрицательных выбросах напряжения. Такой вид имеет входная цепь в схемах VHC и АНС.

Структура входной цепи должна быть такой, как показано на рис. 3.86(b), но этого не достаточно, чтобы вход допускал подачу на него напряжения 5 В. Процесс изготовления микросхем должен включать создание транзисторов, способных выдерживать ббльшие напряжения, чем VQC. По этой причине в семействе VHC напряжение V ограничено величиной 7.0 В. В технологическом процессе изготовления многих специализированных интегральных схем с напряжением питания 3.3 В нет возможности получить входы, допускающие напряжение 5 В, даже если есть желание отказаться от выгод, связанных с диодом D2, который шунтирует вход при положительных всплесках в линии передачи.