- •Цифровые схемы

- •1. Логические сигналы и вентили

- •Для не специалистов в области электроники надежда остается

- •3.2. Семейства логических схем

- •3.3. Кмоп-логика

- •3.3.1. Логические уровни кмоп-схем

- •3.3.3. Базовая схема кмоп-инвертора

- •Импеданс и сопротивление

- •Что заключено в обозначениях?

- •3.3.4. Кмоп-схемы и-не и или-не

- •Сравнение схем и-не и или-не

- •3.3.5. Коэффициент объединения по входу

- •3 .3.6. Неинвертирующие вентили

- •3.3.7. «Моп-схемы и-или-нЕи или-и-не

- •3.4. Электрические свойства кмоп-схем

- •3.4.1. Общий обзор

- •3.4.2. Справочные данные и спецификация

- •Не бойтесь!

- •Примечания:

- •Что означают числа?

- •3.5. Электрические характеристики кмоп-схем в установившемся режиме

- •3.5.1. Логические уровни и помехоустойчивость

- •3.5.2. Поведение схемы с активными нагрузками

- •Теорема тевенина

- •Правда о потребляемой мощности

- •3.5.3. Поведение схемы с неидеальными входными сигналами

- •3.5.4. Коэффициент разветвления по выходу

- •3.5.5. Влияние нагрузки

- •3.5.6. Неиспользуемые входы

- •Коварные ошибки

- •3.5.7. Броски тока и развязывающие конденсаторы

- •3.5.8. Как испортить кмоп-схему

- •Недопускайте неаккуратного обращения!

- •3.6. Динамические свойства кмоп-схем

- •3.6.1. Длительность переходного процесса

- •Не все так просто!

- •3.6.2. Задержка распространения

- •3.7. Другие варианты входных и выходных цепей кмоп-схем

- •3.7.1. Логические ключи

- •3.7.2. Триггер Шмитта

- •3.7.3. Схемы с тремя состояниями

- •Приведите в порядок передачу данных

- •Юридическая справка

- •3.7.4. Схемы с открытым стоком

- •*3.7.5. Подключение светодиодов

- •Сопротивления резисторов

- •*3.7.6. Шины с несколькими источниками сигналов

- •3.7.7. Монтажная логика

- •*3.7.8. Резисторы, соединяющие выходы схем с шиной питания

- •Допущение, касающееся открытого стока

- •3.8. Семейства схем кмоп-логикн

- •3.8.1. Семейства схем нс и нст

- •3.6.2. Семейства схем vhc и vhct

- •3.6.8. Электрические характеристики схем семейств нс, hct5vhc и vhct

- •Обратите внимание на систему обозначений

- •Экономия энергии

- •М ощность, потребляемая кмоп- и ттл-схемами

- •3.8.4 Схемы семейств fct и fct-t

- •3.8.5. Электрические характеристики схем семейства fct-t

- •Сверхбыстрая коммутация

- •3.9. Логические схемы на биполярных транзисторах

- •3.9.1. Диоды

- •Стрелок, действительно, две

- •Стабилитроны

- •3.9.2. Диодная логика

- •3.9.3. Биполярные транзисторы

- •3.9.4. Транзисторный инвертор

- •3.9.5. Транзисторы Шоттки

- •3 .10. Транзисторно-транзисторная логика

- •3.10.1. Базовый ттл-вентиль и-не

- •Г де же транзистор q1?

- •Снова броски тока

- •3.10.2. Логические уровни и запас помехоустойчивости

- •3.10.3. Коэффициент разветвления по выходу

- •Асимметрия выхода ттл-схем

- •Обожженные пальцы

- •3.10.4. Неиспользуемые входы

- •Плавающие входы ттл

- •Почему применяется резистор?

- •3.10.5. Ттл-схемы других типов

- •3.11. Семейства ттл-схем

- •3.11.1. Первые семейства ттл-схем

- •3.11.2. Ттл-схемы с транзисторами Шоттки

- •3.11.3. Характеристики ттл-схем

- •3.11.4. Справочные данные для ттл-схем

- •Примечания:

- •*3.12. Сопряжение кмоп- и ттл-схем

- •3.13. Схемы низковольтовой кмоп-логики и их сопряжение с другими схемами

- •*3.13.1. Lvttl- и lvcmos-логика с напряжением питания 3.3 в

- •*3.13.2. Входы, допускающие напряжение 5 в

- •*3.13.3. Выходы, допускающие напряжение 5 в

- •*3.13.4. Сопряжение ttl-схем и схем с уровнями lvttl: сводка результатов

- •3.13.5. Логические схемы с напряжениями питания 2.5Ви1.8в

- •3.14. Эмиттерно-связанная логика

- •3.14.1. Базовая схема эсл

- •3.14.2. Семейства эсл-схем 10к/1 он

- •*3.14.4. Эсл-схемы с положительным напряжением питания

- •Обзор литературы

- •Упражнения

3.13. Схемы низковольтовой кмоп-логики и их сопряжение с другими схемами

Два важных фактора подтолкнули производителей ИС к снижению напряжения питания КМОП-схем:

• В большинстве случаев сигнал на выходе КМОП-схемы изменяется от потенциала земли до напряжения на шине питания, так что величина У в выражении СК2/равняется напряжению питания. При снижении напряжения питания динамическая рассеиваемая мощность уменьшается еще быстрее.

• По мере продвижения технологии ко все меньшим размерам транзисторов, изоляция в виде окиси кремния между затвором КМОП-транзистора и стоком и истоком становится все более тонкой и поэтому неспособна выдержать разность потенциалов, доходящую до 5 В.

В результате группой промышленных стандартов ИС Объединенного технического совета по электронным приборам (JEDEC) в качестве очередного «стандарта» для логических схем были выбраны следующие напряжения питания: 3.3 В ± 0.3 В, 2.5 В ± 0.2 В, и 1.8 В ± 0.15 В. Стандартами JEDEC определены также входные и выходные напряжения логических уровней устройств, работающих с этими напряжениями питания.

Переход к меньшим напряжениям происходил постепенно и будет продолжаться дальше. В отношении дискретных логических семейств тенденция состояла в том, чтобы выпускать компоненты с меньшим напряжением питания и с меньшими значениями напряжений на выходах, но допускающие, тем не менее, более высокие напряжения на входах. В следующем разделе мы увидим, что этот подход позволяет КМОП-схемам с напряжением питания 3.3 В работать совместно с 5-воль-товыми КМОП- и ТТЛ-схемами.

Подобный подход использован во многих специализированных интегральных схемах и микропроцессорах, но часто применяется также и другой метод. Упомянутые устройства достаточно велики, так что имеет смысл снабдить их двумя источниками питания. Низкое напряжение, скажем 2.5 В, служит питанием для внутренних узлов микросхемы, ее логического ядра (core logic). Большее напряжение, например 3.3 В, используется для питания внешних цепей ввода и вывода, образующих интерфейсный блок (pad ring), посредством которого осуществляется сопряжение со схемами старшего поколения, примененными в системе. Для быстрого и безошибочного преобразования логических уровней между логическим ядром и интерфейсным блоком применяются специальные буферные схемы.

*3.13.1. Lvttl- и lvcmos-логика с напряжением питания 3.3 в

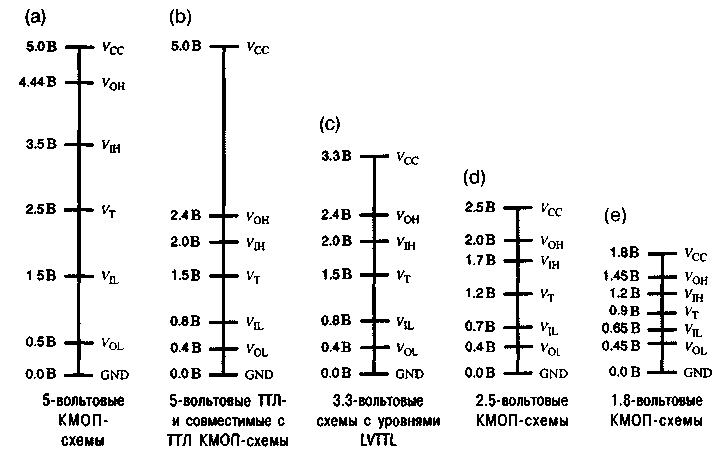

На рис. 3.85 наглядно представлены соотношения между уровнями сигналов для обычных ТТЛ-семейств и низковольтовых КМОП-схем, работающих при своих номинальных напряжениях питания; эти соотношения взяты из указаний по применению фирмы Texas Instruments. Исходные симметричные уровни сигнала для чисто 5-вольтовых КМОП-семейств типа НС и VHC показаны на рис. 3.85(а). В КМОП-схемах, совместимых с ТТЛ-схемами, таких как НСТ, VHCT и FCT, уровни напряжения сдвинуты вниз, как показано на рис. 3.85(b).

Р ис.

3.85. Сравнение логических уровней: (а)

5-вольтовые «МОП-схемы; (b)5-вольтовые

ТТЛ-схемы, а также совместимые с ТТЛ

5-вольтовые КМОП-схемы; (с) 3.3-вольтовые

схемы с уровнями LVTTL; (d) 2.5-вольтовые

КМОП-схемы; (е) 1.8-вольтовые КМОП-схемы

(GND - земля)

ис.

3.85. Сравнение логических уровней: (а)

5-вольтовые «МОП-схемы; (b)5-вольтовые

ТТЛ-схемы, а также совместимые с ТТЛ

5-вольтовые КМОП-схемы; (с) 3.3-вольтовые

схемы с уровнями LVTTL; (d) 2.5-вольтовые

КМОП-схемы; (е) 1.8-вольтовые КМОП-схемы

(GND - земля)

Первым шагом на пути уменьшения напряжения питания КМОП-схем стало напряжение 3.3 В. Фактически стандарт JEDEC для 3.3-вольтовой логики определяет два набора уровней. Уровни LVCMOS (низковольтовыеуровни КМОП-схем; low-voltage CMOS) относятся к случаю использования только КМОП-схем, когда выходы схем слабо нагружены по постоянному току (меньше 100 мкА), так что напряжения FQL и Кон отличаются от потенциала земли и от напряжения питания не более, чем на 0.2 В. Уровни LVTTL (низковольтовыеуровни схем, совместимых с ТТЛ; law-voltage TTL), приведенные на рис. 3.85(с), используются в приложениях, где выходы существенно нагружены по постоянному току, и поэтому напряжение VQL может достигать 0.4 В, а напряжение FQH может опускаться до 2.4 В.

Расположение логических уровней ТТЛ-схем в нижней части 5-вольтового диапазона в действительности было совершенно случайным. Как показано на рис. 3.85(b) и (с), уровни LVTTL оказалось возможным задать так, чтобы они точно совпадали с уровнями ТТЛ-схем. Таким образом, к выходу схемы с уровнями LVTTL можно без проблем подключать входы ТТЛ-схем до тех пор, пока не нарушаются требования относительно величины выходного тока (IOLmax, IOHmax Аналогично к выходу ТТЛ-схемы можно подключать вход схемы с уровнями LVTTL, за исключением тех случаев, когда подаваемый сигнал превышает напряжение питания vcq схем с уровнями LVTTL, равное 3.3 В, о чем речь пойдет ниже.