- •Цифровые схемы

- •1. Логические сигналы и вентили

- •Для не специалистов в области электроники надежда остается

- •3.2. Семейства логических схем

- •3.3. Кмоп-логика

- •3.3.1. Логические уровни кмоп-схем

- •3.3.3. Базовая схема кмоп-инвертора

- •Импеданс и сопротивление

- •Что заключено в обозначениях?

- •3.3.4. Кмоп-схемы и-не и или-не

- •Сравнение схем и-не и или-не

- •3.3.5. Коэффициент объединения по входу

- •3 .3.6. Неинвертирующие вентили

- •3.3.7. «Моп-схемы и-или-нЕи или-и-не

- •3.4. Электрические свойства кмоп-схем

- •3.4.1. Общий обзор

- •3.4.2. Справочные данные и спецификация

- •Не бойтесь!

- •Примечания:

- •Что означают числа?

- •3.5. Электрические характеристики кмоп-схем в установившемся режиме

- •3.5.1. Логические уровни и помехоустойчивость

- •3.5.2. Поведение схемы с активными нагрузками

- •Теорема тевенина

- •Правда о потребляемой мощности

- •3.5.3. Поведение схемы с неидеальными входными сигналами

- •3.5.4. Коэффициент разветвления по выходу

- •3.5.5. Влияние нагрузки

- •3.5.6. Неиспользуемые входы

- •Коварные ошибки

- •3.5.7. Броски тока и развязывающие конденсаторы

- •3.5.8. Как испортить кмоп-схему

- •Недопускайте неаккуратного обращения!

- •3.6. Динамические свойства кмоп-схем

- •3.6.1. Длительность переходного процесса

- •Не все так просто!

- •3.6.2. Задержка распространения

- •3.7. Другие варианты входных и выходных цепей кмоп-схем

- •3.7.1. Логические ключи

- •3.7.2. Триггер Шмитта

- •3.7.3. Схемы с тремя состояниями

- •Приведите в порядок передачу данных

- •Юридическая справка

- •3.7.4. Схемы с открытым стоком

- •*3.7.5. Подключение светодиодов

- •Сопротивления резисторов

- •*3.7.6. Шины с несколькими источниками сигналов

- •3.7.7. Монтажная логика

- •*3.7.8. Резисторы, соединяющие выходы схем с шиной питания

- •Допущение, касающееся открытого стока

- •3.8. Семейства схем кмоп-логикн

- •3.8.1. Семейства схем нс и нст

- •3.6.2. Семейства схем vhc и vhct

- •3.6.8. Электрические характеристики схем семейств нс, hct5vhc и vhct

- •Обратите внимание на систему обозначений

- •Экономия энергии

- •М ощность, потребляемая кмоп- и ттл-схемами

- •3.8.4 Схемы семейств fct и fct-t

- •3.8.5. Электрические характеристики схем семейства fct-t

- •Сверхбыстрая коммутация

- •3.9. Логические схемы на биполярных транзисторах

- •3.9.1. Диоды

- •Стрелок, действительно, две

- •Стабилитроны

- •3.9.2. Диодная логика

- •3.9.3. Биполярные транзисторы

- •3.9.4. Транзисторный инвертор

- •3.9.5. Транзисторы Шоттки

- •3 .10. Транзисторно-транзисторная логика

- •3.10.1. Базовый ттл-вентиль и-не

- •Г де же транзистор q1?

- •Снова броски тока

- •3.10.2. Логические уровни и запас помехоустойчивости

- •3.10.3. Коэффициент разветвления по выходу

- •Асимметрия выхода ттл-схем

- •Обожженные пальцы

- •3.10.4. Неиспользуемые входы

- •Плавающие входы ттл

- •Почему применяется резистор?

- •3.10.5. Ттл-схемы других типов

- •3.11. Семейства ттл-схем

- •3.11.1. Первые семейства ттл-схем

- •3.11.2. Ттл-схемы с транзисторами Шоттки

- •3.11.3. Характеристики ттл-схем

- •3.11.4. Справочные данные для ттл-схем

- •Примечания:

- •*3.12. Сопряжение кмоп- и ттл-схем

- •3.13. Схемы низковольтовой кмоп-логики и их сопряжение с другими схемами

- •*3.13.1. Lvttl- и lvcmos-логика с напряжением питания 3.3 в

- •*3.13.2. Входы, допускающие напряжение 5 в

- •*3.13.3. Выходы, допускающие напряжение 5 в

- •*3.13.4. Сопряжение ttl-схем и схем с уровнями lvttl: сводка результатов

- •3.13.5. Логические схемы с напряжениями питания 2.5Ви1.8в

- •3.14. Эмиттерно-связанная логика

- •3.14.1. Базовая схема эсл

- •3.14.2. Семейства эсл-схем 10к/1 он

- •*3.14.4. Эсл-схемы с положительным напряжением питания

- •Обзор литературы

- •Упражнения

Недопускайте неаккуратного обращения!

В лаборатории ради безопасности следует соблюдать определенные меры предосторожности, связанные с возможностью электростатического разряда, хотя некоторые разработчики и не считают необходимым терпеть возникающие при этом неудобства:

Перед началом работы с КМОП-схемой коснитесь металлического корпуса заземленного прибора или другого места заземления. Перед транспортировкой КМОП-схемы вставьте ее в электропроводящий пенопласт.

При переноске платы, содержащей КМОП-схемы, возьмите ее за края и, прежде чем будете что-нибудь делать с ней, коснитесь заземления земляным выводом платы.

При передаче КМОП-схемы коллеге, особенно в сухой зимний день, сначала коснитесь его. Он или она только скажут вам за это спасибо.

Одной из возможных причин защелкивания являются «отрицательные выбросы», возникающие при очень быстрых переходах сигнала от высокого уровня к низкому, рассматриваемые в параграфе 11.4. В этом случае входной сигнал перед достижением нормального низкого уровня может опуститься ниже уровня земли на несколько вольт. Правда в современных КМОП-вентилях имеются специальные цепи, предотвращающие защелкивание при таком кратковременном процессе.

Защелкивание может наступать также в том случае, когда сигналы поступают на входы КМОП-схемы с выходов другой системы или подсистемы с отдельным источником питания. Если на вход КМОП-схемы подан высокий уровень до того, как включен источник питания, то при включении питания вентиль может перейти в «защелкнутое» состояние. Отметим снова, что современные логические КМОП-схемы изготовлены так, чтобы в большинстве случаев предотвратить это явление. Если, однако, выход предыдущей схемы способен выдать большой ток (например, десятки мА), то защелкивание все же возможно. Одно из решений этой проблемы состоит в том, чтобы включать источник питания до присоединения входных кабелей.

3.6. Динамические свойства кмоп-схем

Как быстродействие КМОП-схемы, так и потребляемая ею мощность в значительной степени зависят от ее характеристик по переменному току или динамических характеристик, а также от нагрузки, то есть от того, что происходит при изменении уровня сигнала на выходе. Частью разработки внутренней структуры специализированных интегральных КМОП-схем должно быть тщательное исследование влияния нагрузки на функционирование выходных цепей, и схему необходимо переделать, если нагрузка слишком велика. Даже на уровне разработки плат необходимо учитывать влияние нагрузки на сигналы синхронизации, сигналы, передаваемые по шинам, и на другие сигналы, поступающие с выхода схем с большим коэффициентом разветвления, а также в том случае, когда разводка осуществляется длинными соединениями.

Быстродействие схемы зависит от двух параметров: от времени переходного процесса и от задержки распространения сигнала; этим двум вопросам посвящены следующие два раздела. Рассеяние мощности рассматривается в третьем разделе.

3.6.1. Длительность переходного процесса

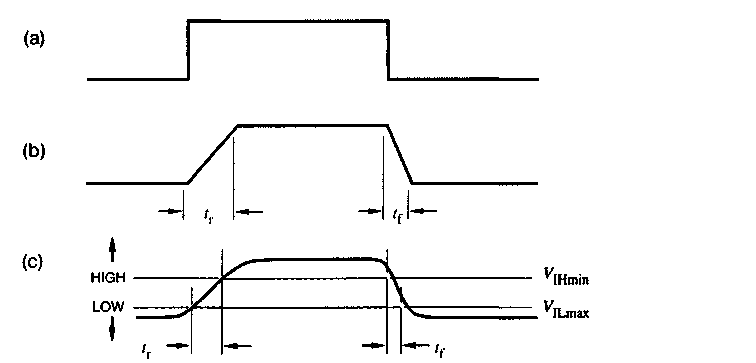

Время, в течение которого сигнал на выходе логической схемы изменяется от одного уровня до другого, называется временем переходного процесса (transition time). На рис. 3.36(а) показано, как могло бы выглядеть изменение выходного сигнала при нулевом времени переходного процесса. Однако реальные выходные сигналы не могут изменяться мгновенно, потому что необходимо время для заряда паразитной емкости между проводами и емкости других компонентов, на которые подаются эти сигналы. Более реалистичный вид выходного сигнала изображен на рис. 3.36(b). В течение времени tr, называемого временем нарастания (rise time), выходной сигнал изменяется от низкого уровня до высокого, а в течение времени tp называемого временем спада (fall time), сигнал изменяется от высокого уровня до низкого; время f может отличаться от времени ?г.

Рис. 3.36. Длительность переходного процесса: (а) идеальный случай с нулевым временем переключения; (b) более близкое к действительности приближение; (с) реальная временная диаграмма с нарастанием и спадом сигнала за конечное время (LOW - низкий уровень, HIGH - высокий уровень)

Рис. 3.36(b) не совсем точен, потому что скорость изменения выходного напряжения не устанавливается мгновенно. Реально переходы в начале и в конце бывают плавными, как это изображено на рис. 3.36(с). Чтобы избежать трудностей в определении начала и конца изменения, время нарастания и время спада обычно измеряют по границам логических уровней, как показано на рисунке.

В соответствии с рис. 3.36(с) время нарастания и время спада говорят о том, как долго выходное напряжение преодолевает область «неопределенности» между низким и высоким уровнями. Время изменения сигнала в пределах одного уровня не включается во время нарастания и время спада. Эта часть переходного процесса вносит вклад в «задержку распространения», которая рассматривается в следующем разделе.

Время нарастания и время спада сигнала на выходе КМОП-схемы зависят в основном от двух параметров: от сопротивления «открытого» транзистора и от емкости нагрузки. При большей емкости время переходного процесса увеличивается и, поскольку это нежелательно, разработчики логических схем очень редко намеренно подключают конденсатор к выходу логической схемы. Однако паразитная емкость (stray capacitance) присутствует в любой цепи, что обусловлено, по крайней мере, тремя причинами:

Выходные цепи, включая выходные транзисторы вентилей, а также внутренние соединения и корпуса схем типичных логических семейств, в том числе КМОП-схем, имеют некоторую собственную емкость в диапазоне от 2 до 10 пикофарад (пФ).

Соединения какого-либо выхода с входами других схем имеют емкость около 1 пФ на дюйм или больше, в зависимости от технологии монтажа.

У типичных логических семейств входные цепи схем, включая транзисторы, внутренний монтаж и корпус микросхемы, имеют емкость от 2 до 15 пФ на вход.

Паразитную емкость иногда называют емкостной нагрузкой (capacitive load) или нагрузкой по переменному току (AC load).

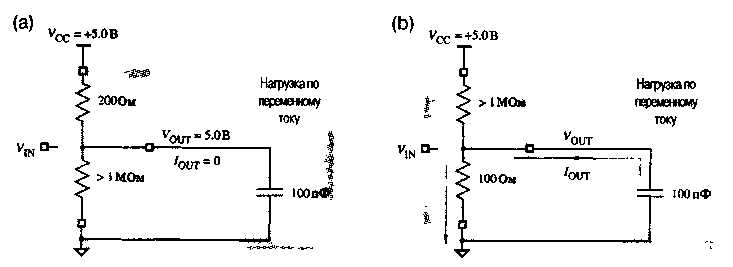

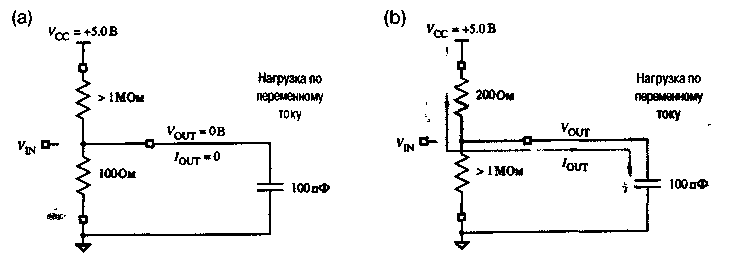

Воспользовавшись эквивалентной цепью, показанной на рис. 3.37, можно рассчитать время нарастания и время спада сигнала на выходе КМОП-вентиля. Как и в предыдущем параграфеp-канальный и n-канальный транзисторы заменены резисторами Rр и Rn соответственно. При нормальной работе сопротивление одного из резисторов велико, а другого – мало в зависимости от уровня сигнала на выходе. Нагрузка на выходе представлена эквивалентной схемой нагрузки (equivalent load circuit), состоящей из трех компонентов:

RL- , VL- два компонента, посредством которых представлена нагрузка по постоянному току; от них зависят напряжения и токи в выходной цепи, когда сигнал на выходе имеет установившееся значение высокого уровня или низкого уровня; при изменении уровня сигнала на выходе нагрузка по постоянному току не оказывает заметного влияния на время перехода;

CL- - емкость, представляющая собой нагрузку по переменному току; от нее зависят значения напряжений и токов в выходной цепи в процессе изменения выходного сигнала и то, как долго происходит переход от одного уровня до другого.

Если выход КМОП-вентиля нагружен входами только КМОП-схем, то нагрузка по постоянному току несущественна. В оставшейся части этого раздела ради простоты мы рассмотрим только этот случай с RL = °° и VL = 0. Наличие некоторой нагрузки по постоянному току повлияет на результат, но не очень сильно (см. упражнение 3.68).

Теперь можно проанализировать время переходного процесса на выходе КМОП-вентиля. Для этого примем CL = 100 пФ, что является умеренной емкостной нагрузкой. Кроме того, будем считать, что, как и в предыдущем разделе, сопротивления «открытых» p-канальных и n-канальных транзисторов равны 200 Ом и 100 Ом соответственно. Время нарастания и время спада сигнала зависят от того, как долго происходит заряд или разряд емкостной нагрузки CL.

Рис. 3.37. Эквивалентная схема для анализа времени переходного процесса в выходной цепи КМОП-вентиля

Р ис.

3.38. Модель перехода КМОП-вентиля от

высокого уровня до низкого: (а) на выходе

вентиля высокий уровень; (b) состояние

вентиля после того, как р-канальный

транзистор оказывается «закрытым», а

n-канальный

транзистор -«открытым»

ис.

3.38. Модель перехода КМОП-вентиля от

высокого уровня до низкого: (а) на выходе

вентиля высокий уровень; (b) состояние

вентиля после того, как р-канальный

транзистор оказывается «закрытым», а

n-канальный

транзистор -«открытым»

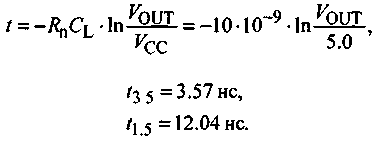

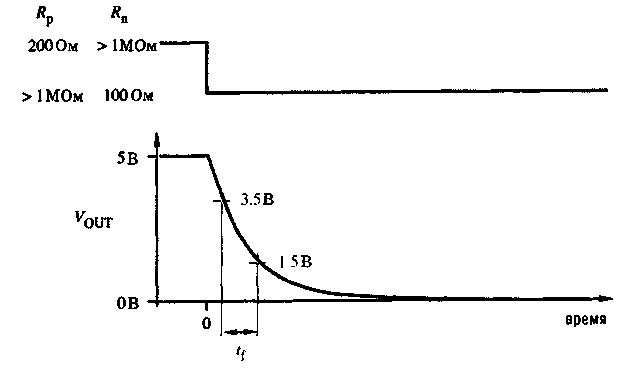

Рассмотрим сначала время спада. На рис. 3.38(а) изображено состояние схемы, когда сигнал на выходе имеет установившийся высокий уровень. (RL- , VL не показаны; они не оказывают никакого влияния, так как мы считаем RL-= °°.) Для нашего анализа предположим, что транзисторы в КМОП-схеме переходят из «открытого» состояния в «закрытое» и обратно мгновенно. Предположим также, что переход сигнала на выходе КМОП-вентиля к низкому уровню начинается в момент времени / = 0, когда схема оказывается в состоянии, указанном на рис. 3.38(b).

В момент времени t=0 напряжение VOUT все еще равно 5.0 В. (Важный принцип электротехники состоит в том, что напряжение на конденсаторе не может изменяться мгновенно.) При t = °° конденсатор должен полностью разрядиться и 4 напряжение VOUT будет равно 0. Между указанными значениями напряжение VOUT изменяется по экспоненциальному закону:

П![]() роизведение

RnCl

имеет размерность времени и

называется постоянной времени (RC time

constant). Проведенное вычисление говорит

о том, что постоянная времени при переходе

от высокого уровня к низкому равна 10

наносекундам (не).

роизведение

RnCl

имеет размерность времени и

называется постоянной времени (RC time

constant). Проведенное вычисление говорит

о том, что постоянная времени при переходе

от высокого уровня к низкому равна 10

наносекундам (не).

В ремя

спада t{ равно разности между этими двумя

числами, что составляет около 8.5 не.

ремя

спада t{ равно разности между этими двумя

числами, что составляет около 8.5 не.

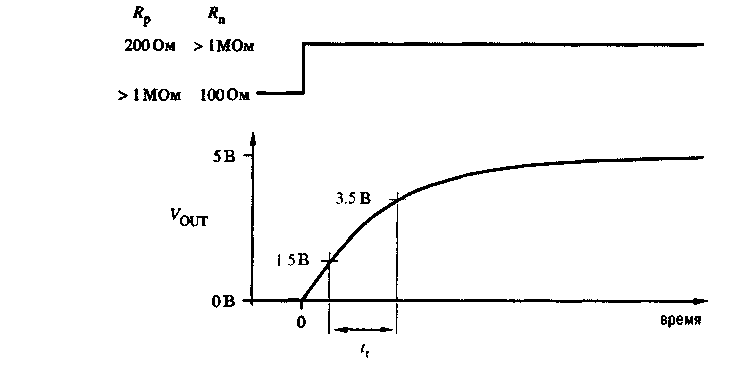

На рис. 3.39 показана зависимость напряжения kout от времени.

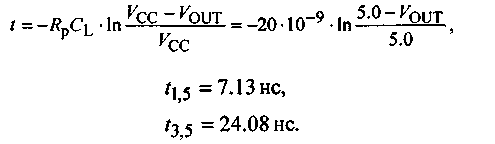

Чтобы определить время спада вспомним, что в качестве границ низкого и высокого уровней входного сигнала КМОП-схемы, подключенной к выходу другой КМОП-схемы, приняты значения 1.5 В и 3.5 В. Чтобы получить время спада, необходимо воспользоваться предыдущим соотношением для VOUT = 3.5 В и VOUT = 1.5 В, откуда следует:

Р ис.

3.39. Время спада при переходе напряжения

на выходе КМОП-вентиля от высокого

уровня к низкому уровню

ис.

3.39. Время спада при переходе напряжения

на выходе КМОП-вентиля от высокого

уровня к низкому уровню

Аналогично можно рассчитать время нарастания сигнала. На рис. 3.40(а) представлено состояние схемы, когда сигнал на выходе имеет установившийся низкий уровень. На рис. 3.40(b) изображен начинающийся в момент времени t=0 переход КМОП-схемы в состояние с высоким уровнем на выходе. Как и прежде, напряжение VOUT не может измениться мгновенно, но при t = °° конденсатор будет полностью заряжен и напряжение VOUT будет равно 5.0 В. Снова изменение напряжения KQUT описывается экспоненциальным законом:

![]()

В ремя

нарастания tr определяется как разность

между полученными двумя числами и

приблизительно равно 17 не.

ремя

нарастания tr определяется как разность

между полученными двумя числами и

приблизительно равно 17 не.

Постоянная времени в этом случае равна RnCl = 20 нc. На рис. 3.41 показана зависимость напряжения VOUT от времени. Чтобы получить время нарастания, снова необходимо воспользоваться имеющимся соотношением для VOUT = 1.5 В и VOUT = 3.5 В, откуда следует:

Р ис.

3.40. Модель перехода КМОП-вентиля от

низкого уровня к высокому уровню на

выходе: (а) низкий уровень на выходе; (b)

состояние схемы после того, как транзистор

с л-каналом оказывается «закрытым», а

транзистор с р-каналом -«открытым»

ис.

3.40. Модель перехода КМОП-вентиля от

низкого уровня к высокому уровню на

выходе: (а) низкий уровень на выходе; (b)

состояние схемы после того, как транзистор

с л-каналом оказывается «закрытым», а

транзистор с р-каналом -«открытым»

В последнем примере предполагается, что p-канапьный транзистор имеет вдвое большее сопротивление, чем и-канальный транзистор; в результате время нарастания вдвое больше времени спада. «Слабому» p-канальному транзистору требуется больше времени для того, чтобы подтянуть выходное напряжение до высокого уровня, чем «сильному» и-канальному транзистору для того, чтобы понизить его до низкого уровня; способность вентиля переключать выходной сигнал «асимметрична». В быстродействующих КМОП-устройствах р-канальные транзисторы иногда изготовляют большего размера, чтобы уравнять времена переходов и сделать переходы на выходе от высокого уровня к низкому уровню и обратно более симметричными.

С

увеличением емкости нагрузки - независимо

от свойств транзисторов - постоянная

времени имеет большее значение и

длительность переходных процессов на

выходе растет. Таким образом, задача

разработчиков быстродействующих схем

состоит в минимизации емкостной нагрузки,

особенно для сигналов, наиболее критичных

в отношении времени. Это можно сделать,

уменьшая число входов, на которые

поступает данный сигнал, путем создания

нескольких копий этого сигнала, а

также посредством аккуратной разводки

схем ы.

ы.

Рис. 3.41. Время нарастания при переходе напряжения на выходе КМОП-вен-тиля от низкого уровня к высокому

При работе с реальными цифровыми схемами часто желательно оценить время переходных процессов без проведения детального анализа. Полезное эмпирическое правило состоит в том, что время переходного процесса приблизительно равняется постоянной времени КС-цепи заряда или разряда. Например, оценки 10 не и 20 не для времени спада и нарастания в рассмотренном примере были бы достаточно приемлемыми, особенно с учетом того, что большинство предположений, прежде всего относительно емкости нагрузки и сопротивлений «открытых» транзисторов, являются приблизительными.

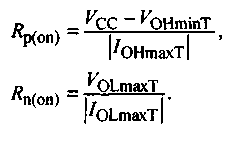

И зготовители

коммерческих КМОП-схем в своих справочных

данных обычно не указывают сопротивления

«открытых» транзисторов. Если тщательно

поискать, то эту информацию можно найти

в публикуемых изготовителями комментариях.

Это сопротивление в любом случае можно

оценить как частное от деления напряжения

на «открытом» транзисторе на ток,

протекающий через активную нагрузку в

наихудшем случае, как это было показано

в разделе 3.5.2:

зготовители

коммерческих КМОП-схем в своих справочных

данных обычно не указывают сопротивления

«открытых» транзисторов. Если тщательно

поискать, то эту информацию можно найти

в публикуемых изготовителями комментариях.

Это сопротивление в любом случае можно

оценить как частное от деления напряжения

на «открытом» транзисторе на ток,

протекающий через активную нагрузку в

наихудшем случае, как это было показано

в разделе 3.5.2: