- •Практическое занятие №1 Тема: Кодирование информации. Системы счисления. Представление чисел в разных системах счисления.

- •Задания для практического занятия и инструктаж по их выполнению

- •Теоретические сведения

- •Задания.

- •Домашнее задание.

- •Практическое занятие №2. Тема: Правила недесятичной арифметики. Сложение, умножение, деление, сдвиг.

- •Задания для практического занятия и инструктаж по их выполнению

- •Теоретические сведения

- •Дополнительные задания:

- •Задания для самостоятельного решения (домашнее задание)

- •Практическое занятие №3 Тема: Логические операции в эвм. Основные логические функции

- •Теоретические сведения

- •Построение таблиц истинности логических выражений.

- •Практическое занятие №4. Тема: Логические элементы шифраторы и дешифраторы.

- •Теоретические сведения

- •Практическое занятие №5 Тема: Логические элементы мультиплексоры, пороговые ячейки.

- •Теоретические сведения

- •Практическое занятие №6 Тема: Логические элементы триггеры. Rs-триггеры, d-триггеры, jk-триггеры.

- •Теоретические сведения

- •Практическое занятие №7. Тема: Логические элементы полусумматоры и сумматоры.

- •Задания для практического занятия и инструктаж по их выполнению

- •Теоретические сведения

- •Практическое занятие №8. Тема: Логические элементы счетчики. Прямой и обратный счетчик. Регистры

- •Теоретические сведения

- •Двоичный счетчик.

- •Практическое занятие №9. Тема: Моделирование работы узлов компьютера с помощью Excel.

- •Задания для практического занятия и инструктаж по их выполнению

- •Схемы сравнения кодов

- •Одноразрядная схема сравнения кодов

- •Многоразрядная схема сравнения кодов

- •Дешифраторы

- •Практическое занятие №10. Тема: Моделирование работы узлов компьютера с помощью Excel

- •Задания для практического занятия и инструктаж по их выполнению Сумматоры

- •Полусумматор

- •Одноразрядный сумматор

- •Многоразрядный сумматор

- •Практическое занятие №11. Тема: Установка процессора в сокет.

- •Задания для практического занятия и инструктаж по их выполнению

- •Выполнить практические задания по данной теме и оформить отчет по образцу: Теоретические сведения

- •Цель работы.

- •Задание.

- •Практическое занятие №12. Тема: Диагностика и настройка производительности процессора. Работа с утилитами.

- •Задания для практического занятия и инструктаж по их выполнению

- •Выполнить практические задания по данной теме.

- •Практическое занятие №13. Тема: Тестирование основных параметров системы. Работа с утилитами

- •Теоретические сведения

- •Практическое занятие №14. Тема: Сборка основных компонентов системы. Установка драйверов устройств.

- •Задания для практического занятия и инструктаж по их выполнению

- •Записать теоретические сведения в тетрадь.

- •Выполнить практические задания по данной теме. Теоретические сведения

- •Практическое занятие №15. Тема: Установка модулей памяти.

- •Задания для практического занятия и инструктаж по их выполнению

- •Записать теоретические сведения в тетрадь.

- •Выполнить практические задания по данной теме. Теоретические сведения

- •Практическое занятие №16. Тема: Тестирование памяти и настройка параметров bios.

- •Задания для практического занятия и инструктаж по их выполнению

- •Записать теоретические сведения в тетрадь.

- •Выполнить практические задания по данной теме. Теоретические сведения

Задания для практического занятия и инструктаж по их выполнению Сумматоры

Сумматором называется узел арифметического устройства, реализующий алгебраическое суммирование чисел, представленных сигналами на его входах.

Числа в любой позиционной системе счисления складываются поразрядно, поэтому сложить любые двоичные числа можно при наличии узлов, реализующих суммирование цифр одного разряда с учетом возможного переноса из соседнего младшего разряда. К таким узлам относятся одноразрядные сумматоры на 2 и 3 входа.

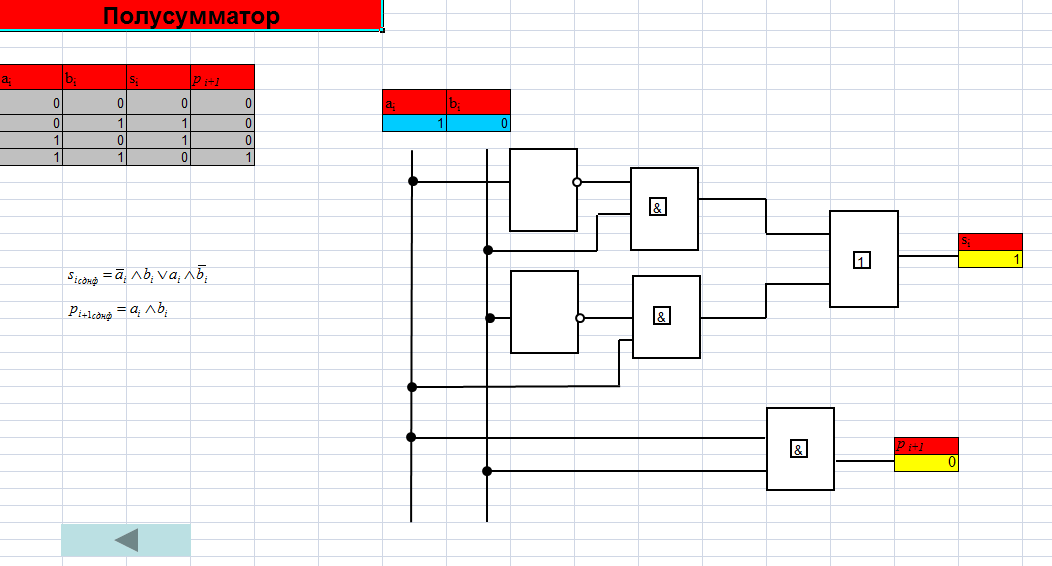

Полусумматор

Полусумматор — это логический узел, предназначенный для суммирования двух одноразрядных двоичных чисел. Он имеет 2 входа — аi и bi и 2 выхода — рi+1 и si.

рi+1 — выход переноса в следующий разряд;

si — выход суммы.

Полусумматор используется для сложения младших разрядов чисел, где отсутствует перенос из предыдущего разряда.

1. Логика работы полусумматора описывается таблицей истинности, представленной на рис. 10 (1).

2. На рис. 10(2) представлены выражения для рi+1 и si в СДНФ.

Рис. 10

3. Упрощение выражения не требуется, пункт 3 порядка проектирования логических схем отсутствует.

4. Схема имеет вид, представленный на рис. 10. Ячейки Н8 и 18 отведены для ввода суммируемых чисел. Им присвоены имена а и b соответственно.

Установлена проверка данных на корректность (ввод только 0 и 1).

Ячейка Р17 отведена для выхода si , в нее введена формула

=ЕСЛИ(ИЛИ(И(НЕ(а);b);И(НЕ(b);а))=ИСТИНА;1;0).

Ячейка Р29 отведена для выхода рi+1, в нее введена формула

=ЕСЛИ(И(а;b)=ИСТИНА; 1 ;0).

Лист защищен за исключением ячеек, в которые вводятся слагаемые.

На рис. 10 показан вариант, когда на входы схемы аi и bi поступают две единицы. При этом на выходе si получаем 0, а на выходе рi+1 — 1 соответственно.

Подавая на входы другие комбинации 0 и 1, можно увидеть, что схема действительно выполняет алгебраическое сложение одноразрядных двоичных чисел. Можно дополнительно ввести формулы для проверки сигналов на выходах любых элементов схемы.

Для большей наглядности на рабочем листе снята сетка.

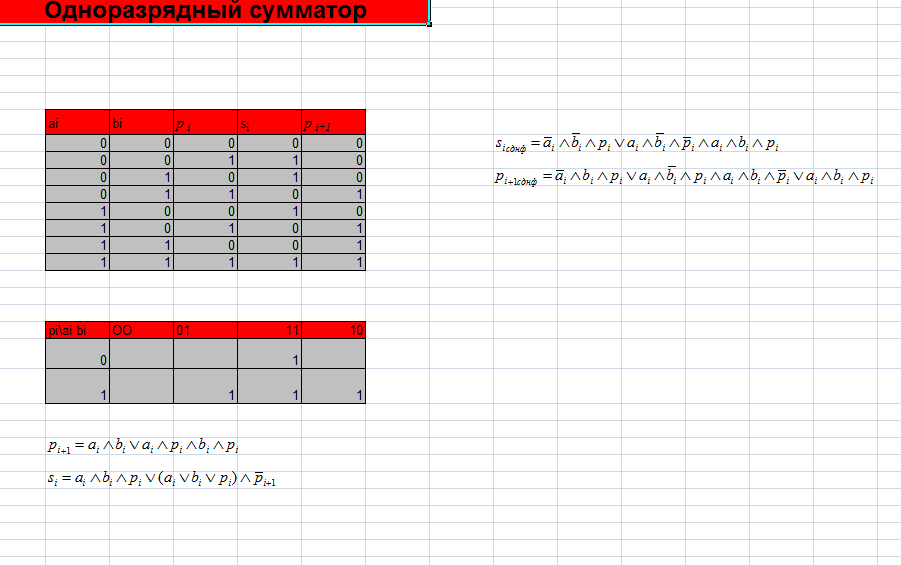

Одноразрядный сумматор

Одноразрядный комбинационный сумматор — это логический узел, предназначенный для суммирования трех одноразрядных двоичных чисел. Он имеет три входа — аi, bi и рi и два выхода — рi+1 и si.

На входы ai, bi поступают значения суммируемых цифр данного разряда, а на вход рi — значение переноса из соседнего младшего разряда.

1. Логика работы одноразрядного сумматора описывается таблицей истинности, представленной на рис. 11 (1).

Puc. 11

2. На рис. 11 (2) представлены выражения для рi+1 и si в виде СДНФ.

3. На рис. 11 (3) представлено упрощение выражения для рi+1 с помощью карт Карно. Упрощение выражения для si на листе не приводится из-за громоздкости. Оно выполнено с использованием законов алгебры логики. Упрощенное выражение для si представлено через рi+1.

4. Схема имеет вид, представленный на рис. 12 (4). Она построена на отдельном листе.

Ячейки В7 и С7 и D7 отведены для ввода суммируемых чисел. Им присвоены имена а, b и р соответственно.

Установлена проверка данных, вводимых в ячейки с именами а, b и р на корректность (ввод только 0 и 1).

Ячейка Р11 отведена для выхода рi+1, ей присвоено имя pi1, и в нее введена формула

=ЕСЛИ(ИЛИ(И(а;b);И(a;p);И(b;р))=ИСТИНА;1;0).

Ячейка Р32 отведена для выхода si, в нее введена формула

=ЕСЛИ(ИЛИ(И(а;b;р);И(НЕ(рi1);ИЛИ(а;b;р)))=ИСТИНА;1;0.

Лист защищен за исключением ячеек, в которые вводятся слагаемые.

На рис. 12 показан вариант, когда на входы схемы ai, bi и рi поступают три единицы. При этом на выходе si получаем 1 и на выходе рi+1 - 1.

Рис. 12

Подавая на входы другие комбинации 0 и 1, можно увидеть, что схема действительно выполняет алгебраическое сложение одноразрядных двоичных чисел. Можно дополнительно ввести формулы для проверки сигналов на выходах любых элементов схемы.