- •Асинхронные триггеры без разделения процессов записи и считывания.

- •Синхронные триггеры без разделения процессов записи и считывания.

- •Триггеры с разделением процессов записи и считывания.

- •Триггеры с динамическим синхровходом.

- •Асинхронные т-триггеры.

- •Преобразование вида логического функционирования триггера.

- •Регистр.

- •Классификация регистров:

- •Схемы использования регистров.

- •Счетчики.

- •Классификация счетчиков.

- •Параметры, характеризующие динамические свойства счетчиков

- •Двоичный счетчик с последовательным переносом.

- •Счетчик со сквозным переносом.

- •Счетчик с комбинированным (или групповым) переносом.

- •Реверсивные счетчики.

- •Счетчики с произвольным модулем счета (или не двоичные).

- •Способ увеличения модуля счета на 1.

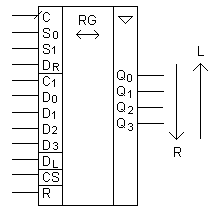

Асинхронные т-триггеры.

Все Т-триггеры могут быть реализованы лишь с внутренней задержкой.

«D» Условное графическое обозначение: «RS»

Так как в триггере с разделением процессов записи и считывания, значение меняется один раз за период (в момент перезаписи с первой ступени во вторую – в двухступенчатом, и в момент действия фронта – в динамических), то триггер сработает по Т входу всего один раз и не будет никаких колебаний.

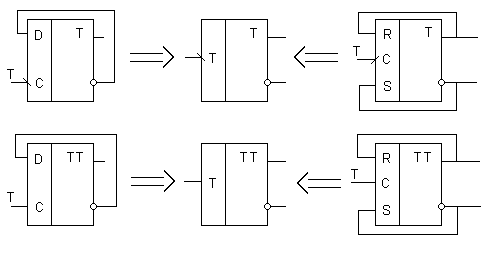

Преобразование вида логического функционирования триггера.

Из триггера типа Х надо построить триггер типа Y. Для триггера без разделения процессов записи и считывания схема имеет такой вид:

Для всех триггеров – такой:

В первом случае входной С сигнал не обязателен. С вход рассматривать как логический можно только в триггерах без разделения процессов записи и считывания.

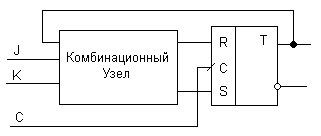

Рассмотрим на примере реализации JK триггера на основе RS. Схема будет иметь следующий вид:

Характеристическое уравнение первого триггера:

J |

K |

Q |

Q |

R |

S |

0 |

0 |

0 |

0 |

* |

0 |

0 |

0 |

1 |

1 |

0 |

* |

0 |

1 |

0 |

0 |

* |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

* |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

R: |

|

|

|

K |

|

|

|

|

Q |

|

* |

0 |

1 |

* |

J |

0 |

0 |

1 |

0 |

![]()

S: |

|

|

|

K |

|

|

|

|

Q |

|

0 |

* |

0 |

0 |

J |

1 |

* |

0 |

1 |

![]()

Регистр.

Регистр – последовательный узел, осуществляющий прием, хранение и выдачу информации.

Основные микрооперации, реализуемые регистрами:

Начальный сброс: RG:=0

Прием

Прямой код: RG:=x

Обратный код: RG:= ┐x

Хранение: RG:=RG

Выдача

Прямой код: Y:=RG

Обратный код: Y:= ┐RG

Сдвиг содержимого регистра

Вправо на один разряд: RG:=R1(RG)

Влево на один разряд: RG:=L1(RG)

Поразрядные логические операции.

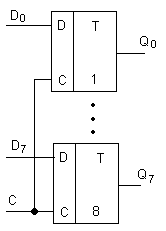

Классификация регистров:

По способу записи:

Параллельные, статические (запись осуществляется во все разряды одновременно)

Последовательные, сдвигающие (запись осуществляется последовательно по 1 разряду, при каждой записи содержимое регистра сдвигается на 1 разряд)

Последовательно-параллельные (имеют оба способа записи)

По способу выдачи информации:

Однофазные (выдается только прямое значение разряда - Q)

Парафазные (каждый разряд выдается двумя битами – Q и )

По способу начальной установки (сбросу):

С асинхронной установкой

Со сбросом по синхросигналу

По отношению к операции сдвига:

Не имеющие данной операции

Сдвигающие только вправо

Сдвигающие только влево

Реверсивные (сдвигающие и вправо и влево)

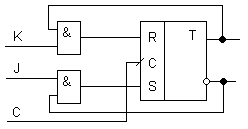

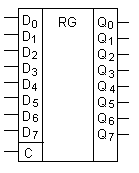

Условное графическое обозначение:

D0-D3 – разряды входного параллельного кода.

Q0-Q3 – разряды выхода (разряды с тремя состояниями).

C1 – синхросигнал приема параллельного кода.

CS – переход выхода в третье состояние

CS= {0 – Q в z состояние}

R – Асинхронный вход сброса регистра.

S0, S1 – входы задания микроопераций

S0 |

S1 |

Микрооперация |

0 |

0 |

Хранение |

0 |

1 |

Сдвиг вправо |

1 |

0 |

Сдвиг влево |

1 |

1 |

Прием параллельного кода |

C – Синхросигнал выполнения микроопераций, заданных S0 и S1.

DR, DL – последовательные входы при сдвиге вправо и влево соответственно.

– означает, что регистр реверсивный.

– регистр, сдвигающий вправо.

– регистр, сдвигающий влево.

Регистр – защелка.

Условное графическое обозначение:

Данный регистр имеет максимальное быстродействие из всех известных регистров. Регистр не имеет внутренней задержки, а, следовательно, в схемах с обратной связью (автоматах) его использовать нельзя.

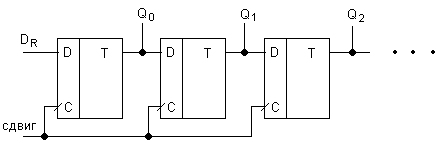

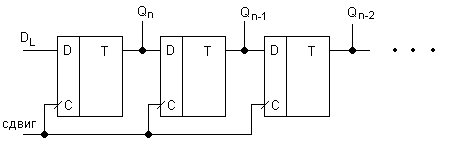

Сдвигающие регистры.

В сдвигающем регистре триггеры должны быть с разделением процесса записи и считывания, в противном случае сигнал на входе DR при появлении синхроимпульса запишется во все разряды одновременно.

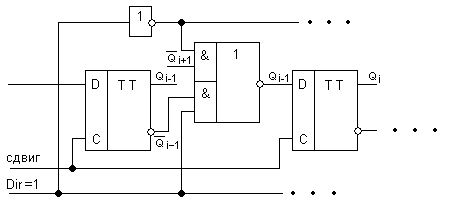

Реверсивные сдвигающие регистры.

![]()

Если

Dir

=1, то блокируется 0 с выхода инвертора

верхнего элемента “И” из “И-ИЛИ-НЕ”.

1 на нижних элементах “И” пропускает

![]() на вход D триггера

на вход D триггера

![]() ,

инвертируя его значение. Получаем, что

заведен на вход D,

а это схема регистра сдвигающего вправо.

,

инвертируя его значение. Получаем, что

заведен на вход D,

а это схема регистра сдвигающего вправо.

Если

же Dir=0 – блокируются нижние элементы

“И”, и на вход D поступает

![]() .

Получаем регистр сдвигающий влево.

.

Получаем регистр сдвигающий влево.

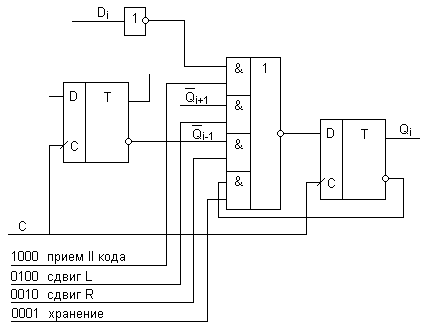

Много функциональный регистр.

Каждый элемент “И” из группы “И-ИЛИ-НЕ” обеспечивает выполнение одной микрооперации, по этому один элемент “И” функционирует, а остальные блокируются, т.е. код задающий функцию содержит одну 1. Если 1 в старшем разряде, то функционирует верхний элемент “И”, сигнал с входа Di поступает на вход D триггера Di и по синхроимпульсу его значение заносится в триггер. У каждого разряда свой вход D, таким образом, осуществляется прием параллельного входа. Второй и третий элементы “И” осуществляют сдвиг влево и вправо аналогично предыдущей схеме. Режим хранения обеспечивает четвертый элемент “И”, здесь он реализован путем записи в триггер собственного значения.