Упражнение № 9

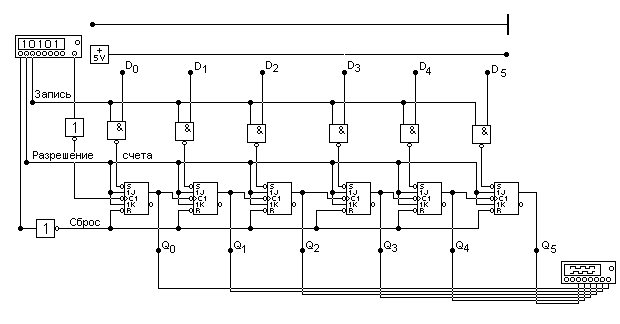

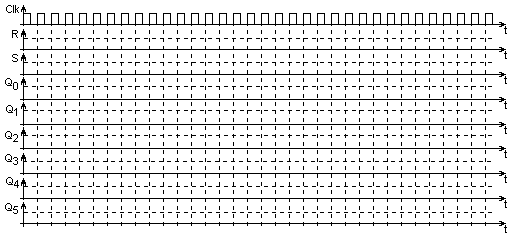

Собрать схему шестиразрядного двоичного счетчика на JK-триггерах (рис.9) и зарисовать временные диаграммы (рис. 10), поясняющие принцип его работы. На первом этапе счет производить с нуля, на втором - со стартового числа D=А, записываемого в нулевом такте.

Рис. 9 Двоичный счетчик |

Рис. 10 Временные диаграммы двоичного счетчика |

Упражнение № 10

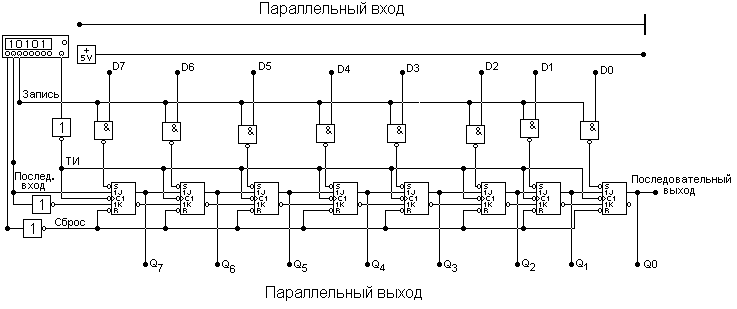

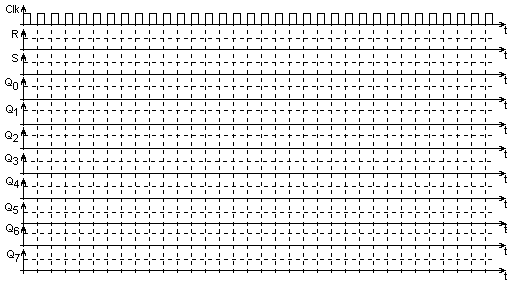

Собрать схему универсального сдвигового регистра на JK-триггерах (рис.11) и зарисовать временные диаграммы, поясняющие принцип его работы в качестве последовательно-параллельного регистра (рис. 12) и в качестве параллельно-последовательного регистра (рис. 13). Преобразования выполнить с числом D=А. Числа А приведены в Приложении 1.

Рис. 11 Универсальный сдвиговый регистр |

Рис. 12 Временные диаграммы последовательно-параллельного сдвигового регистра |

Для ввода данных в параллельном коде использовать источник напряжения постоянного тока и заземление.

Примечание: на временных диаграммах R означает сброс, S – запись, Clk – тактовые импульсы, D – входные данные, Q – выходные данные.

Рис. 13 Временные диаграммы параллельно-последовательного сдвигового регистра |

Упражнение № 11

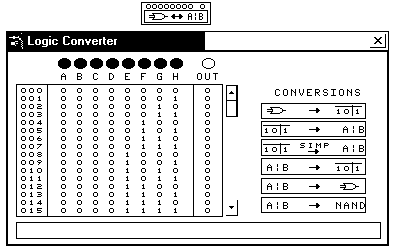

Синтезировать схему цифрового устройства с помощью Logic Converter (рис.14). Варианты заданий приведены в Приложении 2.

Рис. 14 Логический конвертор |

Здесь записать минимизированное булево выражение синтезируемого устройства |

Упражнение выполнить в следующей последовательности:

В колонке “OUT” логического конвертора установить значение “ИСТИНА” для соответствующих заданию минтермов;

Получить аналитическую форму описания синтезируемого устройства;

Минимизировать полученное булево выражение;

Синтезировать логическую схему устройства;

Решить обратную задачу – определить таблицу истинности и булево выражения для синтезированного устройства, подключив его к конвертору.

Примечание: все этапы выполняются с помощью логического конвертора.

Приложение 1

№ варианта |

A10 |

B10 |

№ варианта |

A10 |

B10 |

1 |

24 |

46 |

19 |

23 |

45 |

2 |

25 |

45 |

20 |

44 |

66 |

3 |

26 |

48 |

21 |

45 |

67 |

4 |

27 |

35 |

22 |

46 |

68 |

5 |

28 |

36 |

23 |

47 |

69 |

6 |

29 |

37 |

24 |

48 |

70 |

7 |

30 |

38 |

25 |

49 |

71 |

8 |

31 |

39 |

26 |

50 |

72 |

9 |

33 |

40 |

27 |

51 |

73 |

10 |

34 |

41 |

28 |

52 |

74 |

11 |

35 |

42 |

29 |

53 |

75 |

12 |

36 |

43 |

30 |

54 |

76 |

13 |

37 |

44 |

31 |

55 |

77 |

14 |

38 |

45 |

32 |

56 |

78 |

15 |

39 |

46 |

33 |

58 |

79 |

16 |

40 |

47 |

34 |

59 |

80 |

17 |

41 |

48 |

35 |

60 |

81 |

18 |

42 |

49 |

36 |

61 |

82 |

Приложение 2

-

№

варианта

Логическая функция в ДСНФ

1

M0+M1+M4+M5+M8+M9+M12+M13

2

M0+M1+M2+M3+M4+M5+M6+M7

3

M1+M3+M5+M7+M9+M11+M13+M15

4

M0+M2+M4+M6+M8+M10+M12+M14

5

M4+M5+M6+M7+M8+M9+M10+M11

6

M8+M9+M10+M11+M12+M13+M14+M15

7

M0+M1+M2+M3+M8+M9+M10+M11

8

M0+M1+M2+M3+M12+M13+M14+M15

9

M12+M13+M14+M15+M16+M17+M18+M19

10

M16+M17+M18+M19+ M20+M21+M22+M23

11

M20+M21+M22+M23+M24+M25+M26+M27

12

M24+M25+M26+M27+M28+M29+M30+M31

13

M28+M29+M30+M31+M32+M33+M34+M35

14

M32+M33+M34+M35+M36+M37+M38+M39

15

M36+M37+M38+M39+M40+M41+M42+M43

16

M40+M41+M42+M43+M44+M45+M46+M47

17

M44+M45+M46+M47+M48+M49+M50+M51

18

M48+M49+M50+M51+M52+M53+M54+M55

19

M52+M53+M54+M55+M56+M57+M58+M59

20

M56+M57+M58+M59+M60+M61+M62+M63

21

M60+M61+M62+M63+M64+M65+M66+M67

22

M64+M65+M66+M67+M68+M69+M70+M71

23

M68+M69+M70+M71+M72+M73+M74+M75

24

M72+M73+M74+M75+M76+M77+M78+M79

25

M76+M77+M78+M79+M80+M81+M82+M83

26

M80+M81+M82+M83+M84+M85+M86+M87

27

M84+M85+M86+M87+M88+M89+M90+M91

28

M88+M89+M90+M91+M92+M93+M94+M95

29

M92+M93+M94+M95+M96+M97+M98+M99

30

M96+M97+M98+M99+M100+M101+M102+M103

31

M100+M101+M102+M103+M104+M105+M106+M107

32

M104+M105+M106+M107+M108+M109+M110+M111

33

M108+M109+M110+M111+M112+M113+M114+M115

34

M112+M113+M114+M115+M116+M117+M118+M119

35

M116+M117+M118+M119+M120+M121+M122+M123

36

M120+M121+M122+M123+M124+M125+M126+M127