- •Тема 7. Комбинационные цифровые устройства

- •Синтез комбинационных цифровых устройств

- •Типовые комбинационные цифровые устройства.

- •Мультиплексоры и демультиплексоры

- •Шифраторы (кодеры) и дешифраторы (декодеры)

- •Аналоговый коммутатор с цифровым управлением

- •Мультиплексоры — демультиплексоры

- •Преобразователи кодов

- •Цифровые компараторы (компараторы кодов)

- •Сумматоры

Преобразователи кодов

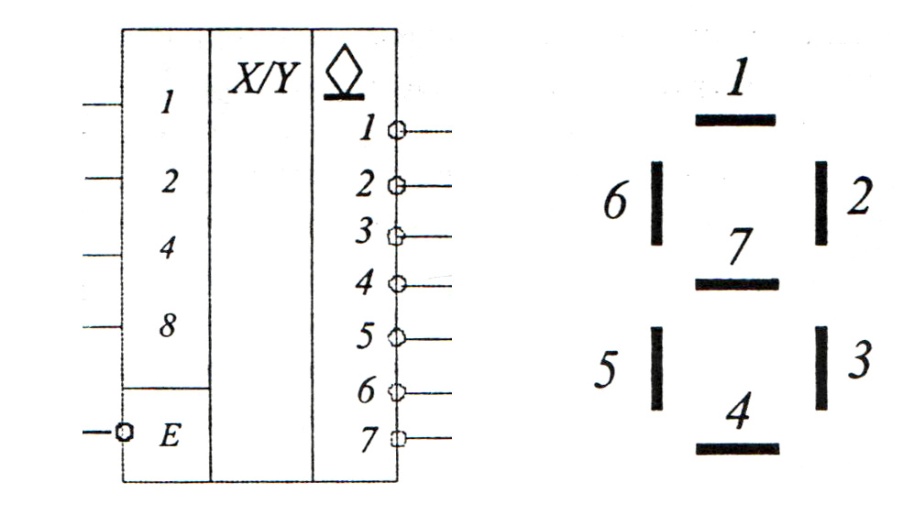

Преобразователи кодов служат для преобразования входных двоичных кодов в выходные двоично— десятичные и наоборот. Находят применение в схемах многоразрядной десятичной индикации. На схемах обозначаются буквами X/Y. Например, микросхема к155пп5 представляет преобразователь двоично-десятичного кода, в код семисегментного индексатора:

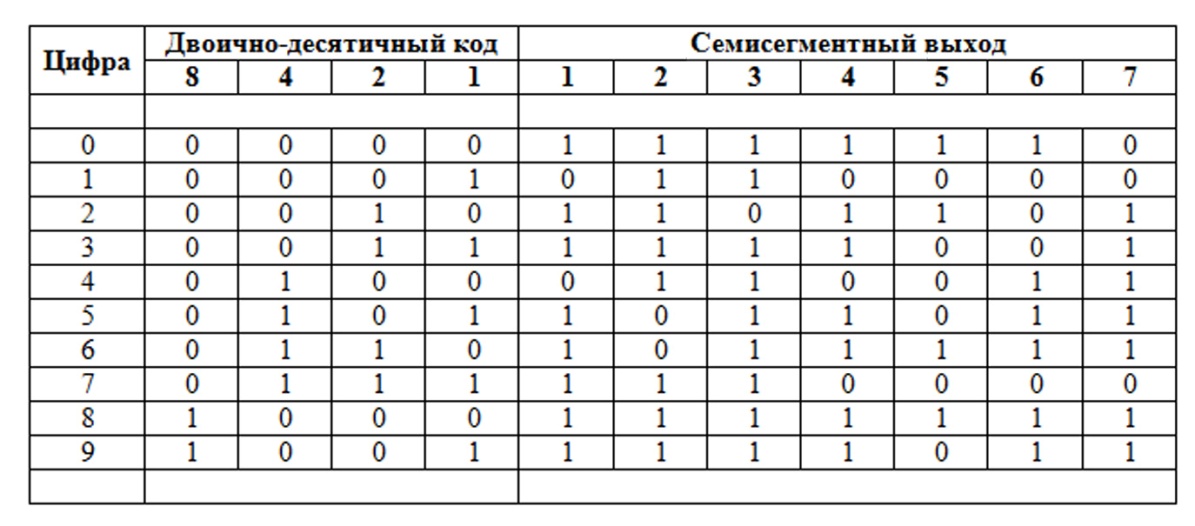

1, 2, 4, 8 — информационные входы. 1, 2, 3, 4, 5, 6, 7 — выходы для управления светодиодной матрицей (показана справа) Вход Е используется либо для осуществления индикации (подачей на него логического 0), либо для гашения индикатора (подачей на него логической 1). Микросхема имеет выход ОК. Работа преобразователя осуществляется в соответствии с таблицей истинности:

Сегмент светится, если на него подаётся логическая 1.

Цифровые компараторы (компараторы кодов)

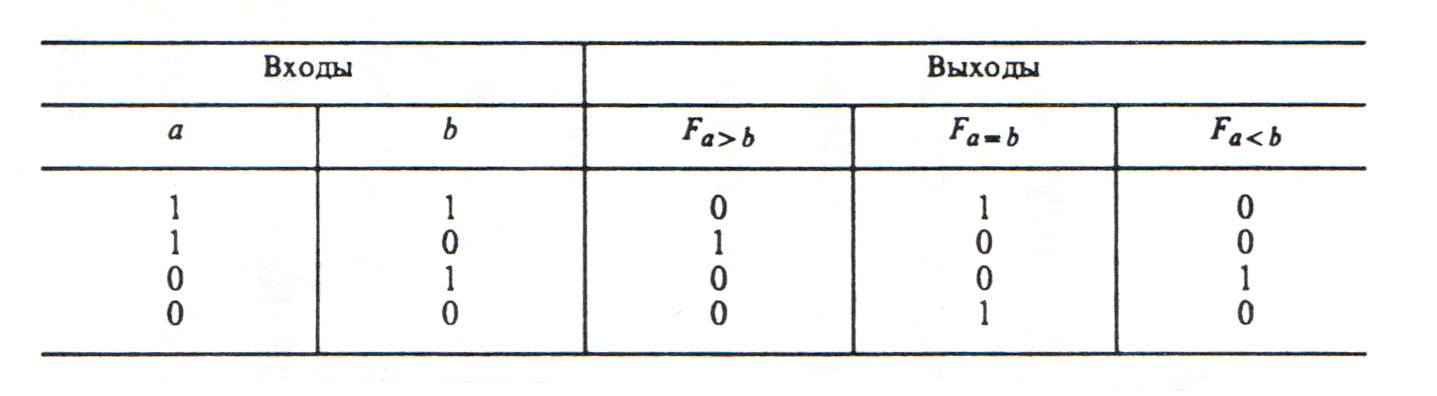

Цифровые компараторы выполняют сравнение двух чисел, заданных в двоичном коде. Они могут определять равенство двух двоичных чисел А и В с одинаковым количеством разрядов либо вид неравенства А > В или А < В. Цифровые компараторы имеют три выхода: Fa > b, Fa = b, Fa < b. Таблица истинности одноразрядного компаратора приведены ниже:

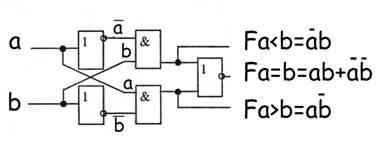

По известным правилам можно записать логические функции, характеризующие соотношение одноразрядных чисел а и в: Fa > b = а • b Fa = b = аb +ab Fa < b = ab Схема одноразрядного компаратора, реализующая приведённые функции, показана ниже:

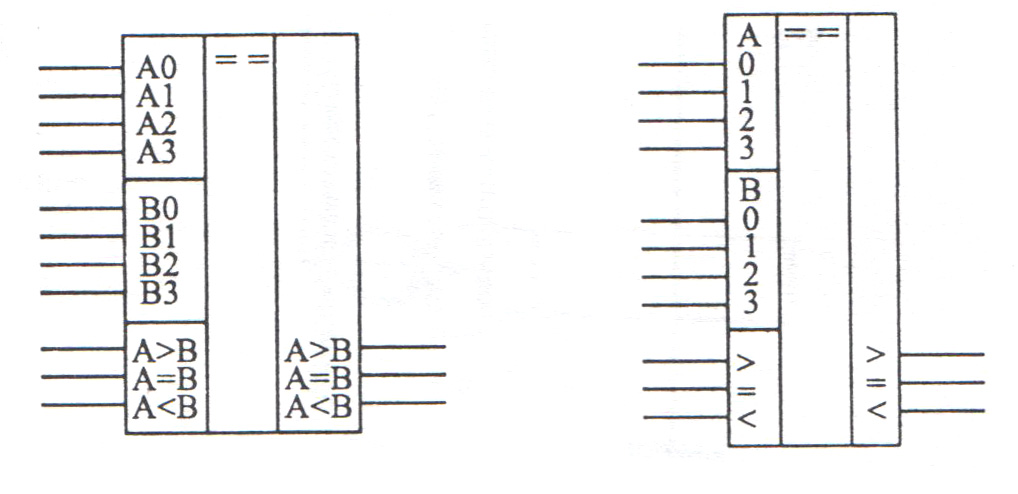

Цифровые компараторы выпускают в виде микросхем. Код микросхем в отечественных сериях — СП. На схемах компараторы кодов обозначаются символами равенства: «= =» Например, четырёхразрядный компаратор кодов имеет два варианта обозначения:

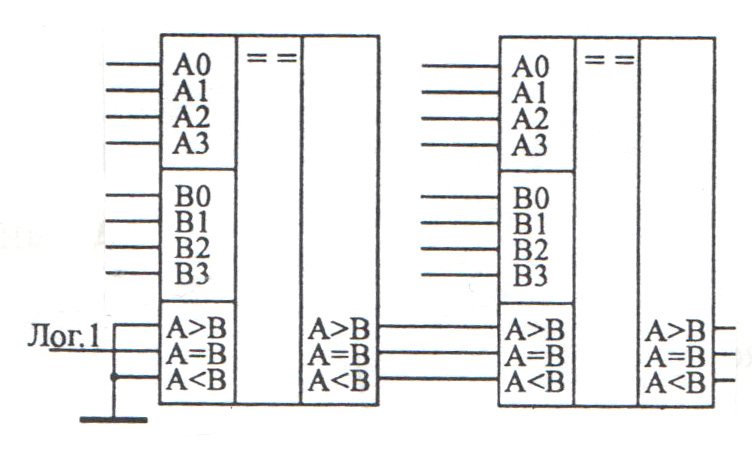

Помимо восьми входов для сравниваемых кодов (двух четырёхразрядных кодов, обозначаемых А0...A3 и В0...В3) компаратор имеет три управляющих входа для наращивания разрядности (А > В, А < В, А = В) и три выхода результирующих сигналов (А > В, А < В, А = В). Для удобства на схемах управляющие входы и выходы иногда обозначают просто «>», «<» и «=». Нулевые разряды кодов (А0 и В0) — младшие, третьи разряды (А3 и В3) — старшие. Если используется одиночная микросхема, то для её правильной работы достаточно подать единицу на вход А = В, а состояния входов А < В и А > В не важны: на них можно подать как нуль, так и единицу. Назначение выходов понятно из их названия, а полярность выходных сигналов положительная (активный уровень — единица). Если микросхема компараторов кодов каскадируются (объединяются) для увеличения числа разрядов сравниваемых кодов, то выходные сигналы микросхемы, обрабатывающей младшие разряды кода, нужно подать на одноимённые входы микросхемы, обрабатывающей старшие разряды кода:

Сумматоры

Сумматоры — это комбинационные устройства, предназначенные для сложения двух входных двоичных кодов. Например, арифметическая сумма кодов 0111 (число 7) и 0101 (число 5) равна 1100 (число 12). Арифметическая сумма кодов 1101 (число 13) и 0110 (число 6) равна 10011 (число 19), т. е. сумма двух двоичных чисел с числом разрядов n может иметь результат с числом разрядов n + 1. Этот дополнительный (старший) разряд называется выходом переноса (Р). На схемах сумматоры обозначаются буквами SM. Микросхемы сумматоров кодируются буквами ИМ. Рассмотрим таблицу истинности сложения двух одноразрядных двоичных чисел без учёта переноса:

A |

B |

S |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

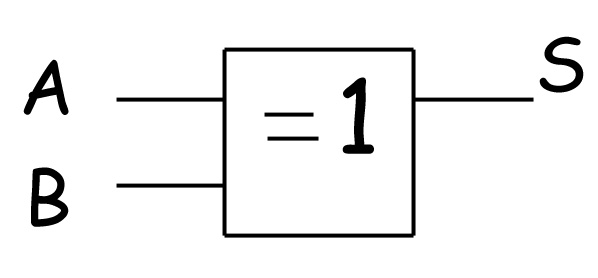

Запишем логическую функцию: S =AB+AB Устройство, реализующее эту функцию, называется " исключающее ИЛИ":

Схема не информирует о бите переноса. Рассмотрим сложение двух одноразрядных двоичных чисел, для чего составим таблицу сложения (таблицу истинности), в которой отразим значение входных чисел А и В, значение результата суммирования S и значения переноса в старший разряд Р:

A |

B |

P |

S |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

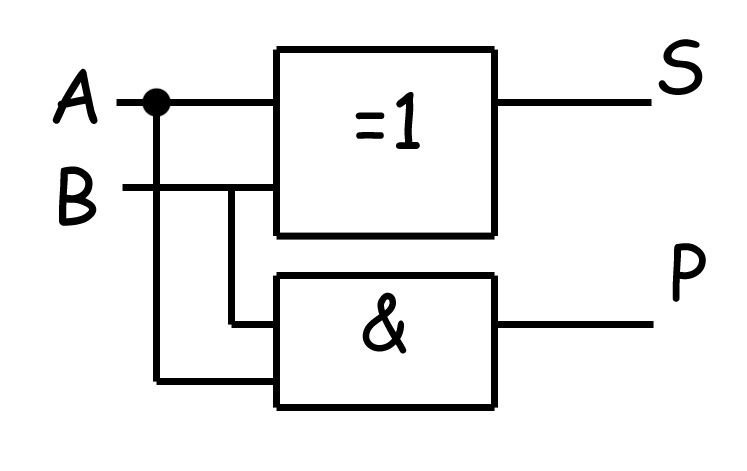

Работа устройства, реализующего таблицу истинности, описывается следующими уравнениями: S = AB+AB и Р = АВ Устройство, реализующего таблицу истинности, содержит " исключающие ИЛИ" и конъюнктор " И"

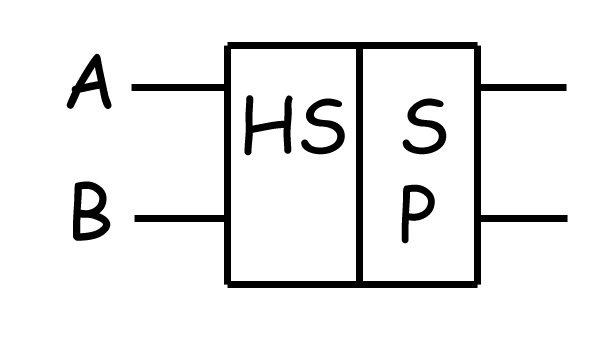

Это устройство называется полусумматором и изображается в виде:

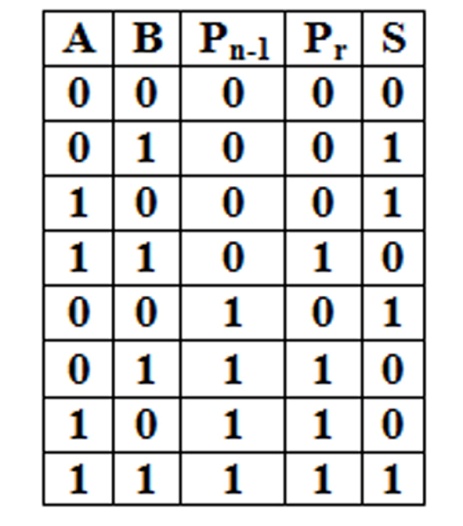

Устройства называются полусумматором, т. к. имеет только два входа и не воспринимается сигнал переноса от других микросхем. Он используется только в младшем разряде. Рассмотрим сложение двух одноразрядных двоичных чисел с учётом бита переноса от других микросхем:

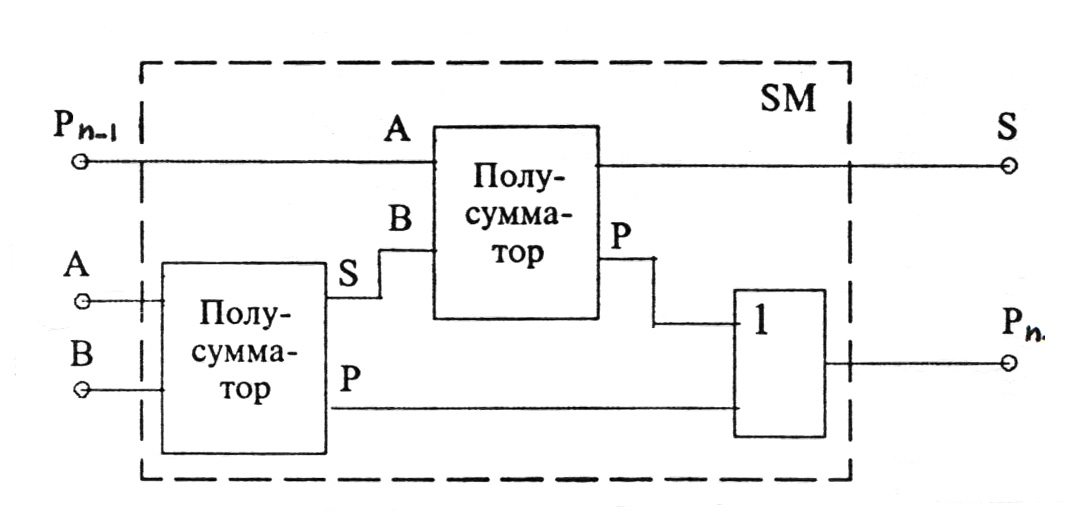

Работа устройства, реализующего таблицу истинности, описывается следующими уравнениями: S=ABPn-1+ABPn-1+ABPn-1+ABPn-1 Pn=ABPn-1+ABPn-1+ABPn-1+ABPn-1 Устройство, реализующие таблицу, содержит два полусумматора и дизъюнктор " ИЛИ":

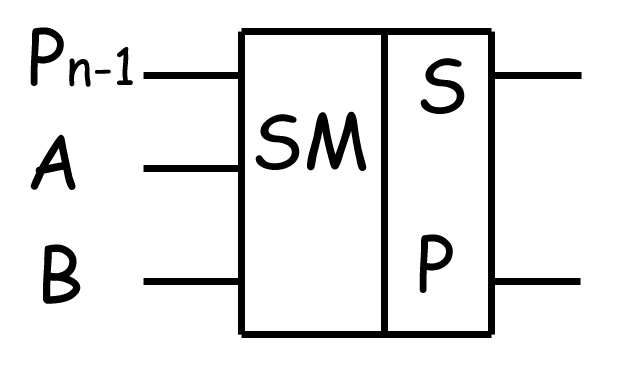

Это устройство называется одноразрядным сумматором и имеет следующее условное графическое обозначение:

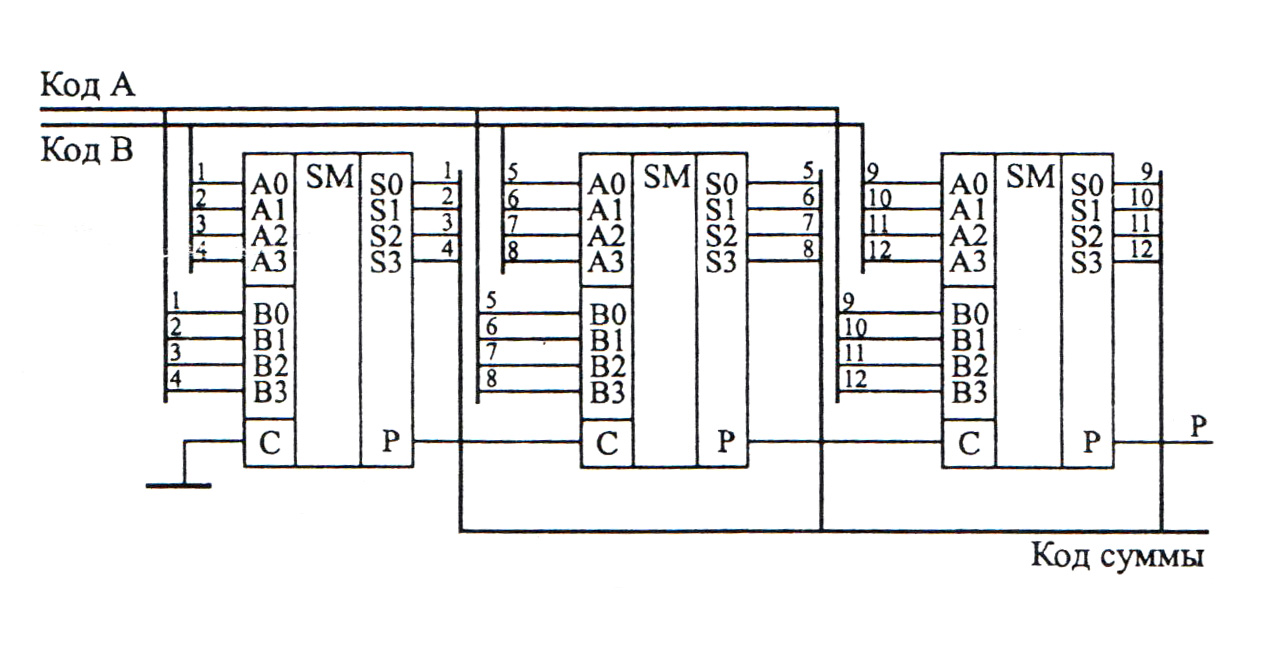

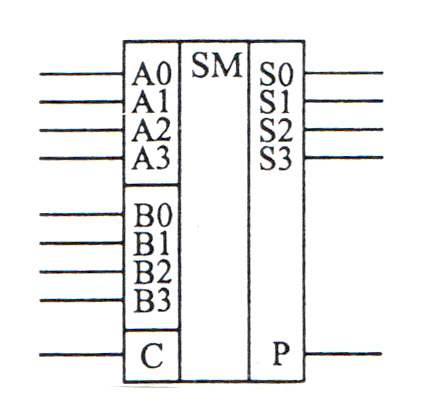

Сумматоры бывают одноразрядные (для суммирования двух одноразрядных чисел) двухразрядные (суммируют двухразрядные числа) и четырёхразрядные (суммируют четырёхразрядные числа). Чаще всего применяют 4 — х разрядные:

Вход С (вход расширения) для объединения нескольких сумматоров с целью увеличения разрядности: