МІНІСТЕРСТВО ОСВІТИ І НАУКИ УКРАЇНИ

НАЦІОНАЛЬНИЙ УНІВЕРСИТЕТ «ЛЬВІВСЬКА ПОЛІТЕХНІКА»

Кафедра САПР

Лабораторна робота №5

з дисципліни «Комп’ютерна схемотехніка та архітектура комп’ютерів»

на тему: «Принципи роботи регістрових пристроїв»

Варіант 76

Виконала

Студентка

Групи КН-26

Суровцева А.В.

Прийняв

Асистент кафедри САПР

Головацький Р.І.

Львів 2013

Тема: Принципи роботи регістрових пристроїв

Мета: Вивчити призначення, принципи роботи та будови різних тригерних регістрів. Набути практичних навиків при дослідженні роботи регістрових пристроїв з бібліотеки EWB.

Теоретичні відомості

Регістри - пристрої для тимчасового зберігання й перетворення інформації у вигляді багато розрядних двійкових чисел. При порівняльній простоті регістри мають більші функціональні можливості. Вони використаються в якості керуючих і запам'ятовувальних пристроїв, генераторів і перетворювачів кодів, лічильників, дільників частоти, вузлів тимчасової затримки.

Для запам'ятовування окремих розрядів числа можуть застосовуватися тригери різних типів. Елементами структури регістрів є тригери D- або JK- типу з динамічним або статичним керуванням.

Одиночний тригер може запам'ятовувати (реєструвати) один розряд (біт) двійкової інформації. Тому, одиночний тригер можна вважати однорозрядним регістром.

Занесення інформації в регістр називається операцією запису або введення. Запис інформації в регістр не вимагає його попереднього обнуління.

Операція видачі інформації з регістра – зчитування або вивід.

Класифікація регістрів:

1) по способу занесення/видачі інформації:

- паралельні (регістри зберігання) - інформація вводиться й виводиться одночасно по всіх розрядах;

- послідовні (регістри зсуву) - інформація біт за бітом «просувається» через регістр і виводиться послідовно також. По напрямку передачі послідовні регістри зсуву інформації бувають односпрямовані або реверсивні;

- комбіновані (послідовно-паралельні регістри) - паралельне введення й послідовний вивід (і навпаки).

Таблиця 1.

M1 |

M2 |

Вид приймання інф. |

Вид видачі інф. |

0 |

0 |

Паралельний |

Паралельний |

0 |

1 |

Паралельний |

Послідовний |

1 |

0 |

Послідовний |

Паралельный |

1 |

1 |

Послідовний |

Послідовний |

Рисунок

2.1 Умовне позначення регістра.

Рисунок

2.1 Умовне позначення регістра.

2) по способу представлення інформації:

- однофазні (інформація представляється в прямому або інверсному виді);

- парафазні (інформація представляється й у прямому, і у інверсному виді).

2.1 Паралельні регістри

Паралельні регістри здійснюють запис і вивід інформації в паралельному коді, а це значить, що для передачі кожного розряду використається окрема лінія.

Для запису інформації в регістр на його входи (D0-D3) потрібно встановити відповідні логічні рівні, після чого подати імпульс на вхід синхронізації (C). Після цього на виходах Q0-Q3 з'явиться записане слово. Регістри запам'ятовують вхідні сигнали тільки в момент часу, обумовлений сигналом синхронізації.

Рисунок 2.2 – Умовно-графічне позначення паралельного регістра

Рисунок 2.3 – Схема паралельного регістра

Дозвіл С Скид Дозвіл Дозвіл

Рисунок 2.4 – Схема паралельного регістра на RS-тригері

2.2 Послідовні регістри (регістри зсуву)

Послідовний регістр (регістр зсуву) звичайно служить для перетворення послідовного коду в паралельний і навпаки. Застосування послідовного коду пов'язане з необхідністю передачі великої кількості двійкової інформації з обмеженої кількості з'єднувальних ліній. При паралельній передачі розрядів потрібно велику кількість з'єднувальних провідників. Якщо двійкові розряди послідовно біт за бітом передавати по одному провіднику, то можна значно скоротити розміри з'єднувальних ліній на платі (і розміри корпусів мікросхем).

Принципова схема послідовного регістра, зібраного на основі D-тригерів і що дозволяє здійснити перетворення послідовного коду в паралельний, наведена на Рисунку 2.4.

Рисунок 2.4. Схема послідовного регістра.

Розглянемо роботу цього регістра. Крім паралельного з'єднання тригерів для побудови регістрів використаються послідовне з'єднання цих елементів. Можна припустити, що на початку всі тригери регістра перебувають у стані логічного нуля, тобто Q0=0, Q1=0, Q2=0, Q3=0. Якщо на вході D-тригера Т1 має місце логічний 0, то надходження синхроімпульсів на входи «С» тригерів не міняє їхні стани.

Відповідно рисунку 2.4, синхроімпульси «С» надходять на відповідні входи всіх тригерів регістра одночасно й записують у них те, що має місце на їхніх інформаційних входах. На інформаційних входах тригерів Т2, Т3, Т4 - рівні логічного «0», тому що інформаційні входи наступних тригерів з'єднані з виходами попередніх тригерів, що перебувають у стані логічного «0», а на вхід «D» першого тригера, подається «0» із зовнішнього джерела інформації. При подачі на вхід «D» першого тригера «1», із приходом першого синхроімпульсу, у цей тригер запишеться «1», а в інші тригери - «0», тому що до моменту надходження фронту синхроімпульсу на виході тригера Т1 ще був присутній логічний «0». Таким чином, у тригер Т1 записується та інформація (той біт), що була на його вході «D у момент надходження фронту синхроімпульсу й т.д. При надходженні другого синхроімпульсу логічна «1» з виходу першого тригера, запишеться в другий тригер Т2, і в результаті відбувається зсув спочатку записаної «1» з тригера Т1 у тригер Т2, із тригера Т2 у тригер Т3 і т.д. Таким чином, виробляється послідовне зсув поданої на вхід регістра інформації (у послідовному коді) на один розряд вправо в кожному такті синхроімпульсів. Після надходження чотирьох синхроімпульсів регістр виявляється повністю заповненим розрядами числа, що входить через послідовне введення на «D0». Протягом наступних чотирьох синхроімпульсів виконується послідовний порозрядний вивід з регістра записаного числа, після чого регістр буде повністю очищеним (за умови подачі на його вхід рівня «0» у режимі виводу записаного числа).

Рисунок 2.5. Часові діаграми роботи регістра зсуву.

Рисунок 2.6. Схема регістра зсуву на D-тригера

Таблиця 2 роботи регістра зсуву на D-тригерах.

Таблиця 2

№. |

Qm-1 |

Qm-2 |

Qm-3 |

... |

Q1 |

Q0 |

1 |

A0 |

* |

* |

|

* |

* |

2 |

A1 |

A0 |

* |

|

* |

* |

3 |

A2 |

A1 |

A0 |

|

|

|

|

|

|

|

|

|

|

m |

Am-1 |

Am-2 |

Am-3 |

|

A1 |

A0 |

m+1 |

* |

Am-1 |

Am-2 |

|

A2 |

A1 |

m+2 |

* |

* |

Am-1 |

|

A3 |

A2 |

|

|

|

|

|

|

|

2m |

* |

* |

* |

|

* |

* |

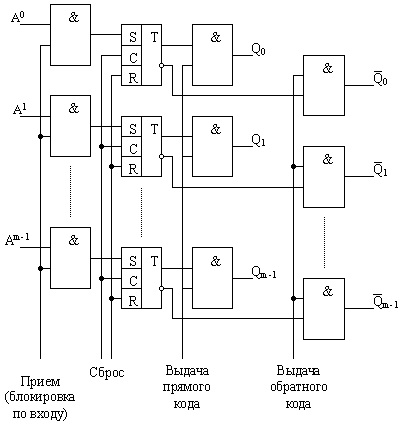

Реалізація

регистра зсуву на однотактних RS триггерах

з парафазними бітами на вході:

Реалізація

регистра зсуву на однотактних RS триггерах

з парафазними бітами на вході:

Рисунок 2.7. Схема регістра зсуву на RS –тригерах.

В класичних регістрах зсуву використовуються двухтактні тригери.

Рисунок 2.7. Схема регістра зсуву на двухтактних D тригерах.