- •II. Pamięci

- •Pojedyncza I sieć jednostek pamięci (o wielu wejściach) zbudowanych na bramkach or

- •Komórka pamięci o pojemności 1 bit, po lewej sram, po prawej dram

- •Porównanie parametrów urządzeń pamięci

- •Struktura logiczna 1-bitowej komórki pamięci

- •Schemat (I symbol) fizycznej jednostki pamięci I jej łączy z zewnętrzem

- •Tablica wartości modułu sterującego pamięci

- •Przykład adresów I zawartości sześciu spośród 210 słów pamięci

- •Dekodowanie I demultipleksowanie adresów na kości dram 64k

- •Schemat logiczny pamięci rom

- •Struktura logiczna pamięci rom 25×8

- •Tabela wartości dekodera

- •Komórka pamięci rom – (Metal Oxide Semiconductor)

- •Typowa organizacja pamięci podręcznej

- •Przykład odwzorowania bloków pamięci ram na linie pamięci podręcznej

Komórka pamięci rom – (Metal Oxide Semiconductor)

Fizyczne realizacje programowania pamięci ROM są rózne. Najprostsza to ustawienie pożądanych połączeń już w trakcie produkcji jednostki pamięci. Stosuje się ją przy masowej produkcji identycznych kości. Metoda jest nieopłacalna gdy zamówienie opiewa na niewielką liczbę egzemplarzy. Dla takich nabywców korzystniej jest produkować programowalne jednostki ROM (PROM). Tego typu pamięci mają fabrycznie zamknięte wszystkie przełączniki przewodnikiem wytrzymującym niskie natężenia prądu elektrycznego. Następnie do połączeń, których stan ma być ‘otwarte’ przykłada się krótki impuls wyższego napięcia, wówczas przepływający przez nie prąd o wyższym natężeniu niż normalne roztapia je. Na tej zasadzie działają bezpieczniki starego typu instalowane na wejściu do domowej instalacji elektrycznej. Programowanie takie jest nieodwracalne. Jego zaletą jest możliwość zaprogramowania kości we własnym zakresie gdyż na rynku dostępne są programatory pamięci PROM. Oczywiście trzeba uprzednio zaprojektować sieć połączeń w podobny sposób jak w powyższym przykładzie.

Inny typ ROM to E(rasable)PROM, w których można doprowadzić do usunięcia wszystkich połączeń przez naświetlenie promieniowanie UV lub za pomocą odpowiedniego sygnału elektrycznego E(ectricall)EPROM. Resetowanie pamięci EEPROM można dokonać bez wyjmowania jej z gniazda. Pamięć doprowadzoną do stanu pierwotnego mżna zaprogramować zgodnie z inną niż poprzedia tabelą wartości.

Pamięci flash to w zasadzie są pamięci EEPROM z dodatkowym układem elektronicznym pozwalającym na selektywne resetowanie wybranych bloków pamięci.

Zastosowania pamięci ROM: mikroprogramowanie, biblioteki programów zawierające często używane funkcje, programy uruchomieniowe pamięci ROM, tablice funkcji matematycznych.

Pamięć podręczna (cache memory) (kieszenie)

(ew. wykorzystać rozdział 7 w Computer)

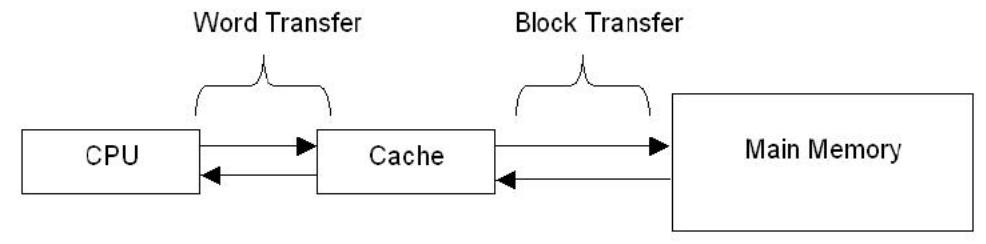

Łatwiej znaleźć książkę w stosie leżącym na biurku niż w bibliotecznej szafie. Podobnie jest z informacją zapisaną w pamięci RAM. Pamięć podręczna (cash) pełni rolę stosu na biurku. Jest fizycznie umieszczona w procesorze lub/i między rejestrami procesora a pamięcią RAM, przechowuje czasowo kopie niewielkiej części informacji zawartej w RAM. Ma niewielką pojemność ale za to krótki czas dostępu. Jeżeli procesor próbuje odczytać słowo z pamięci wpierw sprawdza czy przypadkiem nie znajduje się ono w pamięci podręcznej. Jeżeli tak to je pobiera. Jeżeli nie, to odczytywany jest blok pamięci RAM zawierający ustaloną liczbę słów (w tym poszukiwane słowo), dostarczany do pamięci podręcznej a stąd do procesora.

Analiza statystyczna pracy procesora wskazuje na znaczne prawdopodobieństwo, tego że w przyszłości procesor będzie poszukiwał słowa z tego samego bloku, z który ostatnio pobrał.

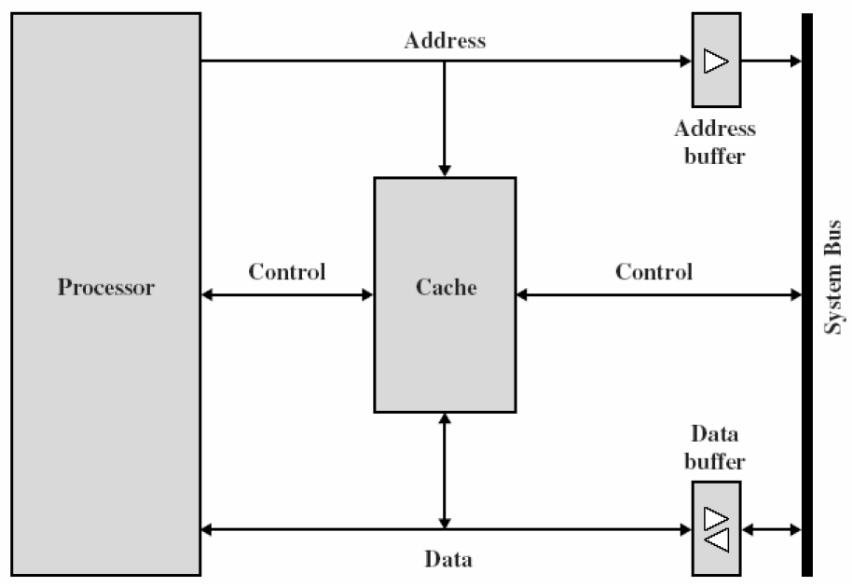

Typowa organizacja pamięci podręcznej

Pamięć podręczna powinna mieć małą pojemność ale być szybka.Im mniejsza pamięć tym krótszy czas dostępu. Sprawność pamięci podręcznej charakteryzuje sumaryczny parametr o nazwie iloraz trafień (Hit Ratio), zdefiowany jako iloraz liczby słów znalezionych przez procesor w cache do całkowitej liczby prób. Uważa się, że pamięć cache jest dobrze zorganizowana i przydatna jeżeli HR > 0.9. Liczba linii pamięci podręcznej jest znacznie mniejsza niż liczba bloków pamięci RAM. Potrzebny jest zatem jakiś alorytm odzorowujący bloki RAM na linie cache oraz reguła określająca, którą linię pamięci podręcznej zajmie nowo wprowadzany blok pamięci głównej. Wybór algorytmu i reguły decydują o organizacji pamięci cache. W użyciu jest kilka wzorów organizacji.

Odwzorowanie bezpośrednie