- •Конспект лекционных занятий по дисциплине

- •«Цифровые устройства и микропроцессоры»

- •Тема лекции 1. Введение. Системы счисления. Формы представления чисел. Прямой, обратный и дополнительный код. Арифметические основы цифровых устройств.

- •Системы счисления

- •Кодирование положительных и отрицательных чисел

- •Деление двоичных чисел в прямом коде.

- •Логические основы цу.

- •Способы задания фал.

- •Конечные автоматы

- •Дешифраторы и шифраторы

- •Мультиплексоры и демультиплексоры

- •Компаратор

- •Регистры

- •Счетчики

- •Сумматоры

- •Тема лекции 10. Интерфейсы ввода и вывода. Шинная организация ibm pc. Передача информации в мпс. Методы ввода/вывода и их классификация. Последовательная передача данных.

- •Методы ввода/вывода и их классификация

- •Глоссарий

Регистры

Регистр - это типовой узел ЭВМ, который служит для запоминания и преобразования многоразрядных двоичных слов. Регистр состоит из триггеров и вспомогательных логических схем. В регистрах выполняется ряд микроопераций. К ним относятся: установка разрядов регистра в нулевое или единичное состояние; прием слова из другого устройства; выдача слов из регистра в прямом или обратном кодах; сдвиг слов в разрядной сетке влево или вправо; преобразование последовательного кода слова в параллельный и обратно. Регистры строятся на D, RS, JK-триггерах.

По способам приема и выдачи данных регистры делятся на параллельные, последовательные (сдвигающие) и последовательно-параллельные. В параллельных регистрах прием и выдача слов производится параллельно по всем разрядам. В последовательных регистрах прием и выдача разрядов слов осуществляется поразрядно. Такие регистры также называют сдвигающими. В реверсивных регистрах сдвиги осуществляются и вправо, и влево. В последовательно-параллельных регистрах имеются входы для параллельного и последовательного приема (выдачи) слов, что позволяет осуществлять преобразование последовательных кодов в параллельные и наоборот.

По количеству каналов, по которым передается одна двоичная единица, различают парафазные и однофазные регистры. В первом случае двоичные единицы передаются по двум цепям каждая, т.е. каждый разряд передается в виде прямого значения переменной Xi и ее инверсии Xi, а в однофазных - только по одной цепи (Xi или Xi).

На рис. 4.6 а показан n-разрядный параллельный регистр с парафазным приемом и передачей информации. Прием парафазных кодов чисел X осуществ-ляется с помощью управляющего сигнала у1. Микрооперации выдачи кода из регистра производятся с помощью сигналов y2 и у3. Сигнал yg выдает содержимое в прямом коде,а у3 в обратном. Условные обозначения n-разрядного регистра на функциональных и структурных схемах приведены соответственно на рис. 4.6 б и 4.6 в.

Рис.4.6. Схема паралельного регистра

Счетчики

Счетчиком называется узел ЭВМ, который служит для подсчета числа входных сигналов. Максимальное число, которое может быть представлено счетчиком, равно N=2n-1, что является емкостью счетчика, где n - разрядность счетчика.

По направлению счета счетчики бывают суммирующие, вычитающие и реверсивные. По способу организации разрядного переноса различают счетчики: с последовательным, параллельным и комбинированным переносом. По основанию систем счисления различают: двоичные, двоично-десятичные, с произвольным основанием счета.

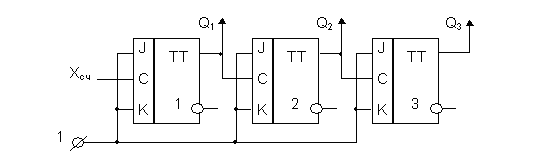

Схема З-х разрядного счетчика с последовательным переносом на JK-триггерах приведена на рис. 4.9. Триггер ТТ1 (младший разряд) при C=1 переключается по каждому сигналу Хсч. Поскольку выходы Qi соединены с C входами последующих триггеров, то сигнал Q1 является входным сигналом триггера TT2, а сигнал Q2 входным сигналом триггера ТТз. Нетрудно убедиться, что начальное состояние счетчика равно 000. После первого сигнала Хсч его состояние изменится на 001, после второго 010 и т.п. После восьмого сигнала счетчик установится снова в 000.

Рис. 4.7. Трехразрядный счетчик с последовательным переносом

Для повышения быстродействия счетчики выполняются с параллельным переносом, где длительность переходного процесса равна длительности переключения одного разряда.

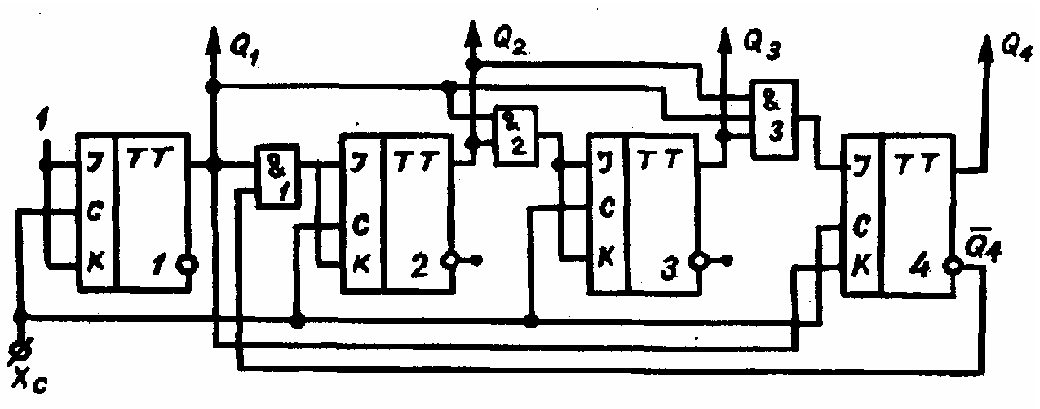

Рис. 4.8. Схема десятичного счетчика с параллельным переносом

Схема десятичного счетчика с параллельным переносом приведена на рис.4.10. После подачи 8-го импульса в счетчике устанавливается код 1000 и уровень Q4 блокирует прохождению единичного сигнала на входы триггера TT2 схемой И1. После 9-го импульса ТТ1 установится в единичное состояние, и единичный уровень с выхода Q1 подается на вход К триггера ТТ4. Десятый импульс установит ТТ1 и ТТ4 в нулевое состояние.